- 32 -

#### ●新特器件应用

# 高速串行数据通信接收芯片 CY7B933 的原理及应用

海军工程大学电子工程学院 徐勤建 刘望锁 姚直象

# Principle and Application of CY7B933 HOTLink Receiver for High Speed Serial Communication

Xu Qinjian Liu Wangsuo Yao Zhixiang

摘要:介绍了 CYPRESS 半导体公司推出的一种用于点对点之间的高速串行数据通信接收芯片 CY7B933 的原理及应用。详细说明了其管脚功能、内部组成、工作原理及工作方式。给出了一个由 CY7B933 构成的实际接收电路及设计方法。

关键词:串行数据通信; CY7B933; FIFO; IDT7200; 基带传输; 差分 PECL 输出 分类号:TN914.3 文献标识码:B 文章编号:1006-6977(2002)01-0032-03

#### 1 概述

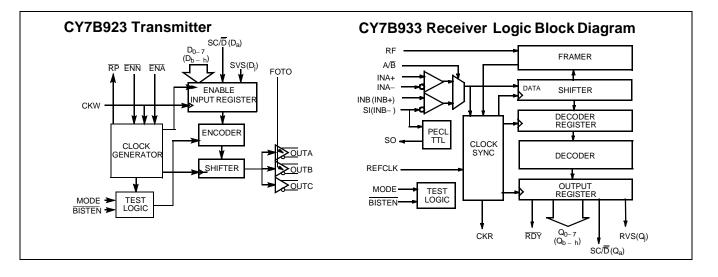

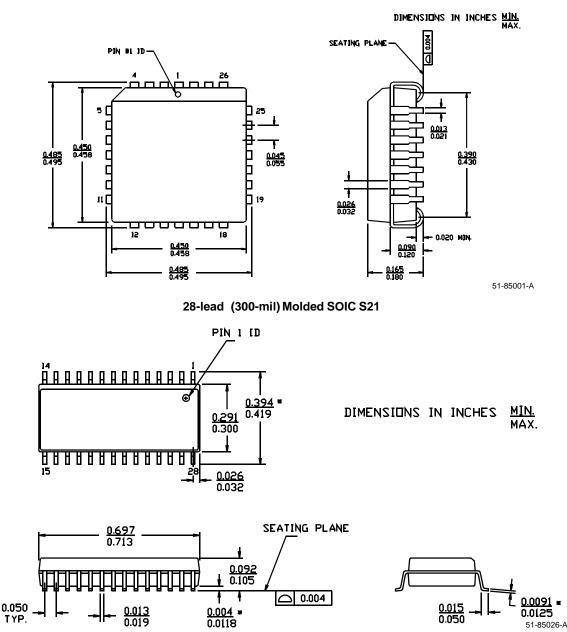

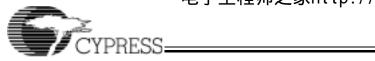

CY7B933 是 CYPRESS 半导体公司推出的一种用 于点对点之间高速串行数据通信的接收芯片。与其配 套的发送芯片为 CY7B923。CY7B933 接收芯片的内部 电路主要包括两对 PECL 串行输入接口、PECL - TTL 电平转换器、时钟同步器、成帧器、移位器、译码寄存 器、译码器、输出寄存器和测试逻辑等几部分。在与 CY7B923 配套时, CY7B933 也有三种传输速率的器件 可供选择:其中标准系列的器件有 CY7B933 - JC、 CY7B933 - JI、CY7B933 - SC和CY7B933 - MB等四种 型号, 它们的传输速率为 160~330Mbps; 高速系列的 器件有 CY7B933 - 400JC 和 CY7B933 - 400JI,其传输 速率为 160~400Mbps; 低速系列的器件有: CY7B933—155JC、CY7B933—155JI等,其传输速率为 150~160Mbps。CY7B933的封装形式有 28 脚 SOIC/ PLCC/LCC等三种,采用0.8MBiCOMS工艺生产和单 +5V 电源供电,功率为 650mW。

#### 2 引脚功能及内部结构

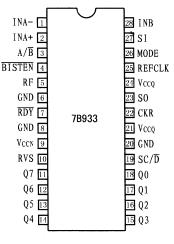

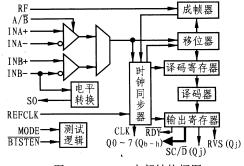

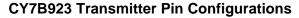

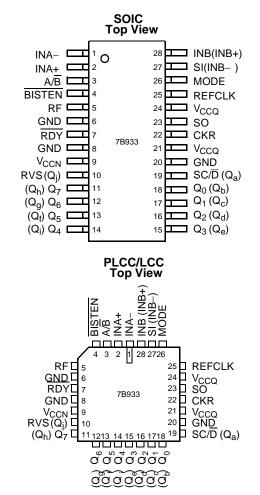

CY7B933 的引脚排列如图 1 所示 (SOIC 封装), 表 1 所列为其引脚功能说明。图 2 所示是其内部结 构框图,下面介绍各部分的主要功能。

●串行数据输入端口

CY7B933 的两对差分线接收端可作为串行数据 的输入,选用 INA + 还是 INB + 取决于 A/B 输入端 的电平;当 A/B 为高电平时,选用 INA ±;当 A/B 为低电平时,选用 INB ±。

#### ●PECLL—TLL 转换器

INB(INB+)输入和 SI(INB-)输入的功能是由 SO 输出脚上的连接方式决定的,若不需要 PECLL/ TLL 转换,则可将 SO 输出脚接到 VCC。利用内置检 测电路可以检测到这种连接方式,并可将以上两个 输入脚置为 INB ± 输入(即差分接收串行数据输

| 人); 若需要进行      |

|----------------|

| PECL/TLL 转换,则  |

| 应在 SO 输出端连     |

| 接一个 TLL 负载,    |

| 此时的 INB + 输入   |

| 即为 INB(单端 E-   |

| CL-100K 型串行数   |

| 据输入)。INB - 则   |

| 可作为 SI(单端      |

| ECK - 100K 型状  |

| 态)输入,而 SO 即    |

| 是 SI 转换成 TLL 电 |

|                |

平时的输出信号。

图 1 CY7B933 的引脚排列

图 2 CY7B933 内部结构框图

#### ●时钟同步器

时钟同步器由内部锁相环来保持与接收到的位 流频率的一致,同时提供内部移、解码时钟。

#### ●成帧器

成帧器可用于检查输入的位流和寻找字节的边 界,从而实现帧同步(字符同步)。成帧器中的组合 逻辑滤波器可用于寻找 X3.230 协议中定义的特殊 字符(K28.5),一旦该字符找到,时钟同步单元中的 位计数器将被同步复位,以开始同步接收数据,并将 串行数据位流准确地重组成字符帧。

#### ●移位器

移位器的作用是在位时钟控制下接收串行输入 的位流,同时将其送到成帧器,当接收满一帧后(10 位数据)便将其送到译码寄存器。

#### ●译码寄存器

译码寄存器在接收到来自移位器中的一帧数据 后将其送到译码器,但该数据在译码器译码至输出 期间仍将保持在译码寄存器中。

#### ●译码器

译码器将接收到的数据按 X3.230 协议定义的 码字符重新转换成"原始数据",然后再送到输出寄 存器中。

#### ●输出寄存器

输出寄存器用于保持译码后恢复的数据(Q0-Q7)、SC/D和RVS),以便在相应的输出脚输出。在 BIST 方式下,这个寄存器还可作为线性反馈移位寄

| 名称                   | 输入/输出               | 引 脚 功 能                                                                                                               |

|----------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------|

| $Q0 - Q7(Q_{b-h})$   | TTL电平输出             | 并行数据输出。Q0-Q7输出脚的值是刚接收到的数据。这几个脚的数据是随着 CKR 的变化而同步变化                                                                     |

| SC/D(Qa)             | TLL 电平输出            | 特殊字符/数据指示。SC/D表明接收的数据类型:SC/D是高电平,表明接收的<br>内容是控制码(特殊字符);SC/D是低电平,表明接收到的是数据字符                                           |

| RVS(Q <sub>J</sub> ) | TLL 电平输出            | 接收违例字符指示。当 RVS 为高点平时,表明在接收数据流中检测到违例字符;若为低电平,表明检测到错误码;在 BIST 方式时,若 RVS 为低电平,表明由<br>发送器、接收器以及链接线路等构成的整个系统工作正常           |

| RDY                  | TLL 电平输出            | 输出数据准备好。上的负脉冲表明已经接收到一个新数据,并且已经准备好传送。在接收到空字符时,RDY不出现负脉冲。在BIST方式下,RDY只是在每次测试循环中的最后一个字符出现时为高电平,其余时间保持低电平                 |

| CKR                  | TLL 输出              | 读数据时钟。它是一个读字节数据时钟信号,其频率和相位与输入的串行数据<br>流保持一致                                                                           |

| A/B                  | PECL 电平输入           | 串行数据输入端选择。它是 PECL100K 类型(接 5 伏参考电压)的输入端,用于<br>输入端的选择。若 A/B为高电平,INA 端连接到移位寄存器,INA 上的输入信<br>号有效并进行译码;若 A/B 为低电平,选 INB 端 |

| INA ±                | 差分输入                | 串行数据输入端(INA ± )                                                                                                       |

| INB(INB+)            | PECL 电平输入<br>(差分输入) | 串行数据输入 B 端。这个脚即可以作为单端方式的 PECL 接收端(INB),也可 以作为差分对的正半端(INB+)                                                            |

| SI                   | PECL 电平输入<br>(差分输入) | 状态输入。此脚即可以作为单端 PECL 状态监控输入(SI),也可以作为 INB 差 分的负半端(INB -)                                                               |

| SO                   | TLL 输出              | 状态输出。SO 是将 SI 转换为 TTL 信号的输出端                                                                                          |

| RF                   | TLL 输入              | 帧同步允许                                                                                                                 |

| REFCLK               | TLL 输入              | 参考时钟。RETCLK 是作为时钟/数据同步锁相环的一个参考时钟                                                                                      |

| MODE                 | 3—电平输入              | 译码方式选择。在 MODE 脚上的电平可决定采用的译码方式;当该脚接地时,<br>采用 8B/10B 译码方式;接 VCC 时,采用旁通方式;当其悬空时,内部上接电阻<br>将该脚拉成 VCC/2 电平;此时为工厂测试方式       |

| BISTEN               | TLL 输入              | 内置自测试允许。若要 ISTEN 置为低电平,则设置为内置测试方式                                                                                     |

| V <sub>CCN</sub>     |                     | 输出驱动电路供电电源                                                                                                            |

| V <sub>CCQ</sub>     |                     | 内部电路供电电源                                                                                                              |

| GND                  |                     | 地                                                                                                                     |

表 1 CY7B933 的引脚功能表

- 34 -

存器,以产生 512 字节的伪随机码。

●测试逻辑

测试逻辑包括 BIST 工作方式的初始化及控制 逻辑,以及用于测试方式时的时钟分配多工器和译 码器控制逻辑等。

#### 3 CY7B933 的工作原理及操作方式

#### 3.1 工作原理

CY7B933 接收器用于接收来自差分串行输入端 的串行位流,它使用内置的集成锁相环(PLL)同步 时钟产生器来恢复用于数据重构所需的位同步时 钟。成帧器在寻找到串行位流的字节边界后即可产 生帧同步时钟。然后输入位流数据即可在移位器中 实现串/并转换,同时再送到译码器中译码并检查传 送错误。最后将译码后的字节数据在帧同步时钟控 制下送到输出寄存器并由并行输出脚输出。

3.2 操作方式

CY7B933 具有 8B/10B 编码方式、旁通方式、内置自测试方式和测试方式四种接收操作方式。

a. 8B/10B 编码方式

在该编码方式下,串行输入的数据经译码后变成 8 位数据位,其中包括类型指示位及解码错误指示 位。若接收后放在译码寄存器中的数据帧能够在有效 数据字符表中找到,则其内容被译为正常的数据信 息,并使 SC/D 输出脚为低电平,假如在有效的特殊 字符码及码系列表中找到,则译为"控制"或"协议"信 息,并且将 SC/D 变高。若检测到非法字符,则 RVS 将 变高。

b. 旁通方式

在旁通方式下,串行输入数据不需由内部译码

器对其译码, 而是直接从译码寄存器到 10 位输出寄 存器(Qa-j), 然后由外加的译码电路来对其译码, 译码方式由设计者确定, 这种方式一般不用。

c. 内置自测试方式(BIST)

内置自测试功能有以下几种:

(1) 设置 BISTEN 为低, 允许自测试产生电路工作。若 RDY 变低,表明初始化码已找到。

(2) 监控 RVS 并检查该脚是否为高电平。若为 高电平,则表明测试到失配样本(数据帧)。

若系统工作正常,则在每次测试循环中使 RDY 出现一次正脉冲。可以对该脉冲进行计数以监控测 试过程。同时 Q0~Q7 和 SC/D 等脚也将出现预期 的样本值,这一点对系统调试是很有用的。

(3) 当测试完成时,设置 BISTEN 为高电平以恢 复正常工作。

BIST 方式主要用于检查发送器。由链接线路和 接收器构成的整个系统一般不用借助外加的信号及 电路,也不用对整个电路作任何改动即可对整个系 统进行严格的测试。

d. 测试方式

当 Mode 脚悬空时,接收器处于芯片测试方式。 这种方式一般作为工厂进行芯片测试或用户新购大 批器件进行测试时使用。

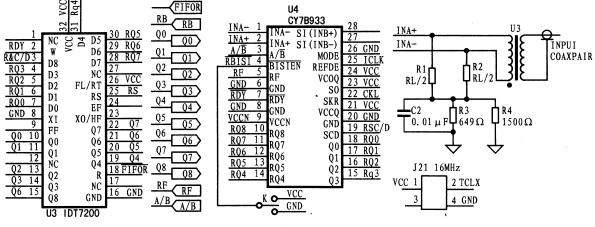

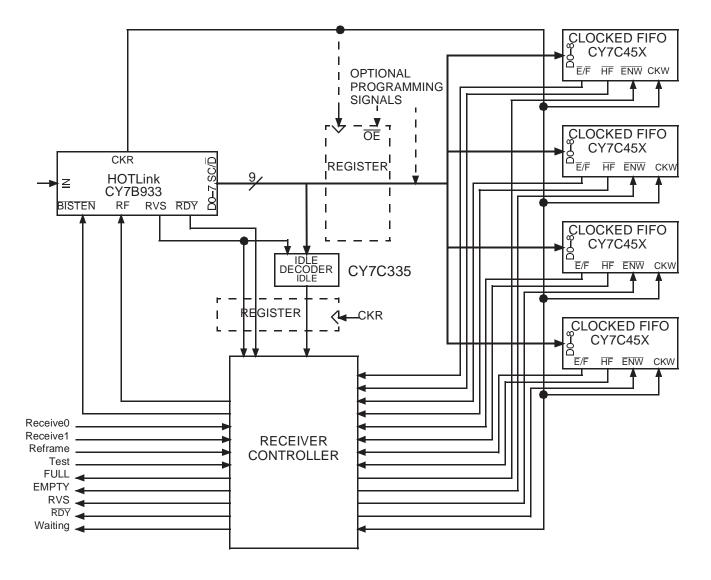

### 4 CY7B933 构成的接收电路设计

由 CY7B933 构成的接收电路如图 3 所示,该电路主要由 CY7B933 接收芯片、IDT7200 (FIFO)芯片和阻抗匹配电路等组成。FIFO 芯片 (IDT7200)的写信号 FIFOW 由 CY7B933 的 RDY 信号提供。利用开关 K 可将 CY7B933 的工作设置在 8B/10B 译码方式

图 3 CY7B933 构成的接收电路

或内置自测试方式。

当 BISTEN = 0 时, CY7B933 工作在内置自测试 方式。此时如果发送芯片 CY7B923 也工作在内置自 测试方式,则可以通过对 CY7B923 的 RP 和 CY7B933 的 RDY 脚进行测试比较来判断整个系统是否正常 工作。若这两个信号同步出现且相位相反(RP 为负 脉冲, RDY 为正脉冲),则表明整个系统的发送电 路、接收电路及其链接线路工作正常。

当 BISTEN = 1 时, CY7B933 工作在 8B/10 译码 方式。当 CY7B933 工作在这种方式时,接收并译码 后的数据可由 CY7B933 提供的 RDY 信号来写入 FI-FO 芯片 IDT7200 中。用户可通过 FIFO 的另一端来 读取该信号。注意:如按上述电路连接,则此时读取 的数据在同步接收到的起始字节中有一个 K28.5 字符(其值为 05H)。若要去掉该字符,可将 RDY 信 号与 SC/D 信号组合以产生 FIFO 写信号,这样,该 控制字符码(05H)就不会写入 FIFO 中,从而使 FIFO 中只包含用户的数据信息。

> 收稿日期:2001-05-22 **咨询编号:020112**

# HOTLink<sup>®</sup> Transmitter/Receiver

#### Features

- Fibre-Channel-compliant

- IBM ESCON<sup>®</sup>-compliant

- DVB-ASI-compliant

- ATM-compliant

- 8B/10B-coded or 10-bit unencoded

- Standard HOTLink<sup>®</sup>: 160–330 Mbps

- High-speed HOTLink: 160–400 Mbps for high-speed applications

- Low-speed HOTLink: 150–160 Mbps for low-cost fiber applications

- TTL synchronous I/O

- No external phase locked-loop (PLL) components

- Triple PECL 100K serial outputs

- Dual PECL 100K serial inputs

- Low power: 350 mW (Tx), 650 mW (Rx)

- · Compatible with fiber-optic modules, coaxial cable, and twisted pair media

- Built-in Self-Test (BIST)

- Single +5V supply

- 28-pin SOIC/PLCC/LCC

- 0.8m BiCMOS

#### **Functional Description**

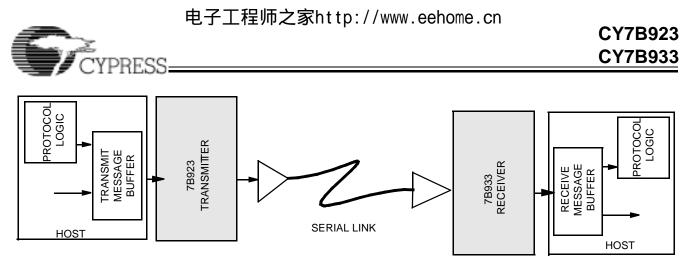

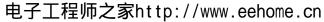

The CY7B923 HOTLink, Transmitter and CY7B933 HOTLink Receiver are point-to-point communications building blocks that transfer data over high-speed serial links (fiber, coax, and twisted pair). Standard HOTLink data rates range from 160-330 Mbits/second. Higher speed HOTLink is also available for high-speed applications (160-400 Mbits/second), as well as for those low-Cost applications HOTLink-155 (150-160 Mbits/second operations). Figure 1 illustrates typical connections to host systems or controllers.

Eight bits of user data or protocol information are loaded into the HOTLink transmitter and are encoded. Serial data is shifted out of the three differential positive ECL (PECL) serial ports at the bit rate (which is ten times the byte rate).

The HOTLink receiver accepts the serial bit stream at its differential line receiver inputs and, using a completely integrated PLL Clock Synchronizer, recovers the timing information necessary for data reconstruction. The bit stream is deserialized, decoded, and checked for transmission errors. Recovered bytes are presented in parallel to the receiving host along with a byte-rate clock.

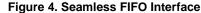

The 8B/10B encoder/decoder can be disabled in systems that already encode or scramble the transmitted data. I/O signals are available to create a seamless interface with both asynchronous FIFOs (i.e., CY7C42X) and clocked FIFOs (i.e., CY7C44X). A BIST pattern generator and checker allows testing of the transmitter, receiver, and the connecting link as a part of a system diagnostic check.

HOTLink devices are ideal for a variety of applications where a parallel interface can be replaced with a high-speed point-to-point serial link. Applications include interconnecting workstations, servers, mass storage, and video transmission equipment.

3901 North First Street San Jose, CA 95134 Cypress Semiconductor Corporation Document #: 38 项目开发 芯片解密 零件配单 TEL: 15013652265 QQ: 38537 442 March 25, 2003

Figure 1. HOTLink System Connections

### CY7B933 Receiver Pin Configurations

Document #: 38-02017 Rev. \*C

Page 2 of 30

### **Pin Descriptions**

#### CY7B923 HOTLink Transmitter

| Name                        | I/O                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ${D_{0-7} \choose D_{b-h}}$ | TTL In             | <b>Parallel Data Input</b> . Data is clocked into the Transmitter on the rising edge of CKW if $\overline{\text{ENA}}$ is LOW (or on the next rising CKW with $\overline{\text{ENN}}$ LOW). If $\overline{\text{ENA}}$ and $\overline{\text{ENN}}$ are HIGH, a Null character (K28.5) is sent. When MODE is HIGH, D <sub>0, 1,7</sub> become D <sub>b, c,h</sub> , respectively.                                                                                                                                                                                                                                                                                        |

| SC/D (D <sub>a</sub> )      | TTL In             | <b>Special Character/Data Select</b> . A HIGH on SC/ $\overline{D}$ when CKW rises causes the transmitter to encode the pattern on D <sub>0-7</sub> as a control code (Special Character), while a LOW causes the data to be coded using the 8B/10B data alphabet. When MODE is HIGH, SC/ $\overline{D}$ (D <sub>a</sub> ) acts as D <sub>a</sub> input. SC/ $\overline{D}$ has the same timing as D <sub>0-7</sub> .                                                                                                                                                                                                                                                   |

| SVS<br>(D <sub>j</sub> )    | TTL In             | <b>Send Violation Symbol</b> . If SVS is HIGH when CKW rises, a Violation symbol is encoded and sent while the data on the parallel inputs is ignored. If SVS is LOW, the state of $D_{0-7}$ and SC/D determines the code sent. In normal or test mode, this pin overrides the BIST generator and forces the transmission of a Violation code. When MODE is HIGH (placing the transmitter in unencoded mode), SVS ( $D_j$ ) acts as the $D_j$ input. SVS has the same timing as $D_{0-7}$ .                                                                                                                                                                             |

| ENA                         | TTL In             | <b>Enable</b> Parallel Data. If ENA is LOW on the rising edge of CKW, the data is loaded, encoded, and sent. If ENA and ENN are HIGH, the data inputs are ignored and the Transmitter will insert a Null character (K28.5) to fill the space between user data. ENA may be held HIGH/LOW continuously or it may be pulsed with each data byte to be sent. If ENA is being used for data control, ENN will normally be strapped HIGH, but can be used for BIST function control.                                                                                                                                                                                         |

| ENN                         | TTL In             | <b>Enable Next Parallel Data</b> . If <b>ENN</b> is LOW, the data appearing on $D_{0-7}$ at the next rising edge of CKW is loaded, encoded, and sent. If <b>ENA</b> and <b>ENN</b> are HIGH, the data appearing on $D_{0-7}$ at the next rising edge of CKW will be ignored and the Transmitter will insert a Null character to fill the space between user data. ENN may be held HIGH/LOW continuously or it may be pulsed with each data byte sent. If ENN is being used for data control, ENA will normally be strapped HIGH, but can be used for BIST function control.                                                                                             |

| CKW                         | TTL In             | <b>Clock Write</b> . CKW is both the clock frequency reference for the multiplying PLL that generates the high–speed transmit clock, and the byte rate write signal that synchronizes the parallel data input. CKW must be connected to a crystal controlled time base that runs within the specified frequency range of the Transmitter and Receiver.                                                                                                                                                                                                                                                                                                                  |

| FOTO                        | TTL In             | <b>Fiber Optic Transmitter Off.</b> FOTO determines the function of two of the three PECL transmitter output pairs. If FOTO is LOW, the data encoded by the Transmitter will appear at the outputs continuously. If FOTO is HIGH, OUTA $\pm$ and OUTB $\pm$ are forced to their "logic zero" state (OUT+ = LOW and OUT- = HIGH), causing a fiber optic transmit module to extinguish its light output. OUTC is unaffected by the level on FOTO, and can be used as a loop-back signal source for board-level diagnostic testing.                                                                                                                                        |

| OUTA±<br>OUTB±<br>OUTC±     | PECLOut            | <b>Differential Serial Data Outputs</b> . These PECL 100K outputs (+5V referenced) are capable of driving terminated transmission lines or commercial fiber optic transmitter modules. Unused pairs of outputs can be left open, or wired to $V_{CC}$ to reduce power, if the output is not required. OUTA± and OUTB± are controlled by the level on FOTO, and will remain at their "logical zero" states when FOTO is asserted. OUTC± is unaffected by the level on FOTO. (OUTA+ and OUTB+ are used as a differential test clock input while in Test mode, i.e., MODE = UNCONNECTED or forced to $V_{CC/2}$ .)                                                         |

| MODE                        | Three-<br>Level In | <b>Encoder Mode Select</b> . The level on MODE determines the encoding method to be used. When wired to GND, MODE selects 8B/10B encoding. When wired to $V_{CC}$ , data inputs bypass the encoder and the bit pattern on $D_{a-j}$ goes directly to the shifter. When left floating (internal resistors hold the input at $V_{CC}/2$ ) the internal bit-clock generator is disabled and OUTA+/OUTB+ become the differential bit clock to be used for factory test. In typical applications MODE is wired to $V_{CC}$ or GND.                                                                                                                                           |

| BISTEN                      | TTL In             | <b>BIST Enable</b> . When <b>BISTEN</b> is LOW and <b>ENA</b> and <b>ENN</b> are HIGH, the transmitter sends an alternating 1–0 pattern (D10.2 or D21.5). When either ENA or ENN is set LOW and BISTEN is LOW, the transmitter begins a repeating test sequence that allows the Transmitter and Receiver to work together to test the function of the entire link. In normal use this input is held HIGH or wired to V <sub>CC</sub> . The BIST generator is a free-running pattern generator that need not be initialized, but if required, the BIST sequence can be initialized by momentarily asserting SVS while BISTEN is LOW. BISTEN has the same timing as D0-7. |

Document #: 38-02017 Rev. \*C

#### CY7B923 HOTLink Transmitter (continued)

| Name             | I/O     | Description                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RP               | TTL Out | <b>Read Pulse</b> . RP is a 60% LOW duty-cycle byte-rate pulse train suitable for the read pulse in CY7C42X FIFOs. The frequency on RP is the same as CKW when enabled by ENA, and duty cycle is independent of the CKW duty cycle. Pulse widths are set by logic internal to the transmitter. In BIST mode, RP will remain HIGH for all but the last byte of a test loop. RP will pulse LOW one byte time per BIST loop. |

| V <sub>CCN</sub> |         | Power for output drivers.                                                                                                                                                                                                                                                                                                                                                                                                 |

| V <sub>CCQ</sub> |         | Power for internal circuitry.                                                                                                                                                                                                                                                                                                                                                                                             |

| GND              |         | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                   |

#### CY7B933 HOTLink Receiver

| Name                                      | I/O                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Q <sub>0-7</sub><br>(Q <sub>b - h</sub> ) | TTL Out              | <b>Q0-7 Parallel Data Output</b> . $Q_{0-7}$ contain the most recently received data. These outputs change synchronously with CKR. When MODE is HIGH, $Q_{0, 1,7}$ become $Q_{b, c,h}$ , respectively.                                                                                                                                                                                                                                                                                                                                                               |

| SC/D(Q <sub>a</sub> )                     | TTL Out              | <b>Special Character/Data Select</b> . SC/ $\overline{D}$ indicates the context of received data. HIGH indicates a Control (Special Character) code, LOW indicates a Data character. When MODE is HIGH (placing the receiver in Unencoded mode), SC/ $\overline{D}$ acts as the Q <sub>a</sub> output. SC/ $\overline{D}$ has the same timing as Q <sub>0-7</sub> .                                                                                                                                                                                                  |

| RVS (Q <sub>j</sub> )                     | TTL Out              | <b>Received Violation Symbol</b> . A HIGH on RVS indicates that a code rule violation has been detected in the received data stream. A LOW shows that no error has been detected. In BIST mode, a LOW on RVS indicates correct operation of the Transmitter, Receiver, and link on a byte-by-byte basis. When MODE is HIGH (placing the receiver in Unencoded mode), RVS acts as the $Q_j$ output. RVS has the same timing as $Q_{0-7}$ .                                                                                                                            |

| RDY                                       | TTL Out              | <b>Data Output Ready</b> . A LOW pulse on RDY indicates that new data has been received and is ready to be delivered. A missing pulse on RDY shows that the received <u>data</u> is the Null character (normally inserted by the transmitter as a pad between data inputs). In BIST mode RDY will remain LOW for all but the last byte of a test loop and will pulse HIGH one byte time per BIST loop.                                                                                                                                                               |

| CKR                                       | TTL Out              | <b>Clock Read</b> . This byte rate clock output is phase and frequency aligned to the incoming serial data stream. RDY, $Q_{0-7}$ , SC/D, and RVS all switch synchronously with the rising edge of this output.                                                                                                                                                                                                                                                                                                                                                      |

| A/B                                       | PECL in              | Serial Data Input Select. This PECL 100K (+5V referenced) input selects INA or INB as the active data input. If A/B is HIGH, INA is connected to the shifter and signals connected to INA will be decoded. If A/B is LOW INB is selected.                                                                                                                                                                                                                                                                                                                            |

| INA±                                      | Diff In              | <b>Serial Data Input A</b> . The differential signal at the receiver end of the communication link may be connected to the differential input pairs INA± or INB±. Either the INA pair or the INB pair can be used as the main data input and the other can be used as a loopback channel or as an alternative data input selected by the state of A/B. One input of an intentionally unused differential-pair (INA± or INB±) should be terminated to $V_{CC}$ through a 1–5 K $\Omega$ resistor to assure that no data transitions are accidentally created.         |

| INB<br>(INB+)                             | PECL in<br>(Diff In) | <b>Serial Data Input B</b> . This pin is either a single-ended PECL data receiver (INB) or half of the INB differential pair. If SO is wired to $V_{CC}$ , then INB± can be used as differential line receiver interchangeably with INA±. If SO is normally connected and loaded, INB becomes a single-ended PECL 100K (+5V referenced) serial data input. INB is used as the test clock while in Test mode.                                                                                                                                                         |

| SI<br>(INB–)                              | PECL in<br>(Diff In) | <b>Status Input</b> . This pin is either a single-ended PECL status monitor input (SI) or half of the INB differential pair. If SO is wired to $V_{CC}$ , then INB± can be used as differential line receiver interchangeably with INA±. If SO is normally connected and loaded, SI becomes a single-ended PECL 100K (+5V referenced) status monitor input, which is translated into a TTL-level signal at the SO pin.                                                                                                                                               |

| SO                                        | TTL Out              | <b>Status Out</b> . SO is the TTL-translated output of SI. It is typically used to translate the Carrier Detect output from a fiber-optic receiver connected to SI. When this pin is normally connected and loaded (without any external pull-up resistor), SO will assume the same logical level as SI and INB will become a single-ended PECL serial data input. If the status monitor translation is not desired, then SO may be wired to V <sub>CC</sub> and the INB± pair may be used as a differential serial data input.                                      |

| RF                                        | TTL In               | <b>Reframe Enable</b> . RF controls the Framer logic in the Receiver. When RF is held HIGH, each SYNC (K28.5) symbol detected in the shifter will frame the data that follows. If it is HIGH for 2,048 consecutive bytes, the internal framer switches to double-byte mode. When RF is held LOW, the reframing logic is disabled. The incoming data stream is then continuously deserialized and decoded using byte boundaries set by the internal byte counter. Bit errors in the data stream will not cause alias SYNC characters to reframe the data erroneously. |

Document #: 38-02017 Rev. \*C

#### CY7B933 HOTLink Receiver (continued)

| Name             | I/O                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REFCLK           | TTL In             | <b>Reference Clock</b> . REFCLK is the clock frequency reference for the clock/data synchronizing PLL.<br>REFCLK sets the approximate center frequency for the internal PLL to track the incoming bit stream.<br>REFCLK must be connected to a crystal-controlled time base that runs within the frequency limits of the Tx/Rx pair, and the frequency must be the same as the transmitter CKW frequency (within CKW $\pm$ 0.1%).                                                                                    |

| MODE             | Three-<br>Level In | <b>Decoder Mode Select</b> . The level on the MODE pin determines the decoding method to be used. When wired to GND, MODE selects 8B/10B decoding. When wired to $V_{CC}$ , registered shifter contents bypass the decoder and are sent to $Q_{a-j}$ directly. When left floating (internal resistors hold the MODE pin at $V_{CC}/2$ ) the internal bit clock generator is disabled and INB becomes the bit rate test clock to be used for factory test. In typical applications, MODE is wired to $V_{CC}$ or GND. |

| BISTEN           | TTL In             | <b>Built-In Self-Test Enable</b> . When BISTEN is LOW the Receiver awaits a D0.0 (sent once per BIST loop) character and begins a continuous test sequence that tests the functionality of the Transmitter, the Receiver, and the link connecting them. In BIST mode the status of the test can be monitored with RDY and RVS outputs. In normal use BISTEN is held HIGH or wired to $V_{CC}$ . BISTEN has the same timing as $Q_{0-7}$ .                                                                            |

| V <sub>CCN</sub> |                    | Power for output drivers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| V <sub>CCQ</sub> |                    | Power for internal circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| GND              |                    | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

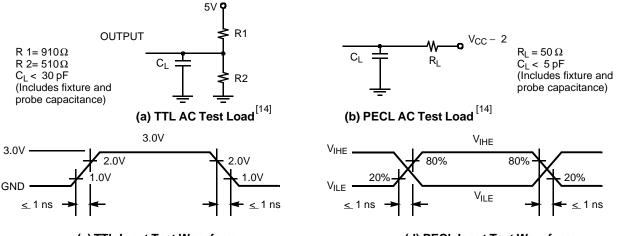

#### CY7B923 HOTLink Transmitter Block Diagram Description

#### Input Register

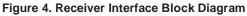

The Input register holds the data to be processed by the HOTLink transmitter and allows the input timing to be made consistent with standard FIFOs. The Input register is clocked by CKW and loaded with information on the D<sub>0-7</sub>, SC/D, and SVS pins. Two enable inputs (ENA and ENN) allow the user to choose when data is loaded in the register. Asserting ENA (Enable, active LOW) causes the inputs to be loaded in the register on the rising edge of CKW. If ENN (Enable Next, active LOW) is asserted when CKW rises, the data present on the inputs on the next rising edge of CKW will be loaded into the Input register. If neither ENA nor ENN are asserted LOW on the rising edge of CKW, then a SYNC (K28.5) character is sent. These two inputs allow proper timing and function for compatibility with either asynchronous FIFOs or clocked FIFOs without external logic, as shown in *Figure 4*.

In BIST mode, the Input register becomes the signature pattern generator by logically converting the parallel Input register into a Linear Feedback Shift Register (LFSR). When enabled, this LFSR will generate a 511-byte sequence that includes all Data and Special Character codes, including the explicit violation symbols. This pattern provides a predictable but pseudo-random sequence that can be matched to an identical LFSR in the Receiver.

#### Encoder

The Encoder transforms the input data held by the Input register into a form more suitable for transmission on a serial interface link. The code used is specified by ANSI X3.230 (Fibre Channel) and the IBM ESCON channel (code tables are at the end of this datasheet). The eight  $D_{0-7}$  data inputs are converted to either a Data symbol or a Special Character, depending upon the state of the SC/D input. If SC/D is HIGH, the data inputs represent a control code and are encoded using the Special Character code table. If SC/D is LOW, the data inputs are converted using the Data code table. If a byte time passes with the inputs disabled, the Encoder will output a Special Character

Comma K28.5 (or SYNC) that will maintain link synchronization. SVS input forces the transmission of a specified Violation symbol to allow the user to check error handling system logic in the controller or for proprietary applications.

The 8B/10B coding function of the Encoder can be bypassed for systems that include an external coder or scrambler function as part of the controller. This bypass is controlled by setting the MODE select pin HIGH. When in bypass mode,  $D_{a-j}$  (note that bit order is specified in the Fibre Channel 8B/10B code) become the ten inputs to the Shifter, with  $D_a$  being the first bit to be shifted out.

#### Shifter

The Shifter accepts parallel data from the Encoder once each byte time and shifts it to the serial interface output buffers using a PLL multiplied bit clock that runs at ten (10) times the byte clock rate. Timing for the parallel transfer is controlled by the counter included in the Clock Generator and is not affected by signal levels or timing at the input pins.

#### OutA, OutB, OutC

The serial interface PECL output buffers (ECL100K referenced to +5V) are the drivers for the serial media. They are all connected to the Shifter and contain the same serial data. Two of the output pairs (OUTA± and OUTB±) are controllable by the FOTO input and can be disabled by the system controller to force a logical zero (i.e., "light off") at the outputs. The third output pair (OUTC±) is not affected by FOTO and will supply a continuous data stream suitable for loop-back testing of the subsystem.

OUTA± and OUTB± will respond to FOTO input changes within a few bit times. However, since FOTO is not synchronized with the transmitter data stream, the outputs will be forced off or turned on at arbitrary points in a transmitted byte. This function is intended to augment an external laser safety controller and as an aid for Receiver PLL testing.

In wire-based systems, control of the outputs may not be required, and FOTO can be strapped LOW. The three outputs are intended to add system and architectural flexibility by offering identical serial bit streams with separate interfaces for

Document #: 38-02017 Rev. \*C

redundant connections or for multiple destinations. Unneeded outputs can be wired to VCC to disable and power down the unused output circuitry.

#### **Clock Generator**

The clock generator is an embedded phase-locked loop (PLL) that takes a byte-rate reference clock (CKW) and multiplies it by ten (10) to create a bit rate clock for driving the serial shifter. The byte rate reference comes from CKW, the rising edge of which clocks data into the Input register. This clock must be a crystal referenced pulse stream that has a frequency between the minimum and maximum specified for the HOTLink Transmitter/Receiver pair. Signals controlled by this block form the bit clock and the timing signals that control internal data transfers between the Input register and the Shifter.

The read pulse  $(\overline{RP})$  is derived from the feedback counter used in the PLL multiplier. It is a byte-rate pulse stream with the proper phase and pulse widths to allow transfer of data from an asynchronous FIFO. Pulse width is independent of CKW duty cycle, since proper phase and duty cycle is maintained by the PLL. The RP pulse stream will insure correct data transfers between asynchronous FIFOs and the transmitter input latch with no external logic.

#### **Test Logic**

Test logic includes the initialization and control for the Built-In Self-Test (BIST) generator, the multiplexer for Test mode clock distribution, and control logic to properly select the data encoding. Test logic is discussed in more detail in the CY7B923 HOTLink Transmitter Operating Mode Description.

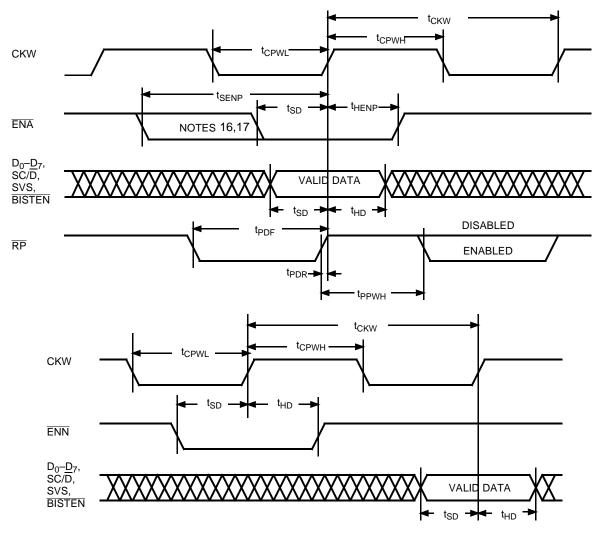

#### CY7B933 HOTLink Receiver Block Diagram Description

#### **Serial Data Inputs**

Two pairs of differential line receivers are the inputs for the serial data stream. INA± or INB± can be selected with the A/B input. INA± is selected with A/B HIGH and INB± is selected with A/B LOW. The threshold of A/B is compatible with the ECL 100K signals from PECL fiber optic interface modules. TTL logic elements can be used to select the A or B inputs by adding a resistor pull-up to the TTL driver connected to A/B. The differential threshold of INA± and INB± will accommodate wire interconnect with filtering losses or transmission line attenuation greater than 20 db (V<sub>DIF</sub> ≥ 50 mv) or can be directly connected to fiber optic interface modules (any ECL logic family, not limited to ECL 100K). The common mode tolerance will accommodate a wide range of signal termination voltages. The highest HIGH input that can be tolerated is  $V_{IN} = V_{CC}$ , and the lowest LOW input that can be interpreted correctly is  $V_{IN}$  = GND+2.0V.

#### **PECL-TTL Translator**

The function of the INB(INB+) input and the SI(INB-) input is defined by the connections on the SO output pin. If the PECL/TTL translator function is not required, the SO output is wired to VCC. A sensor circuit will detect this connection and cause the inputs to become INB± (a differential line-receiver serial-data input). If the PECL/TTL translator function is required, the SO output is connected to its normal TTL load (typically one or more TTL inputs, but no pull-up resistor) and the INB+ input becomes INB (single-ended ECL 100K, serial data input).

This positive-referenced PECL-to-TTL translator is provided to eliminate external logic between an PECL fiber-optic interface module "carrier detect" output and the TTL input in the control logic. The input threshold is compatible with ECL 100K levels (+5V referenced). It can also be used as part of the link status indication logic for wire connected systems.

#### **Clock Synchronization**

The Clock Synchronization function is performed by an embedded PLL that tracks the frequency of the incoming bit stream and aligns the phase of its internal bit rate clock to the serial data transitions. This block contains the logic to transfer the data from the Shifter to the Decode register once every byte. The counter that controls this transfer is initialized by the Framer logic. CKR is a buffered output derived from the bit counter used to control the Decode register and the output register transfers.

Clock output logic is designed so that when reframing causes the counter sequence to be interrupted, the period and pulse width of CKR will never be less than normal. Reframing may stretch the period of CKR by up to 90%, and either CKR Pulse Width HIGH or Pulse Width LOW may be stretched, depending on when reframe occurs.

The REFCLK input provides a byte-rate reference frequency to improve PLL acquisition time and limit unlocked frequency excursions of the CKR when no data is present at the serial inputs. The frequency of REFCLK is required to be within  $\pm 0.1\%$  of the frequency of the clock that drives the transmitter CKW pin.

#### Framer

Framer logic checks the incoming bit stream for the pattern that defines the byte boundaries. This combinatorial logic filter looks for the X3.230 symbol defined as a Special Character Comma (K28.5). When it is found, the free-running bit counter in the Clock Synchronization block is synchronously reset to its initial state, thus framing the data correctly on the correct byte boundaries.

Random errors that occur in the serial data can corrupt some data patterns into a bit pattern identical to a K28.5, and thus cause an erroneous data-framing error. The RF input prevents this by inhibiting reframing during times when normal message data is present. When RF is held LOW, the HOTLink receiver will deserialize the incoming data without trying to reframe the data to incoming patterns. When RF rises, <u>RDY</u> will be inhibited until a K28.5 has been detected, after which RDY will resume its normal function. While RF is HIGH, it is possible that an error could cause misframing, after which all data will be corrupted. Likewise, a K28.7 followed by D11.x, D20.x, or an SVS (C0.7) followed by D11.x will create alias K28.5 characters and cause erroneous framing. These sequences must be avoided while RF is HIGH.

If RF remains HIGH for greater than 2048 bytes, the framer converts to double-byte framing, requiring two K28.5 characters aligned on the same byte boundary within 5 bytes in order to reframe. Double-byte framing greatly reduces the possibility of erroneously reframing to an aliased K28.5 character.

#### Shifter

The Shifter accepts serial inputs from the Serial Data inputs one bit at a time, as clocked by the Clock Synchronization

Document #: 38-02017 Rev. \*C 项目开发 芯片解密 零件配单 TEL:15013652265 QQ:38537442

logic. Data is transferred to the Framer on each bit, and to the Decode register once per byte.

#### **Decode Register**

The Decode register accepts data from the Shifter once per byte as determined by the logic in the Clock Synchronization block. It is presented to the Decoder and held until it is transferred to the output latch.

#### Decoder

Parallel data is transformed from ANSI-specified X3.230 8B/10B codes back to "raw data" in the Decoder. This block uses the standard decoder patterns shown in the Valid Data Characters and Valid Special Character Codes and Sequences sections of this datasheet. Data patterns are signaled by a LOW on the SC/D output and Special Character patterns are signaled by a HIGH on the SC/D output. Unused patterns or disparity errors are signaled as errors by a HIGH on the RVS output and by specific Special Character codes.

#### **Output Register**

The Output register holds the recovered data ( $Q_{0^{-7}}$ , SC/ $\overline{D}$ , and RVS) and aligns it with the recovered byte clock (CKR). This synchronization insures proper timing to match a FIFO interface or other logic that requires glitch free and specified output behavior. Outputs change synchronously with the rising edge of CKR.

In BIST mode, this register becomes the signature pattern generator and checker by logically converting itself into a Linear Feedback Shift Register (LFSR) pattern generator. When enabled, this LFSR will generate a 511-byte sequence that includes all Data and Special Character codes, including the explicit violation symbols. This pattern provides a predictable but pseudo-random sequence that can be matched to an identical LFSR in the Transmitter. When synchronized, it checks each byte in the Decoder with each byte generated by the LFSR and shows errors at RVS. Patterns generated by the LFSR are compared after being buffered to the output pins and then fed back to the comparators, allowing test of the entire receive function.

In BIST mode, the LFSR is initialized by the first occurrence of the transmitter BIST loop start code D0.0 (D0.0 is sent only once per BIST loop). Once the BIST loop has been started, RVS will be HIGH for pattern mismatches between the received sequence and the internally generated sequence. Code rule violations or running disparity errors that occur as part of the BIST loop will not cause an error indication. RDY will pulse HIGH once per BIST loop and can be used to check test pattern progress. The receiver BIST generator can be reinitialized by leaving and re-entering BIST mode.

#### Test Logic

Test logic includes the initialization and control for the Built-In Self-Test (BIST) generator, the multiplexer for Test mode clock distribution, and control logic for the decoder. Test logic is discussed in more detail in the CY7B933 HOTLink Receiver Operating Mode Description.

#### HOTLink CY7B923 Transmitter and CY7B933 Receiver Operation

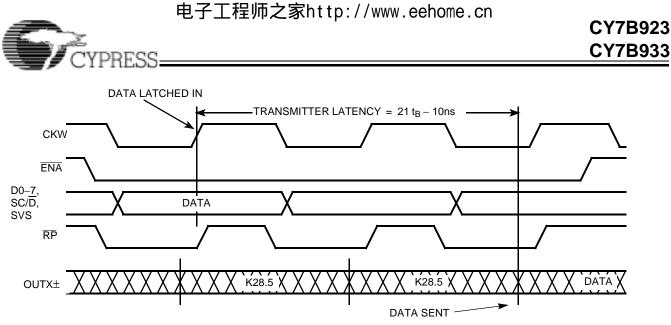

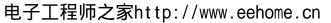

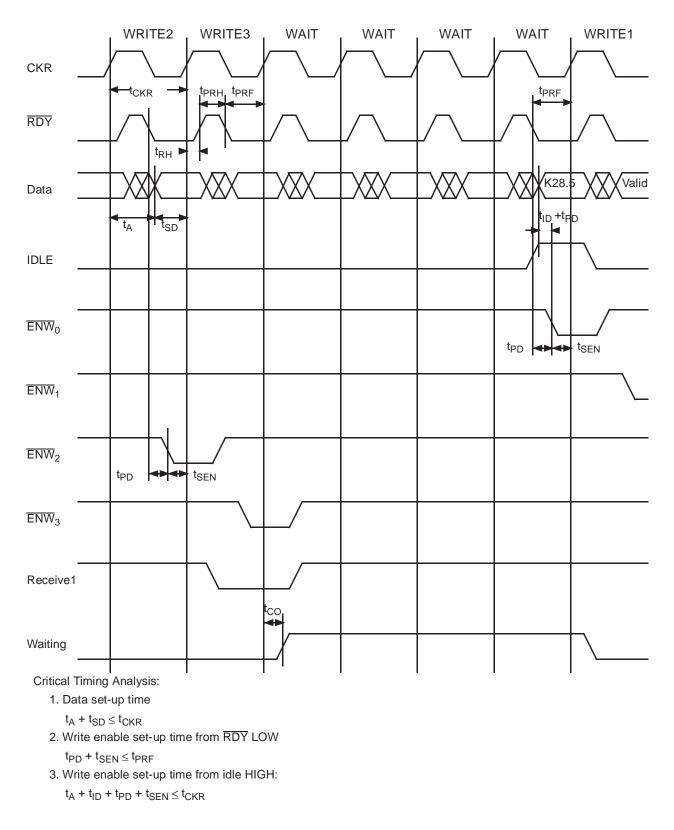

The CY7B923 Transmitter operating with the CY7B933 Receiver form a general purpose data communications subsystem capable of transporting user data at up to 33 Mbytes per second (40 Mbytes per second for -400 devices) over several types of serial interface media. Figure 7 illustrates the flow of data through the HOTLink CY7B923 transmitter pipeline. Data is latched into the transmitter on the rising edge of CKW when enabled by ENA or ENN. RP is asserted LOW with a 60% LOW/40% HIGH duty cycle when ENA is LOW. RP may be used as a read strobe for accessing data stored in a FIFO. The parallel data flows through the encoder and is then shifted out of the OUTx±PECL drivers. The bit-rate clock is generated internally from a multiply-by-ten PLL clock generator. The latency through the transmitter is approximately 21tB - 10 ns over the operating range. A more complete description is found in the section CY7B923 HOTLink Transmitter Operating Mode Description.

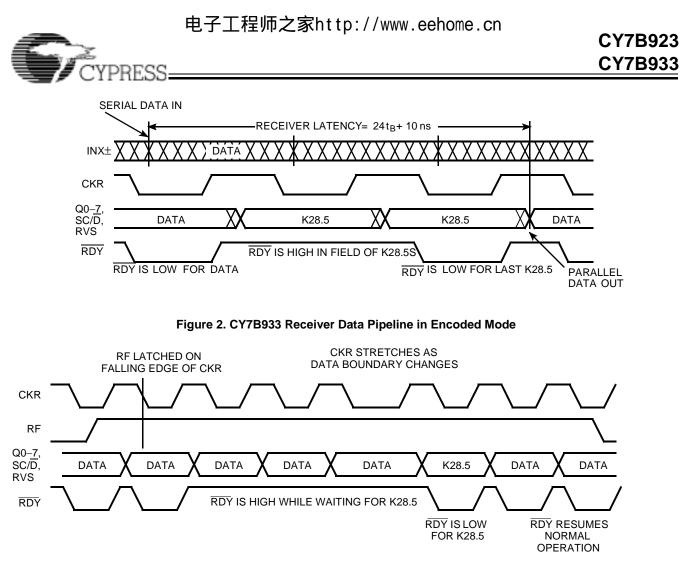

*Figure 2* illustrates the data flow through the HOTLink CY7B933 receiver pipeline. Serial data is sampled by the receiver on the INx± inputs. The receiver PLL locks onto the serial bit stream and generates an internal bit rate clock. The bit stream is deserialized, decoded and then presented at the parallel output pins. A byte rate clock (bit clock <sup>3</sup> 10) synchronous with the parallel data is presented at the CKR pin. The RDY pin will be asserted to LOW to indicate that data or control characters are present on the outputs. RDY will not be asserted LOW in a field of K28.5s except for any single K28.5 or the last one in a continuous series of K28.5's. The latency through the receiver is approximately  $24t_B + 10$  ns over the operating range. A more complete description of the receiver is in the section CY7B933 HOTLink Receiver Operating Mode Description.

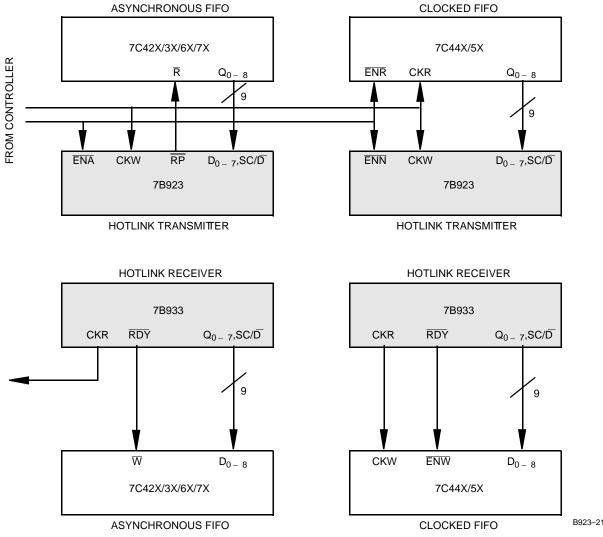

The HOTLink Receiver has a built-in byte framer that synchronizes the Receiver pipeline with incoming SYNC (K28.5) characters. *Figure 3* illustrates the HOTLink CY7B933 Receiver framing operation. The Framer is enabled when the RF pin is asserted HIGH. RF is latched into the receiver on the falling edge of CKR. The framer looks for K28.5 characters embedded in the serial data stream. When a K28.5 is found, the framer sets the parallel byte boundary for subsequent data to the K28.5 boundary. While the framer is enabled, the RDY pin indicates the status of the framing operation.

Document #: 38-02017 Rev. \*C

Page 7 of 30

#### Figure 3. CY7B933 Framing Operation in Encoded Mode

When the RF pin is asserted HIGH, RDY leaves it normal mode of operation and is asserted HIGH while the framer searches the data stream for a K28.5 character. After the framer has synchronized to a K28.5 character, the Receiver will assert the RDY pin LOW when the K28.5 character is present at the parallel output. The RDY pin will then resume its normal operation as dictated by the MODE and BISTEN pins.

The normal operation of the  $\overline{\text{RDY}}$  pin in encoded mode is to signal when parallel data is present at the output pin<u>s</u> by pulsing LOW with a 60% LOW/40% HIGH duty cycle. RDY does not pulse LOW in a field of K28.5 characters; however, RDY does pulse LOW for the last K28.5 character in the field or for any single K28.5. In unencoded mode, the normal operation of the RDY pin is to signal when any K28.5 is at the parallel output pins.

The Transmitter and Receiver parallel interface timing and functionality can be made to match the timing and functionality of either an asynchronous FIFO or a clocked FIFO by appropriately connecting signals (See *Figure 4*). Proper operation of the FIFO interface depends upon various FIFO-specific access and response specifications.

The HOTLink Transmitter and Receiver serial interface provides a seamless interface to various types of media. A minimal number of external components are needed to

Document #: 38-02017 Rev. \*C

properly terminate transmission lines and provide PECL loads. For proper power supply decoupling, a single 0.01 mF for each device is all that is required to bypass the VCC and GND pins. *Figure 5* illustrates a HOTLink Transmitter and Receiver interface to fiber optic and copper media. More information on interfacing HOTLink to various media can be found in the *HOTLink Design Considerations* application note.

#### CY7B923 HOTLink Transmitter Operating Mode Description

In normal operation, the Transmitter can operate in either of two modes. The Encoded mode allows a user to send and receive eight-bit data and control information without first converting it to transmission characters. The Bypass mode is used for systems in which the encoding and decoding is performed in an external protocol controller.

In either mode, data is loaded into the Input register of the Transmitter on the rising edge of CKW. The input timing and functional response of the Transmitter input can be made to match the timing and functionality of either an asynchronous FIFO or a clocked FIFO by an appropriate connection of input signals (see *Figure 4*). Proper operation of the FIFO interface depends upon various FIFO-specific access and response specifications.

#### **Encoded Mode Operation**

In Encoded mode the input data is interpreted as eight bits of data (D0 – D7), a context control bit (SC/D), and a system diagnostic input bit (SVS). If the context of the data is to be normal message data, the SC/D input should be LOW, and the data should be encoded using the valid data character set described in the Valid Data Characters section of this datasheet. If the context of the data is to be control or protocol information, the SC/D input will be HIGH, and the data will be encoded using the valid special character set described in the Valid Special Character Codes and Sequences section. Special characters include all protocol characters necessary

to encode packets for Fibre Channel, ESCON, proprietary systems, and diagnostic purposes.

The diagnostic characters and sequences available as Special Characters include those for Fibre Channel link testing, as well as codes to be used for testing system response to link errors and timing. A Violation symbol can be explicitly sent as part of a user data packet (i.e., send C0.7;  $D_{7-0} = 111\ 00000$  and SC/ $\overline{D} = 1$ ), or it can be sent in response to an external system using the SVS input. This will allow system diagnostic logic to evaluate the errors in an unambiguous manner, and will not require any modification to the transmission interface to force transmission errors for testing purposes.

#### **Bypass Mode Operation**

In Bypass mode the input data is interpreted as ten (10) bits  $(D_{b-h})$ , SC/ $\overline{D}$  (Da), and SVS (Dj) of pre-encoded transmission data to be serialized and sent over the link. This data can use any encoding method suitable to the designer. The only restrictions upon the data encoding method is that it contain suitable transition density for the Receiver PLL data synchronizer (one per 10 bit byte), and that it be compatible with the transmission media.

Data loaded into the Input register on the rising edge of CKW will be loaded into the Shifter on the subsequent rising edges of CKW. It will then be shifted to the outputs one bit at a time using the internal clock generated by the clock generator. The first bit of the transmission character (Da) will appear at the output (OUTA±, OUTB±, and OUTC±) after the next CKW edge.

While in either the Encoded mode or Bypass mode, if a <u>CKW</u> edge arrives when the inputs are not enabled (ENA and ENN both HIGH), the Encoder will insert a pad character K28.5 (e.g., C5.0) to maintain proper link synchronization (in Bypass

Document #: 38-02017 Rev.\*C 项目开发 芯片解密 零件配单 TEL:15013652265 QQ:38537442

mode the proper sense of running disparity cannot be guaranteed for the first pad character, but is correct for all pad characters that follow). This automatic insertion of pad characters can be inhibited by insuring that the Transmitter is always enabled (i.e., ENA or ENN is hard-wired LOW).

#### **PECL Output Functional and Connection Options**

The three pairs of PECL outputs all contain the same information and are intended for use in systems with multiple connections. Each output pair may be connected to a different serial media, each of which may be a different length, link type, or interface technology. For systems that do not require all three output pairs, the unused pairs should be wired to  $V_{CC}$  to minimize the power dissipated by the output circuit, and to minimize unwanted noise generation. An internal voltage comparator detects when an output differential pair is wired to  $V_{CC}$ , causing the current source for that pair to be disabled. This results in a power savings of around 5 mA for each unused pair.

In systems that require the outputs to be shut off during some periods when link transmission is prohibited (e.g., for laser safety functions), the FOTO input can be asserted. While it is possible to insure that the output state of the PECL drivers is LOW (i.e., light is off) by sending all 0's in Bypass mode, it is often inconvenient to insert this level of control into the data transmission channel, and it is impossible in Encoded mode. FOTO is provided to simplify and augment this control function (typically found in laser-based transmission systems). FOTO will force OUTA+ and OUTB+ to go LOW, OUTA- and OUTB- to go HIGH, while allowing OUTC± to continue to function normally (OUTC is typically used as a diagnostic feedback and cannot be disabled). This separation of function allows various system configurations without undue load on the control function or data channel logic.

#### **Transmitter Serial Data Characteristics**

The CY7B923 HOTLink Transmitter serial output conforms to the requirements of the Fibre Channel specification. The serial data output is controlled by an internal Phase-Locked Loop that multiplies the frequency of CKW by ten (10) to maintain the proper bit clock frequency. The jitter characteristics (including both PLL and logic components) are shown below:

- Deterministic Jitter (D<sub>j</sub>) < 35 ps (peak-peak). Typically measured while sending a continuous K28.5 (C5.0).

- Random Jitter (R<sub>j</sub>) < 175 ps (peak-peak). Typically measured while sending a continuous K28.7 (C7.0).

#### **Transmitter Test Mode Description**

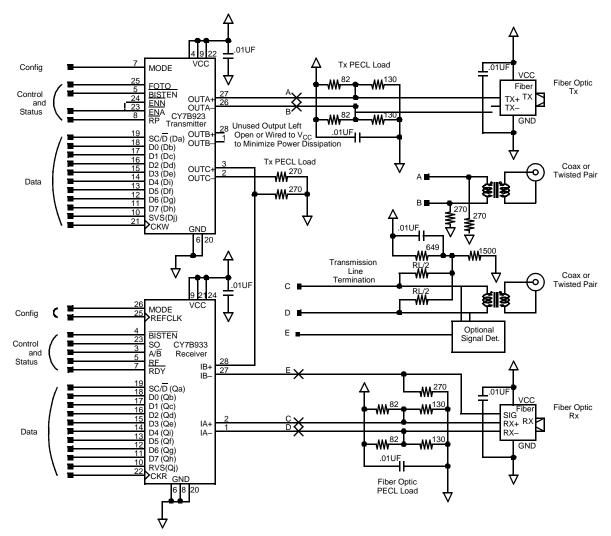

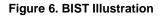

The CY7B923 Transmitter offers two types of test mode operation, BIST mode and Test mode. In a normal system application, the Built-In Self-Test (BIST) mode can be used to check the functionality of the Transmitter, the Receiver, and the link connecting them. This mode is available with minimal impact on user system logic, and can be used as part of the normal system diagnostics. Typical connections and timing are shown in *Figure 6*.

Document #: 38-02017 Rev. \*C

Document #: 38-02017 Rev. \*C 项目开发 芯片解密 零件配单 TEL:15013652265 QQ:38537442

Page 11 of 30

#### BIST Mode

BIST mode functions as follows:

- 1. Set BISTEN LOW to begin test pattern generation. Transmitter begins sending bit rate ...1010...

- 2. Set either ENA or ENN LOW to begin pattern sequence generation (use of the Enable pin not being used for normal FIFO or system interface can minimize logic delays between the controller and transmitter).

- 3. Allow the Transmitter to run through several BIST loops or until the Receiver test is complete. RP will pulse LOW once

per BIST loop, and can be used by an external counter to monitor the number of test pattern loops.

4. When testing is completed, set BISTEN HIGH and ENA and ENN HIGH and resume normal function.

**Note**: It may be advisable to send violation characters to test the RVS output in the Receiver. This can be done by explicitly sending a violation with the SVS input, or allowing the transmitter BIST loop to run while the Receiver runs in normal mode. The BIST loop includes deliberate violation symbols and will adequately test the RVS function.

Document #: 38-02017 Rev. \*C 项目开发 芯片解密 零件配单 TEL:15013652265 QQ:38537442

Page 12 of 30

BIST mode is intended to check the entire function of the Transmitter (except the Transmitter input pins and the bypass function in the Encoder), the serial link, and the Receiver. It augments normal factory ATE testing and provides the designer with a rigorous test mechanism to check the link transmission system without requiring any significant system overhead.

While in Bypass mode, the BIST logic will function in the same way as in the Encoded mode. MODE = HIGH and BISTEN = LOW causes the Transmitter to switch to Encoded mode and begin sending the BIST pattern, as if MODE = LOW. When BISTEN returns to HIGH, the Transmitter resumes normal Bypass operation. In Test mode the BIST function works as in the Normal mode. For more information on BIST, consult the "HOTLink Built-In Self-Test" application note.

#### **Test Mode**

The MODE input pin selects between three transmitter functional modes. When wired to VCC, the  $D_{(a-j)}$  inputs bypass the Encoder and load directly from the Input register into the Shifter. When wired to GND, the inputs  $D_{0-7}$ , SVS, and SC/D are encoded using the Fibre Channel 8B/10B codes and sequences (shown at the end of this datasheet). Since the Transmitter is usually hard wired to Encoded or Bypass mode and not switched between them, a third function is provided for the MODE pin. Test mode is selected by floating the MODE pin (internal resistors hold the MODE pin at  $V_{CC}/2$ ). Test mode is used for factory or incoming device test.

Test mode causes the Transmitter to function in its Encoded mode, but with OutA+/OutB+ (used as a differential test clock input) as the bit rate clock input instead of the internal PLL-generated bit clock. In this mode, inputs are clocked by CKW and transfers between the Input register and Shifter are timed by the internal counters. The bit-clock and CKW must maintain a fixed phase and divide-by-ten ratio. The phase and pulse width of RP are controlled by phases of the bit counter (PLL feedback counter) as in Normal mode. Input and output patterns can be synchronized with internal logic by observing the state of RP or the device can be initialized to match an ATE test pattern using the following technique:

- 1. With the MODE pin either HIGH or LOW, stop CKW and bit-clock.

- 2. Force the MODE pin to MID (open or  $V_{\mbox{CC}}/2)$  while the clocks are stopped.

- 3. Start the bit-clock and let it run for at least two cycles.

- 4. Start the CKW clock at the bit-clock/10 rate.

Test mode is intended to allow logical, DC, and AC testing of the Transmitter without requiring that the tester check output data patterns at the bit rate, or accommodate the PLL lock, tracking, and frequency range characteristics that are required when the HOTLink part operates in its normal mode. To use OutA+/OutB+ as the test clock input, the FOTO input is held HIGH while in Test mode. This forces the two outputs to go to an "PECL LOW," which can be ignored while the test system creates a differential input signal at some higher voltage.

#### CY7B933 HOTLink Receiver Operating Mode Description

In normal user operation, the Receiver can operate in either of two modes. The Encoded mode allows a user system to send

and receive eight-bit data and control information without first converting it to transmission characters. The Bypass mode is used for systems in which the encoding and decoding is performed by an external protocol controller.

In either mode, serial data is received at one of the differential line receiver inputs and routed to the Shifter and the Clock Synchronization. The PLL in the Clock Synchronizer aligns the internally generated bit rate clock with the incoming data stream and clocks the data into the shifter. At the end of a byte time (ten bit times), the data accumulated in the shifter is transferred to the Decode register.

To properly align the incoming bit stream to the intended byte boundaries, the bit counter in the Clock Synchronizer must be initialized. The Framer logic block checks the incoming bit stream for the unique pattern that defines the byte boundaries. This combinatorial logic filter looks for the X3.230 symbol defined as "Special Character Comma" (K28.5). Once K28.5 is found, the free running bit counter in the Clock Synchronizer block is synchronously reset to its initial state, thus "framing" the data to the correct byte boundaries.

Since noise-induced errors can cause the incoming data to be corrupted, and since many combinations of error and legal data can create an alias K28.5, an option is included to disable resynchronization of the bit counter. The Framer will be inhibited when the RF input is held LOW. When RF rises, RDY will be inhibited until a K28.5 has been detected, and RDY will resume its normal function. Data will continue to flow through the Receiver while RDY is inhibited.

#### **Encoded Mode Operation**

In Encoded mode the serial input data is decoded\_into eight bits of data  $(Q_0 - Q_7)$ , a context control bit (SC/D), and a system diagnostic output bit (RVS). If the pattern in the Decode register is found in the Valid Data Characters table, the context of the data is decoded as normal message data and the SC/D output will be LOW. If the incoming bit pattern is found in the Valid Special Character Codes and Sequences table, it is interpreted as "control" or "protocol information," and the SC/D output will be HIGH. Special characters include all protocol characters defined for use in packets for Fibre Channel, ESCON, and other proprietary and diagnostic purposes.

The Violation symbol that can be explicitly sent as part of a user data packet (i.e., Transmitter sending C0.7;  $D_{7-0} = 111$  00000 and SC/D = 1; or SVS = 1) will be decoded and indicated in exactly the same way as a noise-induced error in the transmission link. This function will allow system diagnostics to evaluate the error in an unambiguous manner, and will not require any modification to the receiver data interface for error-testing purposes.

#### **Bypass Mode Operation**

In Bypass mode the serial input data is not decoded, and is transferred directly from the Decode register to the Output register's 10 bits ( $Q(a_{rj})$ ). It is assumed that the data has been preencoded prior to transmission, and will be decoded in subsequent logic external to HOTLink. This data can use any encoding method suitable to the designer. The only restrictions upon the data encoding method is that it contain suitable transition density for the Receiver PLL data synchronizer (one per 10 bit byte) and that it be compatible with the transmission media.

Document #: 38-02017 Rev. \*C 项目开发 芯片解密 零件配单 TEL:15013652265 QQ:38537442

The framer function in Bypass mode is identical to Encoded mode, so a K28.5 pattern can still be used to reframe the serial bit stream.

#### Parallel Output Function

The 10 outputs ( $Q_{0-7}$ , SC $\overline{D}$ , and RVS) all transition simultaneously, and are aligned with  $\overline{RDY}$  and CKR with timing allowances to interface directly with either an asynchronous FIFO or a clocked FIFO. Typical FIFO connections are shown in *Figure 4*.

Data outputs can be clocked into the system using either the rising or falling edge of CKR, or the rising or falling edge of RDY. If CKR is used, RDY can be used as an enable for the receiving logic. A LOW pulse on RDY shows that new data has been received and is ready to be delivered. The signal on RDY is a 60%-LOW duty cycle byte-rate pulse train suitable for the write pulse in asynchronous FIFOs such as the CY7C42X, or the enable write input on Clocked FIFOs such as the CY7C44X. HIGH on RDY shows that the received data appearing at the outputs is the null character (normally inserted by the transmitter as a pad between data inputs) and should be ignored.

When the Transmitter is disabled it will continuously send pad characters (K28.5). To assure that the receive FIFO will not be overfilled with these dummy bytes, the RDY pulse output is inhibited during fill strings. Data at the  $Q_{0-7}$  outputs will reflect the correct received data, but will not appear to change, since a string of K28.5s all are decoded as Q7-0 =000 00101 and SC/D = 1 (C5.0). When new data appears (not K28.5), the RDY output will resume normal function. The "last" K28.5 will be accompanied by a normal RDY pulse.

Fill characters are defined as any K28.5 <u>followed</u> by another K28.5. All fill characters will not cause RDY to pulse. Any K28.5 followed by any other character (including violation or illegal <u>characters</u>) will be interpreted as usable data and will cause RDY to pulse.

As noted above, RDY can also be used as an indication of correct framing of received data. While the Receiver is awaiting receipt of a K28.5 with RF HIGH, the RDY outputs will be inhibited. When RDY resumes, the received data will be properly framed and will be decoded correctly. In Bypass mode with RF HIGH, RDY will pulse once for each K28.5 received. For more information on the RDY pin, consult the "HOTLink CY7B933 RDY Pin Description" application note.

Code rule violations and reception errors will be indicated as follows:

#### RVS SC/D Qouts Name

1. Good Data code received with good running disparity (RD)0000-FFD0.0-31.7

| 2. Good Special Character code received with good RD      | 0 | 1 | 00-0E | 3 C0.0-11.0 |

|-----------------------------------------------------------|---|---|-------|-------------|

| 3. K28.7 immediately following<br>K28.1 (ESCON Connect_SC |   | 1 | 27    | C7.1        |

| 4. K28.7 immediately following<br>K28.5 (ESCON Passive_SC |   | 1 | 47    | C7.2        |

| 5. Unassigned code received                               | 1 | 1 | E0    | C0.7        |

| 6K28.5+ received when<br>RD was +                         | 1 | 1 | E1    | C1.7        |

| 7. +K28.5- received when<br>RD was -                      | 1 | 1 | E2    | C2.7        |

| 8. Good code received<br>with wrong RD                    | 1 | 1 | E4    | C4.7        |

#### **Receiver Serial Data Requirements**

The CY7B933 HOTLink Receiver serial input capability conforms to the requirements of the Fibre Channel specification. The serial data input is tracked by an internal PLL that is used to recover the clock phase and to extract the data from the serial bit stream. Jitter tolerance characteristics (including both PLL and logic component requirements) are shown below:

- Deterministic Jitter Tolerance (Dj) > 40% of tB. Typically measured while receiving data carried by a bandwidth-limited channel (e.g., a coaxial transmission line) while maintaining a Bit Error Rate (BER) < 10–12.</li>

- Random Jitter Tolerance (Rj) > 90% of tB. Typically measured while receiving data carried by a random-noise-limited channel (e.g., a fiber-optic transmission system with low light levels) while maintaining a Bit Error Rate (BER) < 10–12.</li>

- Total Jitter Tolerance > 90% of tB. Total of Dj + Rj.

- PLL-Acquisition Time < 500-bit times from worst-case phase or frequency change in the serial input data stream, to receiving data within BER objective of 10-12. Stable power supplies within specifications, stable REFCLK input frequency and normal data framing protocols are assumed. Note: Acquisition time is measured from worst-case phase or frequency change to zero phase and frequency error. As a result of the receiver's wide jitter tolerance, valid data will appear at the receiver's outputs a few byte times after a worst-case phase change.

Document #: 38-02017 Rev. \*C

Page 14 of 30

The CY7B933 Receiver offers two types of test mode operation, BIST mode and Test mode. In a normal system application, the Built-In Self-Test (BIST) mode can be used to check the functionality of the Transmitter, the Receiver and the link connecting them. This mode is available with minimal impact on user system logic, and can be used as part of the normal system diagnostics. Typical connections and timing are shown in *Figure 6*.

#### **BIST Mode**

BIST Mode function is as follows:

- 1. <u>Set BISTEN</u> LOW to enable self-test generation and await RDY LOW indicating that the initialization code has been received.

- 2. Monitor RVS and check for an<u>y byte</u> time with the pin HIGH to detect pattern mismatches. RDY will pulse HIGH once per BIST loop, and can be used by an external counter to monitor test pattern progress.  $Q_{0-7}$  and SC/D will show the expected pattern and may be useful for debug purposes.

- 3. When testing is completed, set BISTEN HIGH and resume normal function.

**Note**: A specific test of the RVS output may be required to assure an adequate test. To perform this test, it is only necessary to have the Transmitter send violation (SVS = HIGH) for a few bytes before beginning the BIST test sequence. Alternatively, the Receiver could enter BIST mode after the Transmitter has begun sending BIST loop data, or be removed before the Transmitter finishes sending BIST loops, each of which contain several deliberate violations and should cause RVS to pulse HIGH.

BIST mode is intended to check the entire function of the Transmitter, serial link, and Receiver. It augments normal factory ATE testing and provides the user system with a rigorous test mechanism to check the link transmission system, without requiring any significant system overhead.

When in Bypass mode, the BIST logic will function in <u>the same</u> way as in the Encoded mode. MODE = HIGH and BISTEN = LOW causes the Receiver to switch to Encoded mode and begin checking the decoded <u>received</u> data of the BIST pattern, as if MODE = LOW. When BISTEN returns to HIGH, the Receiver resumes normal Bypass operation. In Test mode the BIST function works as in the normal mode.

#### **Test Mode**

The MODE input pin selects between three receiver functional modes. When wired to VCC, the Shifter contents bypass the Decoder and go directly from the Decoder latch to the  $Q_{a-j}$  inputs of the Output latch. When wired to GND, the outputs are decoded using the 8B/10B codes shown at the end of this datasheet and become  $Q_{0-7}$ , RVS, and SC/D. The third function is Test mode, used for factory or incoming device test. This mode can be selected by leaving the MODE pin open (internal circuitry forces the open pin to VCC/2).

Test mode causes the Receiver to function in its Encoded mode, but with INB (INB+) as the bit rate Test clock instead of the Internal PLL generated bit clock. In this mode, transfers between the Shifter, Decoder register and Output register are controlled by their normal logic, but with an external bit rate clock instead of the PLL (the recovered bit clock). Internal logic and test pattern inputs can be synchronized by sending a SYNC pattern and allowing the Framer to align the logic to the bit stream. The flow is as follows:

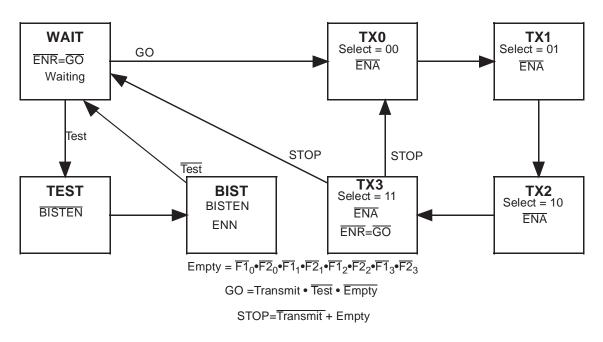

CY7B923 CY7B933

- 1. Assert Test mode for several test clock cycles to establish normal counter sequence.

- 2. Assert RF to enable reframing.

- 3. Input a repeating sequence of bits representing K28.5 (Sync).

- 4. RDY falling shows the byte boundary established by the K28.5 input pattern.

- 5. Proceed with pattern, voltage and timing tests as is convenient for the test program and tester to be used.

(While in Test mode and in BIST mode with RF HIGH, the  $Q_{0-7}$ , RVS, and SC/D outputs reflect various internal logic states and not the received data.)

Test mode is intended to allow logical, DC, and AC testing of the Receiver without requiring that the tester generate input data at the bit rate or accommodate the PLL lock, tracking and frequency range characteristics that are required when the part operates in its normal mode.

#### X3.230 Codes and Notation Conventions

Information to be transmitted over a serial link is encoded eight bits at a time into a 10-bit Transmission Character and then sent serially, bit by bit. Information received over a serial link is collected ten bits at a time, and those Transmission Characters that are used for data (Data Characters) are decoded into the correct eight-bit codes. The 10-bit Transmission Code supports all 256 8-bit combinations. Some of the remaining Transmission Characters (Special Characters) are used for functions other than data transmission.

The primary rationale for use of a Transmission Code is to improve the transmission characteristics of a serial link. The encoding defined by the Transmission Code ensures that sufficient transitions are present in the serial bit stream to make clock recovery possible at the Receiver. Such encoding also greatly increases the likelihood of detecting any single or multiple bit errors that may occur during transmission and reception of information. In addition, some Special Characters of the Transmission Code selected by Fibre Channel Standard consist of a distinct and easily recognizable bit pattern (the Special Character Comma) that assists a Receiver in achieving word alignment on the incoming bit stream.

#### **Notation Conventions**

The documentation for the 8B/10B Transmission Code uses letter notation for the bits in an 8-bit byte. Fibre Channel Standard notation uses a bit notation of A, B, C, D, E, F, G, H for the 8-bit byte for the raw 8-bit data, and the letters a, b, c, d, e, i, f, g, h, j for encoded 10-bit data. There is a correspondence between bit A and bit a, B and b, C and c, D and d, E and e, F and f, G and g, and H and h. Bits i and j are derived, respectively, from (A,B,C,D,E) and (F,G,H).

The bit labeled A in the description of the 8B/10B Transmission Code corresponds to bit 0 in the numbering scheme of the FC-2 specification, B corresponds to bit 1, as shown below.

| FC-2 bit designation—    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------------------------|---|---|---|---|---|---|---|---|

| HOTLink D/Q designation- | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 8B/10B bit designation—  | Н | G | F | Е | D | С | В | А |

Document #: 38-02017 Rev. \*C 项目开发 芯片解密 零件配单 TEL:15013652265 QQ:38537442

Page 15 of 30

Data Byte Name

To clarify this correspondence, the following example shows the conversion from an FC-2 Valid Data Byte to a Transmission Character (using 8B/10B Transmission Code notation)

> FC-2 45 Bits: <u>7654</u> <u>3210</u> 0100 0101

Converted to 8B/10B notation (note carefully that the order of bits is reversed):

D5.2 Bits:<u>ABCDEFGH</u> 10100 010

Translated to a transmission Character in the 8B/10B Transmission Code:

#### Bits: <u>abcdeifghj</u> 1010010101