#### ●新特器件应用

# 嵌入式语音识别处理器 ISD - SR3000 的特性及应用

南华大学电气工程学院 张允 黄智伟

### Characteristic and Application of Embedded Speech Recognition Processor ISD – SR3000

Zhang Yun Huang Zhiwei

摘要:ISD - SR3000 是 Winbond 公司推出的新型嵌入式语音识别处理器,它由语音识别引擎、语音压缩引擎和录音功能组成。并带有最优指令系统为核心的 PISC/PSP、灵活的 CODEC 接口和串行主控制器接口,文中介绍了 ISD - SR3000 的特点、引脚排列和功能。给出了一个用 SR3000 组成的语音识别系统电路。

关键词:语音识别; 微处理器; CODEC; SR3000

分类号:TN912.34 文献标识码:B 文章编号:1006-6977(2002)01-0025-03

1 概述

ISD - SR3000 是 Winbond 公司推出的新型嵌入 式语音识别处理器,它由语音识别引擎、语音压缩引 擎和录音功能部分组成。芯片内包含一个以最优指 令系统为核心的并行 PISC/ DSP、灵活的 CODEC 接 口和一个串行主控制器接口。

ISD - SR3000 中的语音识别引擎使用成熟的 Hidden Markov 模型 (HMMS),因而能够识别连续的 语音信号,并可与数字信号相连。同时可以由用户 选择单语音用户命令、连接数字信号命令和定义说 话者命令。

定义说话者命令允许用户分类和辨识声音标签。声音标签可作为用户命令或进行姓名目录管理。单用户命令、语音提示符和被定义的说话者的声音标签可储存在外部存储器中。

该芯片可支持单语音用户连续输入语音,并支持用户定义的语音标签,还可为特性抽取和实时音质模型查找提供最优化的识别引擎。该芯片提供有μ律、A 律或线形 CODEC 接口以及到主控制器的串行接口。在 3.3~5V 供电时,其语音识别的电流为40mA,而在低功耗模式时仅为 12mA。SR3000 语音识别处理器可广泛应用在可存储的仪器仪表、自动化控制系统、无线电话、蜂窝电话、家庭网络、英特网设备等系统。

### 2 ISD - SR3000 的引脚功能

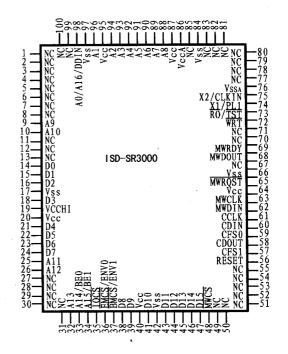

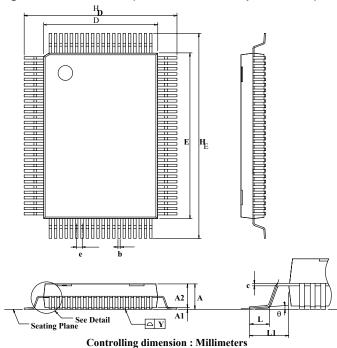

ISD - SR3000 采用 100 引脚 QFP 封装,其引脚分布如图 1 所示,各引脚功能如表 1 所列。

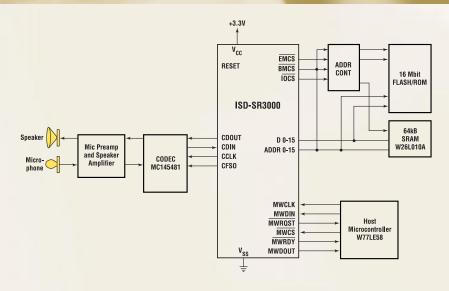

### 3 基于 SR3000 的语音识别系统

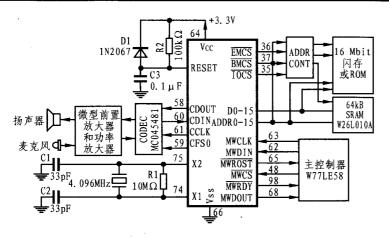

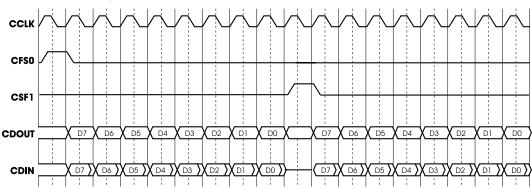

由 ISD - SR3000 构成的语音识别系统电路如图

图 1 ISD - SR3000 的引脚分布图

图 2 语音识别系统框图

2 所示。以下分别介绍电路中各部分的功能。

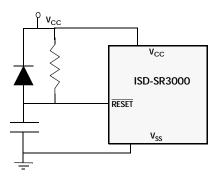

#### 3.1 复位

RESET 端为芯片复位端。加电时 RESET 必须保持在低电平,时间至少应持续 30ms。TST 端必须利用上拉电阻以便其处于高电平状态。MWRDY 端的值

在复位期间没有定义。但在复位 100ms 后,微处理器将首先等待这个信号或者 在这期间此信号被拉高。

在复位时,电路将对 ENV0 和 ENV1 的输入端进行采样以决定操作环境。而  $\overline{EMCS}$  / ENV0 和  $\overline{BMCS}$  / ENV1 端则在复位时用来决定 ENV0 和 ENV1 输入信号。利用芯片内的上拉电阻可将 ENV0 和 ENV1 置 1。而利用一个连接于  $V_{ss}$  端上的 5.1k $\Omega$  的外接电阻则可对 ENV0 和 ENV1 置 0。

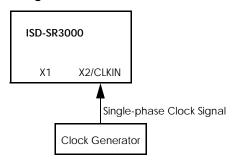

#### 3.2 时钟

SR3000 内含片内振荡器,但应用时也可通过 X1 和 X2/ CLKIN 端的外接晶振或外部时钟源来产生时钟信号。外部时钟源信号应通过 X2/CLKIN 端输入。要注意的是,外部时钟源电平与CLKIN 的输入电平要相符(3.3V 或 5V)。

| 表 1 ISD - SR3000 引脚信号排列说明 |                    |       |               |  |  |  |  |

|---------------------------|--------------------|-------|---------------|--|--|--|--|

| 引脚名称                      | 信号名称               | 信号类型  | 说明            |  |  |  |  |

| A(0:15)                   | A(0:16)            | 输出    | 0 到 16 的地址位   |  |  |  |  |

| CCLK                      | CCLK               | 输入/输出 | CODEC 主从时钟接口  |  |  |  |  |

| BMCS                      | BMCS               | 输出    | 基存储器芯片选择 **   |  |  |  |  |

| BMCS/ENV1                 | BMCS               | 输入/输出 | 基存储器芯片选择或环境选择 |  |  |  |  |

| CDIN                      | CDIN               | 输入    | 从 CODEC 数据输入  |  |  |  |  |

| CDOUT                     | CDOUT              | 输出    | 从 CODEC 数据输出  |  |  |  |  |

| CFS0                      | CFS0               | 输入/输出 | CODECO 帧同步    |  |  |  |  |

| CFS1                      | CFS1               | 输出    | CODEC1 帧同步    |  |  |  |  |

| D(0:7)                    | D(0:7)             | 输入/输出 | 0到7的数据位       |  |  |  |  |

| EMCS/ENV0                 | EMCS               | 输出    | 扩充存储器芯片选择     |  |  |  |  |

| EMCS/ENV0                 | ENV0               | 输入    | 环境选择          |  |  |  |  |

| MWCLK                     | MWCLK              | 输入    | 与微处理器连接的时钟    |  |  |  |  |

| MWCS                      | MWCS               | 输入    | 与微处理器连接的芯片选择  |  |  |  |  |

| MWDIN                     | MWDIN              | 输入    | 与微处理器连接的数据输入  |  |  |  |  |

| MWDOUT                    | MWDOUT             | 输出    | 与微处理器连接的数据输出  |  |  |  |  |

| MWRDY                     | MWRDY              | 输出    | 微处理器准备信号      |  |  |  |  |

| MWRQST                    | MWRQST             | 输出    | 微处理器请求信号      |  |  |  |  |

| RESET                     | RESET              | 输入    | 复位            |  |  |  |  |

| TST                       | TST                | 输入    | 测试脚           |  |  |  |  |

| V <sub>CC</sub>           | $v_{cc}$           | 电源    | 3.3V 电源引脚     |  |  |  |  |

| V <sub>CC</sub> A         | V <sub>CC</sub> A  | 电源    | 3.3V 模拟电源引脚   |  |  |  |  |

| V <sub>CC</sub> HI        | V <sub>CC</sub> HI | 电源    | 5V 电源引脚       |  |  |  |  |

| $V_{SS}$                  | $ m V_{SS}$        | 电源    | 片内逻辑和输出驱动器地   |  |  |  |  |

| V <sub>SS</sub> A         | V <sub>SS</sub> A  | 电源    | 片内模拟电路地       |  |  |  |  |

| X1                        | X1                 | 振荡器   | 晶振接口 '        |  |  |  |  |

| X2/CLKIN                  | X2                 | 振荡器   | 晶振接口          |  |  |  |  |

表 1 ISD - SR3000 引脚信号排列说明

口使用的 5 个信号分别为 CDIN、CDOUT、CCLK、CFS0 和 CSF1。其中 CDIN、CDOUT、CCLK 和 CFS0 被连接到第一个 CODEC。CDIN、CDOUT、CCLK 和 CFS1 被连接—到第二个 CODEC 接口。数据通过 CDOUT 输出端传送给 CODEC 接口,并通过 CDIN 输入端从 CODEC 读出。CCLK 和 CFS0 端在主模式下为输出状态,而在从模式下为输入状态。CFS1 是一个输出端。SR3000 支

持的典型 CODEC 器件见表 3 所列。

#### 参考文献

1. Winbond. ISD – SR3000 Embedded Speech Recogni – tion Processor .www.isd.com,2001.5

收稿日期:2001-06-04

咨询编号:020110

表 3 SR3000 支持的典型的 CODEC 器件

| 生产商                    | CODEC 设备名称 | 特征      | 工作电压 | 转换类型  |

|------------------------|------------|---------|------|-------|

| National Semiconductor | TP3054     | 单 CODEC | 5V   | μ律    |

| OKI                    | MSM7533V   | 双 CODEC | 5 V  | μ律,A律 |

| Macronix               | MX93002FC  | 双 CODEC | 5V   | μ律    |

| Lucent                 | T7503      | 双 CODEC | 5 V  | μ律    |

| Motorola               | MC145481   | 单 CODEC | 3 V  | μ律    |

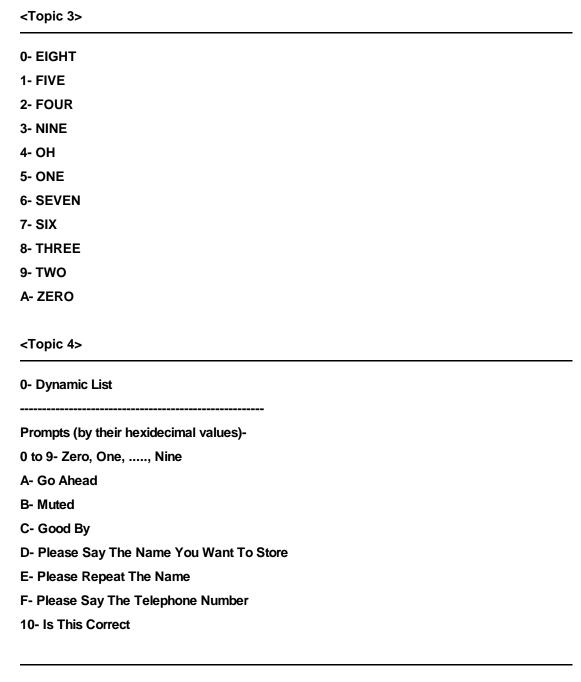

# ISD-SR3000

## **Embedded Speech Recognition Processor**

Advanced Information =

# EMBEDDED SPEECH RECOGNITION PROCESSOR FOR COMMAND AND CONTROL APPLICATIONS

The ISD-SR3000 is a complete embedded speech recognition processor. It consists of a speech recognition engine, a speech compression engine, and a recording function. The ISD-SR3000 hardware includes a parallel PISC/DSP core with an optimized instruction set, a flexible CODEC interface, and a serial host controller interface.

The speech recognition engine uses sophisticated Hidden Markov Models (HMMs), which enables recognition of continuous speech and connected digits. An application consists of speaker-independent commands (chosen by the application developer), connected digits and speaker-defined commands. The speaker-defined commands allow users to sore and recognize voicetags that can be used for custom commands or name list management. The speaker-defined commands use the HMMs, providing much more robust performance compared to conventional speaker-dependent commands.

The speaker-independent commands, the audio prompts, and the speaker-defined voicetags are stored in external memory, allowing for maximum application flexibility. Typical storage requirements are 2kB for each predefined command, 2.5kB for each audio prompt, and 3kB for each voicetag, including the model, recording, and data. Application commands are divided into topics (menus), with active vocabulary size governed by the size of the external SRAM. A development system, the ISD-DS3000, is available. The development system includes tools for compiling and sizing commands and prompts, as well as sample C-code for host control program development.

#### **IDEAL EMBEDDED SPEECH APPLICATIONS**

- Accessible appliances

- Desktop phones

- Home automation

- Cordless phones

- Information kiosks

- Automotive command and control

- Cellular car kits

- Cellular handsets

- Instrumentation control

- Internet appliances

IMPORTANT NOTICE: This product concept and specifications are preliminary and subject to change without notice. Please contact ISD before using this information in any product design.

September 2000

#### **ISD-SR3000 PRODUCT FEATURES**

#### **Speech Recognition Attributes**

- Speech recognition processor optimized for command and control applications

- All speech recognition processing performed on chip

- · Supports speaker-independent continuous speech

- Command vocabulary selected from a large (>100k word) dictionary

- Number of commands and voicetags determined by external memory availability

- Multiple topics and finite state grammar supported

- Connected digit recognition with no domain restrictions

#### Supports speaker defined voicetags

- Phonetic models of user speech input created "on the fly"

- More robust than typical speaker-dependent word models

- Used for phone books and customized commands

- Recognition always active

- Allows for voice activation with keyword command

- Push-to-talk option for battery applications

- Zero power voicetag storage

- Hidden Markov Models and triphones used to optimize accuracy while maintaining real-time recognition

#### **Recognition Processor Attributes**

- · Recognition engine optimized for feature extraction and real-time acoustic model search

- Interfaces to µ-Law, A-Law or linear voice CODEC

- Serial interface to host microcontroller

- Single +5V or +3.3V power supply

- Current: 40mA (typical) during active recognition

- Package: 100-pin QFP

- Temperature range: 0 to +70°C

#### **Application Attributes**

- · Advanced API enables sophisticated VUI development

- True hands-free control

- Optional activation by voice

- Standard, easy to use interface for voice activated appliances

- Minimizes adaptation time for users

- Accelerated application development by providing standard interface software

- · Flexible API provides high level commands suitable for a wide variety of applications

- Measure accuracy >99% per digit for connected digit strings

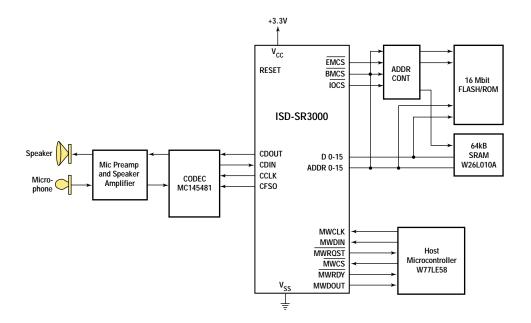

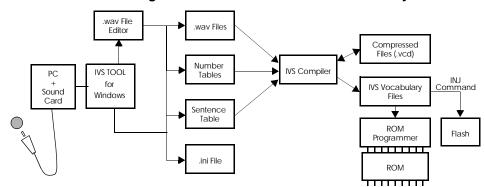

Figure i: Stand-alone Speech Recognition System Diagram

# Table of Contents

| Chap            | ter 1– | -HARDWARE1-1                         |

|-----------------|--------|--------------------------------------|

| 1.1             | PIN AS | SSIGNMENT1-1                         |

|                 | 1.1.1  | Pin-Signal Assignment1-1             |

| 1.2             | DESCI  | RIPTION                              |

|                 | 1.2.1  | Resetting                            |

|                 | 1.2.2  | Clocking                             |

|                 | 1.2.3  | Power-Down Mode1-5                   |

|                 | 1.2.4  | Power and Grounding                  |

|                 | 1.2.5  | Memory Interface1-7                  |

|                 | 1.2.6  | The Codec Interface                  |

|                 | 1.2.7  | Expansion Memory Addressing1-11      |

| 1.3             | SPECI  | FICATIONS                            |

|                 | 1.3.1  | Absolute Maximum Ratings1-19         |

|                 | 1.3.2  | Electrical Characteristics           |

|                 | 1.3.3  | Switching Characteristics1-21        |

|                 | 1.3.4  | Synchronous Timing Tables            |

|                 | 1.3.5  | Timing Diagrams                      |

| Chap <b>2.1</b> |        | -SOFTWARE                            |

| 2.1             |        |                                      |

| 2.2             | RECO   | GNITION ENGINE2-2                    |

|                 | 2.2.1  | Types of Recognition2-2              |

|                 | 2.2.2  | Grammar                              |

|                 | 2.2.3  | Vocabulary2-3                        |

|                 | 2.2.4  | Language                             |

|                 | 2.2.5  | Additional Components2-4             |

| 2.3             | INITIA | LIZATION2-4                          |

| 2.4             | RECO   | ENGINE MANAGEMENT2-4                 |

| 2.5             | HOST   | CONTROLLER INTERFACE2-5              |

|                 | 2.5.1  | Input Signals                        |

|                 | 2.5.2  | Output Signals                       |

|                 | 2.5.3  | Signal Use in the Interface Protocol |

|                 | 2.5.4  | Interface Protocol Error Handling    |

|                 | 2.5.5  | Echo Mechanism                       |

|                 |        |                                      |

# 电子工程师之家http://www.eehome.cn

#### ISD-SR3000

| 2.6  | MEMORY INTERFACE                                            | 2-9            |

|------|-------------------------------------------------------------|----------------|

| 2.7  | CODEC INTERFACE                                             | 2-9            |

|      | 2.7.1 Supported Functionality                               | 2-9            |

| 2.8  | SPEECH OUTPUT                                               | 2-9            |

|      | 2.8.1 International Vocabulary Support                      | . 2-10         |

|      | 2.8.2 Vocabulary Design                                     | . 2-10         |

|      | 2.8.3 IVS Vocabulary Components                             | . <b>2-1</b> 1 |

| 2.9  | THE STATE MACHINE                                           | . <b>2-1</b> 3 |

|      | 2.9.1 Command Execution                                     | . 2-14         |

|      | 2.9.2 Synchronous Commands                                  | . <b>2-1</b> 4 |

|      | 2.9.3 Asynchronous Commands                                 | . 2-14         |

|      | 2.9.4 ISD-SR3000 Status and Registers                       | . 2-15         |

| 2.10 | SR3000 PROCESSOR COMMANDSQUICK REFERENCE TABLE              | . 2-16         |

| 2.11 | COMMAND DESCRIPTION                                         | . 2-20         |

| 2.12 | TUNABLE PARAMETERS                                          | . <b>2-6</b> 4 |

| 2.13 | EXAMPLE OPERATION PROCEDURES                                | . 2-68         |

|      | 2.13.1 ISD-SR3000 Initialization                            | . 2-68         |

|      | 2.13.2 Normal Operation Procedures                          | . 2-68         |

|      | 2.13.3 Add Voice Tag Procedure                              |                |

| Chap | ter 3—International Vocabulary Support and the IVS Tool .   | . 3-1          |

| 3.1  | INTERNATIONAL VOCABULARY SUPPORT (IVS)                      | 3-1            |

| 3.2  | IVS FEATURES                                                | 3_1            |

| 3.2  | WOTERTORES.                                                 | , . J-1        |

| 3.3  | THE IVS TOOL                                                |                |

|      | 3.3.1 How to use the IVS Tool with the ISD-SR3000 Processor | 3-2            |

| Chap | ter 4—Glossary                                              | . 4-1          |

|      | EDDOD CODES AND EVEL ANATIONS                               |                |

| A 1  | LUUNU MANILE ARIILEVUI ARIA HARIE                           | л ·            |

### Chapter 1—Hardware

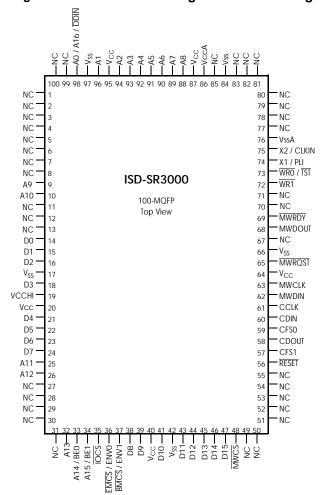

#### 1.1 PIN ASSIGNMENT

The following sections detail the pins of the ISD-SR3000 processor. Slashes separate the names of signals that share the same pin.

#### 1.1.1 PIN-SIGNAL ASSIGNMENT

Table 1-1 shows all the pins and the signals that use them in different configurations. It also shows the type and direction of each signal.

Figure 1-1: 100-MQFP Package Connection Diagram

**Note**: Pins marked NC should not be connected.

Table 1-1: ISD-SR3000 Pin Signal Assignment

| Pin Name           | Signal Name        | Туре                | Description                                                                     |

|--------------------|--------------------|---------------------|---------------------------------------------------------------------------------|

| A(0:15)            | A(0:16)            | Output              | Address bits 0 through 16                                                       |

| CCLK               | CCLK               | I/O                 | Codec Master/slave Clock                                                        |

| BMCS               | BMCS               | Output              | Base memory chip select                                                         |

| BMCS/              | BMCS               | I/O                 | Base memory chip select                                                         |

| ENV1               |                    |                     | Environment Select                                                              |

| CDIN               | CDIN               | Input               | Data Input from Codec                                                           |

| CDOUT              | CDOUT              | Output              | Data Output to Codec                                                            |

| CFS0               | CFS0               | 1/0                 | Codec 0 Frame Synchronization                                                   |

| CFS1               | CFS1               | Output              | Codec 1 Frame Synchronization                                                   |

| D(0:7)             | D(0:7)             | 1/0                 | Data bits 0 through 7                                                           |

| EMCS/<br>ENV0      | EMCS               | Output <sup>2</sup> | Expansion Memory Chip Select                                                    |

| EMCS/<br>ENV0      | ENV0               | Input <sup>1</sup>  | Environment Select                                                              |

| MWCLK              | MWCLK              | Input <sup>3</sup>  | MICROWIRE Clock                                                                 |

| MWCS               | MWCS               | Input <sup>3</sup>  | MICROWIRE Chip Select                                                           |

| MWDIN              | MWDIN              | Input <sup>3</sup>  | MICROWIRE Data Input                                                            |

| MWDOUT             | MWDOUT             | Output              | MICROWIRE DATA Output                                                           |

| MWRDY              | MWRDY              | Output              | MICROWIRE Ready                                                                 |

| MWRQST             | MWRQST             | Output              | MICROWIRE Request Signal                                                        |

| RESET              | RESET              | Input <sup>3</sup>  | Reset                                                                           |

| TST                | TST                | Input               | Test pin                                                                        |

| V <sub>CC</sub>    | V <sub>CC</sub>    | Power               | 3.3 V power supply pin                                                          |

| V <sub>CC</sub> A  | V <sub>CC</sub> A  | Power               | 3.3 V analog circuitry power supply pin                                         |

| V <sub>CC</sub> HI | V <sub>CC</sub> HI | Power               | 5 V power supply pin. Connect to V <sub>CC</sub> if 3.3 V power supply is used. |

| V <sub>SS</sub>    | V <sub>SS</sub>    | Power               | Ground for on-chip logic and output drivers                                     |

| V <sub>SS</sub> A  | V <sub>SS</sub> A  | Power               | Ground for on-chip analog circuitry                                             |

| X1                 | X1                 | Oscillator          | Crystal Oscillator Interface                                                    |

| X2/CLKIN           | X2                 | Oscillator          | Crystal Oscillator Interface                                                    |

<sup>1.</sup> TIL1 output signals provide CMOS levels in the steady state, for small loads.

<sup>2.</sup> Input during reset. CMOS level input.

<sup>3.</sup> Schmitt trigger input.

#### 1.2 DESCRIPTION

This section provides details of the functional characteristics of the ISD-SR3000 processor. It is divided into the following sections:

- Resetting

- Clocking

- Power-Down Mode

- Power and Grounding

- Memory Interface

- Codec Interface

#### 1.2.1 RESETTING

The RESET pin is used to reset the ISD-SR3000 processor.

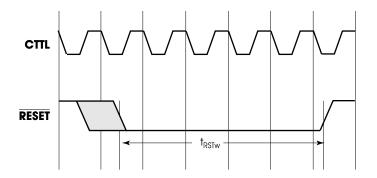

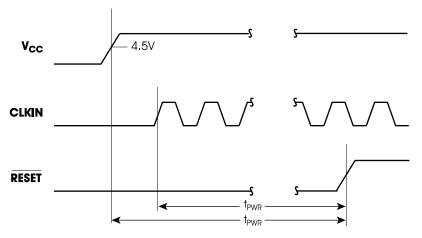

On application of power, RESET must be held low for at least  $t_{pwr}$  after  $V_{CC}$  is stable. This ensures that all on-chip voltages are completely stable before operation. Whenever RESET is applied, it must also remain active for not less than  $t_{RST}$ , see Table 1-11 and Table 1-12. During this period, and for 100 ms after, the  $\overline{TST}$  signal must be high. This can be done with a pull-up resistor on the  $\overline{TST}$  pins

The value of MWRDY is undefined during the reset period, and for 100 ms after. The microcontroller should either wait before polling the signal for the first time, or the signal should be pulled high during this period.

Upon reset, the ENV0 and ENV1 input pins are sampled to determine the operating environment. During reset, the EMCS/ENV0 and BMCS/ENV1 pins are used for the ENV0 and ENV1 inputs signals respectively. An internal pull-up resistor sets ENV0 and ENV1 to 1. An external 5.1k  $\Omega$  resistor connected to V<sub>ss</sub> can be used to set them to 0.

After reset, the same pin is used for EMCS.

#### SYSTEM LOAD ON ENVO

For any load on the ENV0 pin, the voltage should not drop below V<sub>ENVh</sub>. Therefore, apply a load on the ENV0 pin that ensures the voltage does not go below 2.4V.

Figure 1-2 shows a recommended circuit for generating a reset signal when the power is turned on.

Figure 1-2: Recommended Power-On Reset Circuit

#### 1.2.2 CLOCKING

The ISD-SR3000 processor provides an internal oscillator that interacts with an external clock source through the X1 and X2/CLKIN pins. Either an external single-phase clock signal or a crystal oscillator may be used as the clock source.

#### EXTERNAL SINGLE-PHASE CLOCK SIGNAL

If an external single-phase clock source is used, it should be connected to the CLKIN signal as shown in Figure 1-3, and should conform to the voltage-level requirements for CLKIN stated in "Electrical Characteristics" on page 1-19.

Note: the CLKIN signal is not 5V tolerant.

Figure 1-3:External Clock Source

#### **CRYSTAL OSCILLATOR**

A crystal oscillator is connected to the on-chip oscillator circuit via the X1 and X2 signals, as shown in Figure 1-4.

Figure 1-4:Connections for an External Crystal Oscillator

Keep stray capacitance and inductance, in the oscillator circuit, as low as possible. The crystal resonator, and the external components, should be as close to the X1 and X2/CLKIN pins as possible, to keep the trace lengths in the printed circuit to an absolute minimum.

You can use crystal oscillators with maximum load capacitance of 20pF, although the oscillation frequency may differ from the crystal's specified value.

The following table lists the components in the crystal oscillator circuit.

Table 1-2: Components of Crystal Oscillator Circuit

| Component         | Values       | Tolerance |

|-------------------|--------------|-----------|

| Crystal Resonator | 4.096MHz     |           |

| Resistor R1       | <b>10M</b> Ω | 5%        |

| Capacitors C1, C2 | 33pF         | 20%       |

#### 1.2.3 POWER-DOWN MODE

Power-down mode is useful during a power failure or in a power-saving model when the power source for the processor is a backup battery or in battery-powered devices, while the processor is in idle mode.

In power-down mode, the clock frequency of the ISD-SR3000 processor is reduced and some of the processor modules are deactivated. As a result, the ISD-SR3000 consumes considerably less power than in normal-power mode. Recognition is not active during power-down mode, so the ISD-SR3000 must return to normal power mode to resume speech recognition.

**Note**: In power-down mode all the chip select signals, CS0 to CS3, are set to 1. To guarantee that there is no current flow from these signals to the Flash devices, the power supply to these devices must not be disconnected.

The ISD-SR3000 stores voicetags and all memory management information in Flash memory. When Flash memory is used for memory management, power does not need to be maintained to the processor to preserve stored voicetags.

To keep power consumption low during power-down mode, the  $\overline{RESET}$ ,  $\overline{MWCS}$ , MWCLK and MWDIN signals should be held above  $V_{CC} = 0.5$  V or below  $V_{SS} + 0.5$  V.

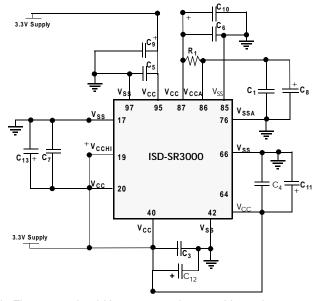

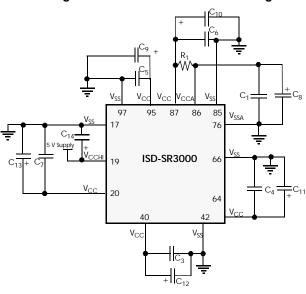

#### 1.2.4 POWER AND GROUNDING

#### **POWER PIN CONNECTIONS**

The ISD-SR3000 can operate over two supply voltage ranges 3.3V  $\pm 10\%$  and 5V  $\pm 10\%$ . The five power supply pins (V<sub>CC</sub>, V<sub>SS</sub>, V<sub>CC</sub>A, V<sub>SS</sub>A and V<sub>CC</sub>HI) must be connected as shown in Figure 1-5 when operating in a 3.3 V environment, and as shown in Figure 1-6 when operating in a 5V environment. Failure to correctly connect the pins may result in damage to the device.

The capacitor and resistor values are given in Table 1-3.

| 1                                          |                  |           |  |  |  |  |  |

|--------------------------------------------|------------------|-----------|--|--|--|--|--|

| Component                                  | Values           | Tolerance |  |  |  |  |  |

| Resistor R1                                | 10Ω              | 5%        |  |  |  |  |  |

| Capacitors C1, C2, C3, C4, C5, C6, C7      | 0.1µF<br>Ceramic | 20%       |  |  |  |  |  |

| Capacitors C8, C9, C10, C11, C12, C13, C14 | 1μF Tantalum     | 20%       |  |  |  |  |  |

Table 1-3: Components of Supply Circuit

Figure 1-5: 3. 3V Power Connection Diagram

**Note**: all Vcc pins in Figure 1-5 should be connected to a 3.3V supply

Figure 1-6: 5V Power Connection Diagram

For optimal noise immunity, the power and ground pins should be connected to  $V_{CC}$  and the ground planes, respectively, on the printed circuit board. If  $V_{CC}$  and the ground planes are not used, single conductors should be run directly from each  $V_{CC}$  pin to a power point, and from each GND pin to a ground point. Avoid daisy-chained connections. The ISD-SR3000 does not perform recognition in power-down mode.

When you build a prototype, using wire-wrap or other methods, solder the capacitors directly to the power pins of the ISD-SR3000 processor socket, or as close as possible, with very short leads.

#### 1.2.5 MEMORY INTERFACE

The ISD-SR3000 supports flash or ROM devices for storing voicetags, vocabulary, prompts, and acoustic models, such that power can be removed from the system without any data loss. The ISD-SR3000 supports AMD-compatible parallel flash devices, depending upon the required amount of memory. The recommended flash size is 16Mb, but larger sizes may be required for some applications. Organization can be 1Mb X 16 or 2Mb X 8. The recommended device is Am29LV160D, which is organized as 1Mb X 16, and operates on a 3V power supply.

#### 1.2.6 THE CODEC INTERFACE

The ISD-SR3000 provides an on-chip interface for analog and digital telephony, supporting master and slave CODEC interface modes. In master mode, the ISD-SR3000 controls the operation of the CODEC for use in analog telephony or stand-alone applications. In the slave mode, the ISD-SR3000 CODEC interface is controlled by an external source. This mode is

used in digital telephony (i.e., ISDN or DECT lines). The slave mode is implemented with respect to IOM-2<sup>TM</sup>/CGI specifications.

See Table 1-4 for CODEC options for the ISD-SR3000 (ISD supports compatible CODECS in addition to those listed below).

The CODEC interface supports the following features:

- · Master Mode or Slave Mode.

- 8- or 16-bit channel width.

- Long (variable) or short (fixed) frame protocol.

- Single or double bit clock rate.

- Single or dual channel CODECS

- One or two CODECS

- Multiple clock and sample rates.

- One or two frame sync signals

This CODEC interface uses five signals: CDIN, CDOUT, CCLK, CFSO, and CFS1. The CDIN, CDOUT, CCLK, and CFSO pins are connected to the first CODEC. The second CODEC (for speakerphone applications) is connected to CDIN, CDOUT, CCLK, and CFS1 pins. Data is transferred to the CODEC (for speakerphone applications) through the CDOUT output pin. Data is read from the CODEC through the CDIN input pin. The CCLK and CFSO pins are output in Master mode and input in Slave mode. The CFS1 is an output pin.

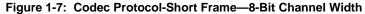

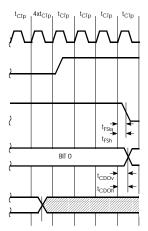

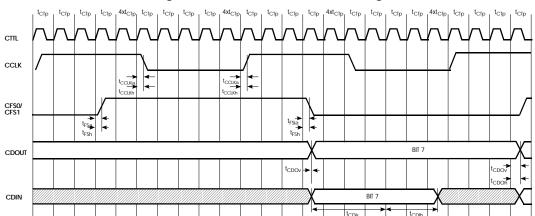

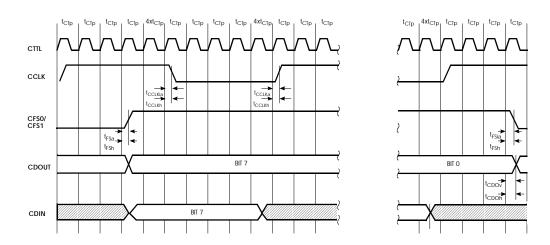

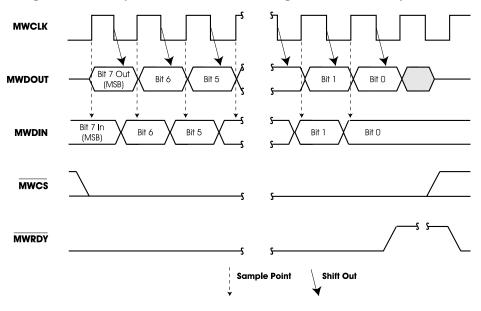

#### SHORT FRAME PROTOCOL

When the short frame protocol is configured, eight or sixteen data bits are exchanged with each CODEC in each frame (i.e., the CFSO cycle). Data transfer begins when CFSO is set to 1 for one CCLK cycle. The data is then transmitted, bit by bit, via the CDOUT pin. Concurrently, the received data is shifted in through the CDIN pin. Data is shifted one bit per CCLK cycle. After the last bit has been shifted, CFS1 is set to 1 for one CCLK cycle. Then, the data from the second CODEC is shifted out via CDOUT, concurrently with the inward shift of the data received via CDIN.

#### LONG FRAME PROTOCOL

When long frame protocol is configured, eight or sixteen data bits are exchanged with each CO-DEC, as for the short frame protocol. However, for the long frame protocol, data transfer starts by setting CFSO to 1 for eight or sixteen CCLK cycles. Short or long frame protocol is available in both Master and Slave modes.

| Table 1 4. Typical Supported SSDES Devices |                      |                 |    |                 |  |  |  |

|--------------------------------------------|----------------------|-----------------|----|-----------------|--|--|--|

| Manufacturer                               | CODEC Device<br>Name | Characteristics |    | Conversion Type |  |  |  |

| National<br>Semiconductor                  | TP3054               | Single CODEC    | 5V | μ-Law           |  |  |  |

| окі                                        | MSM7533V             | Dual CODEC      | 5V | μ-Law, A-Law    |  |  |  |

| Macronix                                   | MX93002FC            | Dual rail CODEC | 5V | μ-Law           |  |  |  |

| Lucent                                     | T7503                | Dual CODEC      | 5V | μ-Law           |  |  |  |

| Motorola                                   | MC145481             | Single CODEC    | 3V | μ-Law           |  |  |  |

**Table 1-4: Typical Supported CODEC Devices**

#### Channel Width

The CODEC interface supports both 8-bit and 16-bit channel width in Master and Slave modes. Figure 1 shows how the CODEC interface signals behave when short frame protocol is configured.

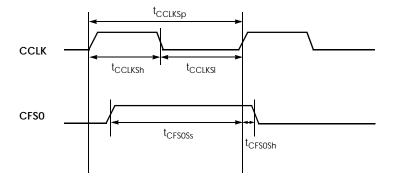

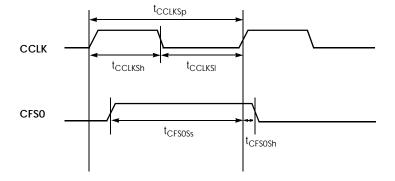

#### Slave Mode

The ISD-SR3000 supports digital telephony applications including DECT and ISDN by providing a Slave mode of operation. In Slave mode operation, the CCLK signal is input to the SR-3000 and controls the frequency of the CODEC interface operation. The CCLK may be any frequency between 500kHz and 4MHz. Both long and short frame protocols are supported with only the CFS1 output signal width affected. The CFSO input signal must be a minimum of one CCLK cycle.

In slave mode, a double clock bit rate feature is available as well. When the CODEC interface is configured to double clock bit rate, the CCLK input signal is divided internally by two and the resulting clock used to control the frequency of the CODEC interface operation.

| Application  | CODEC<br>Type | No. of<br>Channels | Master/<br>Slave | Channel<br>Width<br>(No.Bits) | Long/<br>Short<br>Frame<br>Protocol | Bit Rate | CCLK Freq.<br>(MHz) | Sample<br>Rate (Hz) | No. of<br>Frame<br>Syncs |

|--------------|---------------|--------------------|------------------|-------------------------------|-------------------------------------|----------|---------------------|---------------------|--------------------------|

| Analog μ-Law | single        | 1                  | Master           | 8                             | short or long                       | 1        | 2.048               | 8000                | 1                        |

| Linear       | single        | 1                  | Master           | 16                            | short                               | 1        | 2.048               | 8000                | 1                        |

**Table 1-5: Typical CODEC Applications**

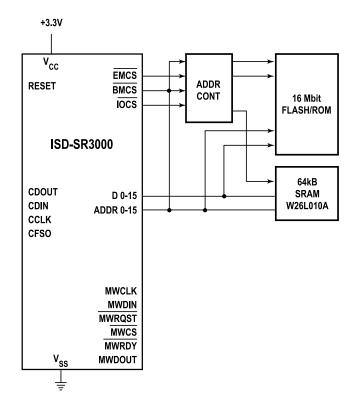

#### 1.2.7 EXPANSION MEMORY ADDRESSING

#### **FUNCTIONAL OVERVIEW**

The ISD-SR3000 requires memory subsystems with enhanced physical address space and a paging scheme. The typical memory requirement for the system is 2Mbytes of ROM to store the application database, and an additional 64Kbytes of SRAM to enable the software to perform sophisticated search on the database.

The diagram below describes the connection of the ISD-SR3000 to external memory space of 2Mbytes. This connection is typical for a recognition application. The external ROM holds the acoustic models (1Mbyte). The flash holds all the topics tables (vocabulary), speech prompts, and voicetag recordings that support the specific application (1Mbyte). The SRAM is used by the ISD-SR3000 as extension for the memory and is used to carry out the HMM algorithm (64Kbytes).

Figure 1-8: ISD-SR3000 connection for external memory space of 2Mbytes

Note: If the application does not support user-created voicetags, the Flash can be replaced with a ROM.

#### **BLOCK DIAGRAM**

Figure 1-9: Address Extension Lines Block Diagram

#### **INTERFACE SIGNALS**

Table 1-6: ISD-SR3000 Extended Address Lines Interface Signals

| Signal Name | Туре | Source Unit/Signal          | Description                                                                       |

|-------------|------|-----------------------------|-----------------------------------------------------------------------------------|

| D[7:0]      | I/O  | ISD-SR3000                  | Data Bus                                                                          |

| A[7:1]      | I    | ISD-SR3000                  | Address Bus                                                                       |

| ĪOCS        | I    | ISD-SR3000                  | I/O Expansion Chip Select to access the I/O registers                             |

| EMCS        | I    | ISD-SR3000                  | Expansion Memory Chip select                                                      |

| DDIN / A16  | I    | ISD-SR3000                  | Serve as direction in I/O operation of SR3000; otherwise is bit 16 of address bus |

| A15         | I    | ISD-SR3000                  | Address line                                                                      |

| WR[0:1]     | I    | ISD-SR3000                  | Write signal for external memory                                                  |

| AF[4:0]     | 0    | To external Extended memory | Extended Address bus                                                              |

| CFEN        | 0    | To external Extended memory | Extended Memory CS could use for Flash CS                                         |

| CREN        | 0    | To external Extended memory | Extended Memory CS could use for ROM CS                                           |

| CSEN        | 0    | To external Extended memory | Extended Memory CS could use for RAM CS                                           |

| EMWR        | 0    | To external Extended memory | Write signal to external SRAM                                                     |

| CSINTROM    | 0    | To internal ROM             | Chip select for internal ROM (Added ROM for DSPM)                                 |

#### INTERNAL DESCRIPTION

#### **Detailed Description**

The Memory Extension unit contains four page registers to perform memory decoding and control functions, memory mapping and paging.

The page registers are mapped into the I/O Expansion space defined by an active IOCS signal (\*Addresses TBD\*) from the ISD-SR3000. Only address lines A1-A7 are used, while A16 becomes DDIN (data direction signal; low for reads). The registers are both writable and readable.

The software accesses the page registers using store or load operations to the respective I/O ports from the ISD-SR3000. The decoding logic generates the proper signals to write and read the page registers, which are accessed by the ISD-SR3000 when store and load commands are executed.

The paging operation works as follows:

- When the ISD-SR3000 accesses the expansion memory space (indicated by EMCS going active), the decoding logic will select one out of the four page registers, based on the state of A[16:15].

- The contents of the selected page register will be use to generate the proper Chip select and the extended address lines AF[4:0].

- Bits 0 to 4 of the page register connect to AF4 to AF0 respectively.

- Chip Select field is bits 5 to 7 and are used to generate the Chip Select lines

- The chip select signal CFEN will assert low if and only if the value inside the Page register, which is driving the bus, has a logic 1 at the bit 5 and the signal EMCS is low.

- The chip select signals CFRN will assert low if and only if the value inside the Page register, which is driving the bus, has a logic 1 at bit 6 and the signal EMCS is low.

- The chip select signals CFSN will assert low if and only if the <u>value</u> inside the Page register which is driving the bus has a logic 1 at bit 7 and the signal EMCS is low.

- When bits <u>5</u>, <u>6</u>, and <u>7</u> on the page register are all at logical 0 and the EMCS is asserted low, the signal CSINROM is asserted low.

**Table 1-7: Paging Operation**

| Local Page<br>Register | 7    | 6    | 5    | 4     | 3     | 2     | 1     | 0     |

|------------------------|------|------|------|-------|-------|-------|-------|-------|

|                        | CFSN | CFRN | CFEN | AF[4] | AF[3] | AF[2] | AF[1] | AF[0] |

The mapping of the address from the ISD-SR3000 to the expansion memory is:

- Address 0x10000-0x17fff use page register 0.

- Address 0x18000-0x1ffff use page register 1.

- Address 0x20000-0x27fff use page register 2.

- Address 0x28000-0x2ffff use page register 3.

Table 1-8: Address Mapping from ISD-SR3000 to Expansion Memory

|     | Page Reg #0 | Page Reg #1 | Page Reg #2 | Page Reg #3 |

|-----|-------------|-------------|-------------|-------------|

| A15 | 0           | 0           | 1           | 1           |

| A16 | 0           | 1           | 0           | 1           |

The signal EMWR is write strobe to external memory. The external SRAM chip can support byte or word access. In order to support this mode 3 signals are used: LB to support writing to low byte of the bus, UB to support writing the high byte of the bus, and WR strobe signal. Since the ISD-SR3000 block can supply  $\overline{\text{WR}}$ [0-1] signal for the low or high byte of the bus, the WR strobe signal needs to be generated, which is the logical AND operation of the two signals. (for more details, refer to the Winbond W26L010A data sheet).

Note that the block is operational only if the MCFG register of the ISD-SR3000 is programmed in extension memory mode, 64K x 16 RAM.

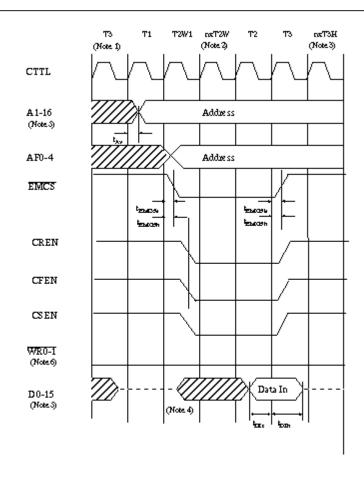

The following figures illustrate the timing of Extended Memory Read and Write cycles. Note the timing of AF[7:5], which result of the qualification of the respective page register outputs with the delayed EMCS strobe.

#### Flow Charts

The software on the SR3000 that uses the SR3000 Extended address unit should do the following:

- Set the MCFG.EMC register to 64kbytes x 16 bits RAM mode. Mode 111 at MCFG.EMC.

- 2. Set the page register to page xxxxxxxx. For example to the internal ROM use 0x00.

- 3. To read or write from external memory use load or store operation from the expansion memory. For the internal ROM the address should be 0x10000 0x17fff.

#### Unit Register Space

The following registers are accessed at addresses <0xFBF2 - 0XFBF\*> in the SR3000 I/O address space for write operation and addresses <0xFF9e - 0XFFbe> in the SR3000 I/O address space for read operation.

**Table 1-9: Unit Register Space**

| Register Name         | Address          | Size<br>(bits) | Description   | R/W | Reset<br>Value |

|-----------------------|------------------|----------------|---------------|-----|----------------|

| Local Page register 0 | 0xFBF2<br>0xff8e | 8              | Page register | R/W | 0              |

| Local Page register 1 | 0xFBF4<br>0xff9e | 8              | Page register | R/W | 0              |

| Local Page register 2 | 0xFBF8<br>0xffae | 8              | Page register | R/W | 0              |

| Local Page register 3 | 0xFBFA<br>0xffbe | 8              | Page register | R/W | 0              |

R - read only

W - Write only

R/W read and write

RAC read auto clear for interrupt status registers

#### Reset Activity

On reset all the registers should be set to their default values 0 and all chip select signals should be inactive.

#### **Power Save Features**

On power down, all chip select signals must be high to ensure minimal power consumption by the external peripheral.

#### **Timing Diagrams**

Figure 1-10: Read operation to externals memory using the SR3000 extended memory unit

rxT2W псТЗН (Note3) (Note 1) CTTL A1-16 Address (Note 3) AF0-4 Address EMCS ومصطا CREN CFEN CSEN WR0-1 (Note 6)

Figure 1-11: Write operation to externals memory using the SR3000 extended memory unit.

#### SPECIAL SOFTWARE REQUIREMENTS

D0-15 (Note 5)

Note that the block is operational only if the MCFG register of the SR3000 is programmed in extension memory mode, 64K x 16 RAM.

Data In

#### MICRO ARCHITECTURE AND DESIGN CONSIDERATIONS

The design should take into account that the some of signals are connected to external memory units. Hence the timing diagram should comply with external parts. Required wait states will be supported using the EXPANSION MEMORY WAIT STATE mechanism.

#### 1.3 SPECIFICATIONS

#### 1.3.1 ABSOLUTE MAXIMUM RATINGS

| Storage temperature                               | -65°C to +150°C  |

|---------------------------------------------------|------------------|

| Temperature under bias                            | 0°C to 70°C      |

| All input or output voltages, with respect to GND | -0.5 V to +6.5 V |

#### 1.3.2 ELECTRICAL CHARACTERISTICS

$T_A = 0$ °C to +70°C,  $V_{CC} = 5V \pm 10$ %, GND = 0V

**Note**: Absolute maximum ratings indicate limits beyond which permanent damage may occur. Continuous operation at these limits is not intended; operation should be limited to the conditions specified below.

Table 1-10: Electrical Characteristics (All Parameters with Reference to  $V_{CC} = 3.3V$ )

| Symbol               | Parameter                                           | Conditions                                                      | Min   | Тур  | Max                         | Units |

|----------------------|-----------------------------------------------------|-----------------------------------------------------------------|-------|------|-----------------------------|-------|

| Сх                   | X1 and X2 capacitance <sup>1</sup>                  |                                                                 |       | 17.0 |                             | pF    |

| I <sub>CC1</sub>     | Active supply current                               | Normal operation mode, running speech applications <sup>2</sup> |       | 40.0 | 80.0                        | mA    |

| I <sub>CC2</sub>     | Standby supply current                              | Normal operation mode, DSPM idle <sup>2</sup>                   |       | 30.0 |                             | mA    |

| I <sub>CC3</sub>     | Power-down Mode Supply<br>Current                   | Power-down Mode <sup>2,3</sup>                                  |       |      | 12                          | mA    |

| IL                   | Input Load Current                                  | 0 V <u>&lt;</u> V <sub>IN</sub> ≤ V <sub>CC</sub>               | -5.0  |      | 5.0                         | μA    |

| I <sub>O</sub> (Off) | Output Leakage Current (I/<br>O pins in input mode) | 0 V ≤ V <sub>OUT</sub> ≤ V <sub>CC</sub>                        | -5.0  |      | 5.0                         | μА    |

| t <sub>CASa</sub>    | CAS Active                                          | After R.E. CTTL, T1 or T2W3                                     |       |      | 12.0                        | nsec  |

| t <sub>CASh</sub>    | CAS Hold                                            | After R.E. CTTL                                                 | 0.0   |      |                             |       |

| t <sub>CASia</sub>   | CAS Inactive                                        | After R.E. CTTL, T3 or TERF                                     |       |      | 12.0                        | nsec  |

| t <sub>CASLw</sub>   | DRAM, PDM, CAS Width                                | At 0.8 V, both edges                                            | 600.0 |      |                             |       |

| t <sub>WRa</sub>     | WR0 Active                                          | After R.E. CTTL, T1                                             |       |      | t <sub>CTp</sub> /<br>2 + 2 |       |

| t <sub>WRCSh</sub>   | WR0 Hold after EMCS <sup>4</sup>                    | R.E. EMCS R.E. to<br>R.E. WR0                                   | 10.0  |      |                             |       |

# Table 1-10: Electrical Characteristics (All Parameters with Reference to $V_{CC} = 3.3V$ )

| Symbol            | Parameter                                                 | Conditions                           | Min                      | Тур | Max                         | Units |

|-------------------|-----------------------------------------------------------|--------------------------------------|--------------------------|-----|-----------------------------|-------|

| t <sub>WRh</sub>  | WR0 Hold                                                  | After R.E. CTTL                      | t <sub>CTp</sub> /2 - 6  |     |                             |       |

| t <sub>WRia</sub> | WR0 Inactive                                              | After R.E. CTTL, T3                  |                          |     | t <sub>CTp</sub> /<br>2 + 2 |       |

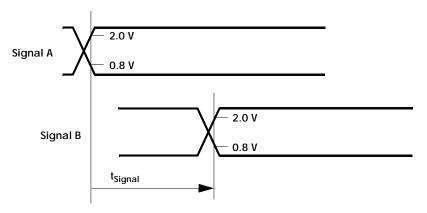

| V <sub>ENVh</sub> | ENV0 Input, high voltage                                  |                                      | 2.0                      |     |                             | ٧     |

| V <sub>Hh</sub>   | CMOS Input with<br>hysteresis, logical 1 input<br>voltage |                                      | 2.1                      |     |                             | V     |

| V <sub>HI</sub>   | CMOS Input with<br>hysteresis, logical 0 input<br>voltage |                                      |                          |     | 0.8                         | V     |

| V <sub>Hys</sub>  | Hysteresis Loop Width <sup>1</sup>                        |                                      | 0.5                      |     |                             | V     |

| V <sub>IH</sub>   | TTL Input, logical 1 input voltage                        |                                      | 2.0                      |     | V <sub>CC</sub> + 0.5       | V     |

| V <sub>IL</sub>   | TTL Input, logical 0 input voltage                        |                                      | -0.5                     |     | 0.8                         | V     |

| V <sub>OH</sub>   | Logical 1 TTL, output voltage                             | I <sub>OH</sub> = -0.4 mA            | 2.4                      |     |                             | V     |

| V <sub>OHWC</sub> | EMCS Logical 1, output voltage                            | $I_{OH} = -50 \ \mu A^5$             | V <sub>CC</sub> –<br>0.2 |     |                             | V     |

| V <sub>OL</sub>   | Logical 0, TTL output                                     | I <sub>OL</sub> = 4 mA               |                          |     | 0.45                        | V     |

|                   | voltage                                                   | $I_{OL} = 50 \ \mu A^5$              |                          |     | 0.2                         | V     |

| V <sub>OLWC</sub> | EMCS Logical 0, output voltage                            | I <sub>OL</sub> = 50 μA <sup>5</sup> |                          |     | 0.2                         | V     |

| V <sub>XH</sub>   | CLKIN Input, high voltage                                 | External clock <sup>6</sup>          | 2.0                      |     |                             | V     |

| V <sub>XL</sub>   | CLKIN Input, low voltage                                  | External clock <sup>6</sup>          |                          |     | 0.8                         | V     |

- 5. Guaranteed by design.

- **6.**  $I_{OUT} = 0$ ,  $I_A = 25$ °C,  $V_{CC} = 3.3$  V for  $V_{CC}$  pins and 3.3 V or 5 V on  $V_{CCHI}$  pins, operating from a 4.096 MHz crystal and running from internal memory with Expansion Memory disabled.

- **7.** All input signals are tied to 0 (above  $V_{CC}$  0.5 V or below  $V_{SS}$  + 0.5 V), except ENVO, which is tied to  $V_{CC}$ .

- **8.** Measured in power-down mode. The total current driven, or sourced, by all the ISD-SR3000 processor's output signals is less than 50  $\mu$ A.

- 9. Guaranteed by design, but not fully tested.

- 10.CLKIN signal is not 5V tolerant.

#### 1.3.3 SWITCHING CHARACTERISTICS

#### **DEFINITIONS**

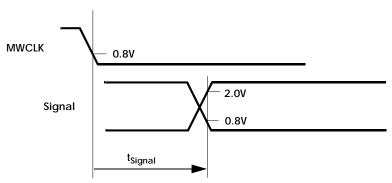

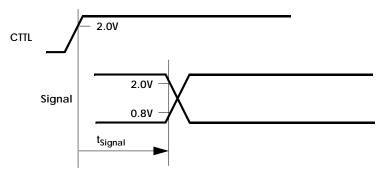

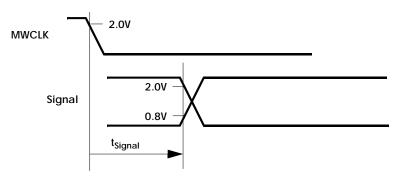

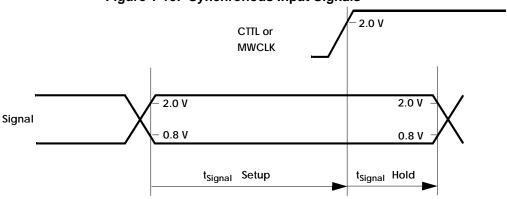

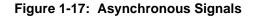

All timing specifications in this section refer to 0.8V or 2.0V on the rising or falling edges of the signals, as illustrated in Figure 1-12 through Figure 1-18, unless specifically stated otherwise.

Maximum times assume capacitive loading of 50pF. CLKIN crystal frequency is 4.096MHz.

**Note**: CTTL is an internal signal and is used as a reference to explain the timing of other signals. See Figure 1-27.

CTTL or MWCLK

Signal

2.0V

2.0V

0.8V

Figure 1-12: Synchronous Output Signals (Valid, Active and Inactive)

Note: Signal valid, active or inactive time, after a rising edge of CTTL or MWCLK.

Figure 1-13: Synchronous Output Signals (Valid)

Note: Signal valid time, after a falling edge of MWCLK.

Figure 1-14: Synchronous Output Signals (Hold), after rising edge of CTTL

Note: Signal hold time, after a rising edge of CTTL.

Figure 1-15: Synchronous Output Signals (Hold), after falling edge of MWCLK

Note: Signal hold time, after a falling edge of MWCLK.

Figure 1-16: Synchronous Input Signals

**Note:** Signal setup time, before a rising edge of CTTL or MWCK, and signal hold time after a rising edge of CTTL or MWCK

Note: Signal B starts after rising or falling edge of signal A.

The RESET has a Schmitt trigger input buffer. Figure 1-18 shows the input buffer characteristics.

Figure 1-18: Hysteresis Input Characteristics

#### 1.3.4 SYNCHRONOUS TIMING TABLES

In this section, R.E. means Rising Edge and F.E. means Falling Edge.

**Table 1-11: Output Signals**

|                      |        |                                       | _                           |                   |          |

|----------------------|--------|---------------------------------------|-----------------------------|-------------------|----------|

| Symbol               | Figure | Description                           | Reference Conditions        | Min (ns)          | Max (ns) |

| t <sub>Ah</sub>      |        | Address Hold                          | After R.E. CTTL             | 0.0               |          |

| t <sub>Av</sub>      |        | Address Valid                         | After R.E. CTTL, T1         |                   | 9.0      |

| t <sub>CCLKa</sub>   |        | CCLK Active                           | After R.E. CTTL             |                   | 12.0     |

| t <sub>CCLKh</sub>   |        | CCLK Hold                             | After R.E. CTTL             | 0.0               |          |

| t <sub>CCLKia</sub>  |        | CCLK Inactive                         | After R.E. CTTL             |                   | 12.0     |

| t <sub>CDOh</sub>    |        | CDOUT Hold                            | After R.E. CTTL             | 0.0               |          |

| t <sub>CDOv</sub>    |        | CDOUT Valid                           | After R.E. CTTL             | -2.0 <sup>3</sup> | 12.0     |

| t <sub>CTp</sub>     |        | CTTL Clock Period <sup>1</sup>        | R.E. CTTL to next R.E. CTTL | 30.5              | 250,000  |

| t <sub>EMCSa</sub>   |        | EMCS Active                           | After R.E. CTTL, T2W1       |                   | 12.0     |

| t <sub>EMCSh</sub>   |        | EMCS Hold                             | After R.E. CTTL             | 0.0               |          |

| t <sub>EMCSia</sub>  |        | EMCS Inactive                         | After R.E. CTTL T3          |                   | 12.0     |

| t <sub>FSa</sub>     |        | CFS0 Active                           | After R.E. CTTL             |                   | 25.0     |

| t <sub>FSh</sub>     |        | CFS0 Hold                             | After R.E. CTTL             | 0.0               |          |

| t <sub>FSia</sub>    |        | CFS0 Inactive                         | After R.E. CTTL             |                   | 25.0     |

| t <sub>MMCLKa</sub>  |        | Master MICROWIRE Clock<br>Active      | After R.E. CTTL             |                   | 12.0     |

| t <sub>MMCLKh</sub>  |        | Master MICROWIRE Clock<br>Hold        | After R.E. CTTL             | 0.0               |          |

| t <sub>MMCLKia</sub> |        | Master MICROWIRE Clock Inactive       | After R.E. CTTL             |                   | 12.0     |

| t <sub>MMDOh</sub>   |        | Master MICROWIRE Data Out Hold        | After R.E. CTTL             | 0.0               |          |

| t <sub>MMDOv</sub>   |        | Master MICROWIRE Data Out Valid       | After R.E. CTTL             |                   | 12.0     |

| t <sub>MWDOf</sub>   |        | MICROWIRE Data Float <sup>1</sup>     | After R.E. MWCS             |                   | 70.0     |

| t <sub>MWDOh</sub>   |        | MICROWIRE Data Out Hold <sup>2</sup>  | After F.E. MWCLK            | 0.0               |          |

| t <sub>MWDOnf</sub>  |        | MICROWIRE Data No Float <sup>2</sup>  | After F.E. MWCS             | 0.0               | 70.0     |

| t <sub>MWDOv</sub>   |        | MICROWIRE Data Out Valid <sup>2</sup> | After F.E. MWCLK            |                   | 70.0     |

| t <sub>MWITOp</sub>  |        | MWDIN to MWDOUT                       | Propagation Time            |                   | 70.0     |

| t <sub>MWRDYa</sub>  |        | MWRDY Active                          | After R.E. of CTTL          | 0.0               | 35.0     |

#### **Table 1-11: Output Signals**

| Symbol               | Figure | Description    | Reference Conditions  | Min (ns) | Max (ns) |

|----------------------|--------|----------------|-----------------------|----------|----------|

| t <sub>MWRDYia</sub> |        | MWRDY Inactive | After F.E. MWCLK      | 0.0      | 70.0     |

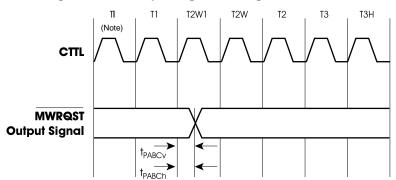

| t <sub>PABCh</sub>   |        | PB and MWRQST  | After R.E. CTTL       | 0.0      |          |

| t <sub>PABCv</sub>   |        | PB and MWRQST  | After R.E. CTTL, T2W1 |          | 12.0     |

- In normal operation mode, t<sub>CTp</sub> must be 30.5 ns; in power-down mode, t<sub>CTp</sub> must be 50,000 ns.

Guaranteed by design, but not fully tested.

Negative hold times are allowed since they are relative to the internal signal CTTL.

**Table 1-12: Input Signals**

| Symbol              | Figure | Description                                 | Reference Conditions          | Min (ns) | Max (ns) |

|---------------------|--------|---------------------------------------------|-------------------------------|----------|----------|

| t <sub>CDIh</sub>   |        | CDIN Hold                                   | After R.E. CTTL               | 0.0      |          |

| t <sub>CDIs</sub>   |        | CDIN Setup                                  | Before R.E. CTTL              | 25.0     |          |

| t <sub>Dlh</sub>    |        | Data in Hold (D0:7)                         | After R.E. CTTL T1, T3 or TI  | 0.0      |          |

| t <sub>DIs</sub>    |        | Data in Setup (D0:7)                        | Before R.E. CTTL T1, T3 or TI | 19.0     |          |

| t <sub>MMDINh</sub> |        | Master MICROWIRE Data<br>In Hold            | After R.E. CTTL               | 0.0      |          |

| t <sub>MMDINs</sub> |        | Master MICROWIRE Data<br>In Setup           | Before R.E. CTTL              | 11.0     |          |

| t <sub>MWCKh</sub>  |        | MICROWIRE Clock High (slave)                | At 2.0 V (both edges)         | 100.0    |          |

| t <sub>MWCKI</sub>  |        | MICROWIRE Clock Low (slave)                 | At 0.8 V (both edges)         | 100.0    |          |

| t <sub>MWCKp</sub>  |        | MICROWIRE Clock Period (slave) <sup>1</sup> | R.E. MWCLK to next R.E. MWCLK | 2.5 µs   |          |

| t <sub>MWCLKh</sub> |        | MWCLK Hold                                  | After MWCS becomes inactive   | 50.0     |          |

| t <sub>MWCLKs</sub> |        | MWCLK Setup                                 | Before MWCS becomes active    | 100.0    |          |

| t <sub>MWCSh</sub>  |        | MWCS Hold                                   | After F.E. MWCLK              | 75.0     |          |

| t <sub>MWCSs</sub>  |        | MWCS Setup                                  | Before R.E. MWCLK             | 100.0    |          |

| t <sub>MWDIh</sub>  |        | MWDIN Hold                                  | After R.E. MWCLK              | 50.0     |          |

| t <sub>MWDIs</sub>  |        | MWDIN Setup                                 | Before R.E. MWCLK             | 100.0    |          |

**Table 1-12: Input Signals**

| Symbol            | Figure | Description                             | Reference Conditions                | Min (ns)                | Max (ns) |

|-------------------|--------|-----------------------------------------|-------------------------------------|-------------------------|----------|

| t <sub>PWR</sub>  |        | Power Stable to RESET R.E. <sup>2</sup> | After V <sub>CC</sub> reaches 4.5 V | 30.0 ms                 |          |

| t <sub>RSTw</sub> |        | RESET Pulse Width                       | At 0.8 V (both edges)               | 10.0 ms                 |          |

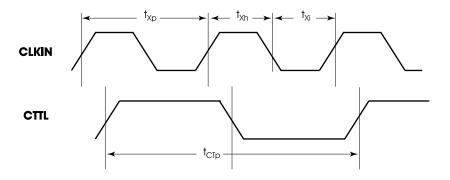

| t <sub>Xh</sub>   |        | CLKIN High                              | At 2.0 V (both edges)               | t <sub>X1p</sub> /2 - 5 |          |

| t <sub>XI</sub>   |        | CLKIN Low                               | At 0.8 V (both edges)               | t <sub>X1p</sub> /2 - 5 |          |

| t <sub>Xp</sub>   |        | CLKIN Clock Period                      | R.E. CLKIN to next R.E. CLKIN       | 244.4                   |          |

<sup>1.</sup> Guaranteed by design, but not fully tested in power-down mode.

<sup>2.</sup> Guaranteed by design, but not fully tested.

#### 1.3.5 TIMING DIAGRAMS

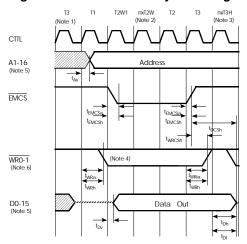

Figure 1-19: SRAM Write Cycle Timing

- 1. This cycle may be either TI (Idle), T3 or T3H.

- $2.0 \le n \le 7$

- 3. If n = 0, this cycle may be either TI (Idle) or T1 (with a new address) and  $t_{Df}$  and  $t_{Dh}$  are measured from the R.E. of CTTL in T3.

- 4. If n = 1, this cycle is T3H, the address bus does not change its value and  $t_{Df}$  and  $t_{Dh}$  are measured from the R.E. of CTTL in T3H.

- 5. Depends on which bytes are written.

- 6. For an 8-bit data bus, address lines are A0-15 and data lines are D0-7

- 7. WR1 is not available if expansion memory is configured as 8-bit bus RAM.

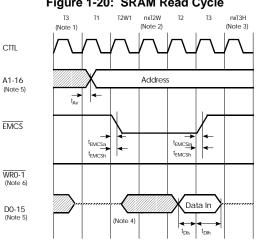

Figure 1-20: SRAM Read Cycle

- 1. This cycle may be either TI (Idle), T3 or T3H.

- 2. 0 < n < 7

- 3. If n = 0, this cycle may be either TI (Idle) or T1 (with a new address). If n = 1, this cycle is T3H, and address bus does not change its value.

- 4. Data can be driven by an external device at T2W1, T2W, T2 and T3.

- 5. For an 8-bit data bus, address lines are A0-15 and data lines are D0-7.

- 6.  $\overline{WR0}$  and  $\overline{WR1}$  are not available if Expansion Memory is configured as ROM.  $\overline{WR1}$  is not available if Expansion Memory is configured as 8-bit bus RAM.

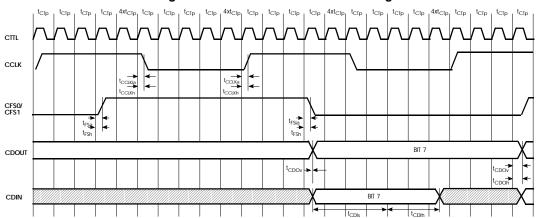

Figure 1-21: CODEC Short Frame Timing

Note: This cycle may be either TI (Idle), T2, T3 or T3H.

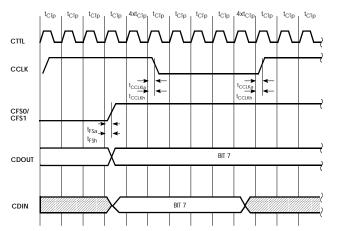

Figure 1-23: Slave CODEC CCLK and CFSO Timing

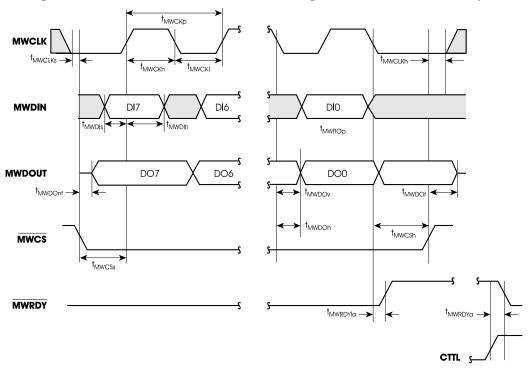

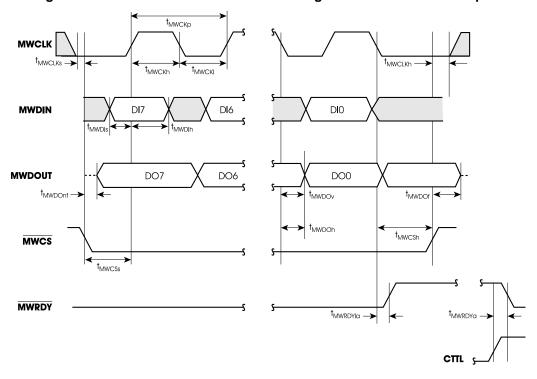

Figure 1-24: MICROWIRE Transaction Timing--Data Transmitted to Output

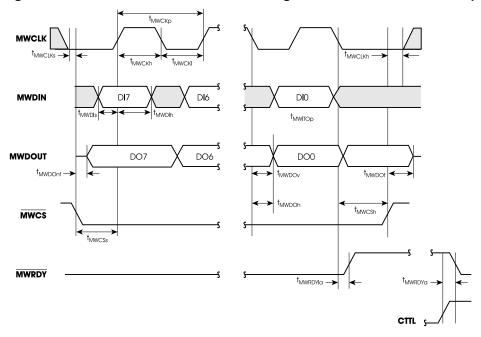

Figure 1-25: MICROWIRE Transaction Timing--Echoed Transmitted to Output

Figure 1-26: Output Signal Timing for MWRQST

Figure 1-27: CLKIN and CTTL Timing

Figure 1-28: Reset Timing When Reset is not at Power-UP

Figure 1-30: Codec Short Frame Timing

Note: The CCLK and CFS0 timing is shown for Master Mode only. For Slave Mode, see Figure 1-32.

Figure 1-31: Codec Long Frame Timing

Note: The CCLK and CFS0 timing is shown for Master Mode only. For Slave Mode, see Figure 1-32.

Figure 1-32: Slave Codec CCLK and CFS0 Timing

Note: For CFS1, CDIN, CDOUT timing, see Figure 1-30 and Figure 1-31.

Figure 1-33: MICROWIRE Transaction Timing--data transmitted to output

$t_{MWCKp}$ **MWCLK** t<sub>MWCLKs</sub> →  $t_{\rm MWCKh}$  $t_{\rm MWCKI}$ DI6 D**I**O **MWDIN** t<sub>MWDIs</sub> †<sub>MWITOP</sub> →  $t_{\rm MWITOp}$ **MWDOUT** DO0  $t_{MWDOnf} \rightarrow$  $t_{MWDOf}$  $t_{\rm MWCSh}$ **MWCS** MWRDY  $t_{MWRDYa} \rightarrow$

Figure 1-34: MICROWIRE Transaction Timing--data echoed to output

# **Chapter 2—SOFTWARE**

# 2.1 OVERVIEW

In chapter one, the ISD-SR3000 was described as a hardware component in a system. This system must include a host controller to handle the Voice User Interface layer that controls the ISD-SR3000. The ISD-SR3000 recognizes words from a pre-defined fixed list and returns them to the host controller for handling. It is the host controller's responsibility to decide how to react to a set of recognized words that has been returned by the recognition engine.

The ISD-SR3000 software resides in the on-chip ROM. It includes speech recognition, speech compression, system support functions and a software interface to hardware peripherals. The following sections in this chapter describe, in detail, the ISD-SR3000 interface, operation procedures, software, tools and commands set.

System under control Host controller Application VUI **User Application** Software (Voice User Interface) ISD-SR3000 Voice Recognition CODEC Audio I/O Compression Application Hardware specific **Memory Elements** firmware **Acoustic models** Voicetag storage

Figure 2-35: Partitioning of Hardware Components and Software Code

Audio prompts Vocabulary

# 2.2 RECOGNITION ENGINE

ISD-SR3000 uses a segmented triphone recognition process. The sampled speech utterance is split into distinct phonetic sounds, the smallest units of speech. Because these phonemes vary in both sound and duration, the processor must be able to determine boundaries between the sounds. The ISD-SR3000 uses Hidden Markov Models to hypothesize boundaries between sounds and to form probabilistic models on each possible combination.

The outputs are then classified by determining matches between the phonetic sounds and the stored phoneme models. The acoustic models for the phonemes are gathered from a large sample of speakers, allowing for a wide variation across accents, dialect, and gender. This allows the recognizer to associate the sound segments with a number of possible phonemes, enabling recognition when words are pronounced differently.

The phonemes are then matched to vocabulary words or phrases using a search routine. The set of phonemes is compared to the vocabulary models for the active topics, and the recognized word is returned. If the phonemes do not match any of the active vocabulary words, nothing is returned. The ISD-SR3000 does not return a score with the word; it either recognizes a word, or it does not.

### 2.2.1 TYPES OF RECOGNITION

The ISD-SR3000 is capable of both speaker-independent and speaker defined recognition. The recognition engine is continuous, allowing for multiple word commands and connected digits. However, there must be recognized silence before and after valid utterances. The length of the silence is programmed into the host controller, and may be as small as 100ms. The commands and digits are speaker-independent, with models constructed from a large corpus of speakers. The speaker-defined voicetags and commands are partially speaker-dependent. However, they are constructed by creating acoustic models "on-the-fly" from the phoneme base. This means only one training pass is required for entering the voicetags, and recognition is possible with some variation in the way the name is spoken. The first pass is used to create the phoneme model, and a second pass is used for recognition confirmation.

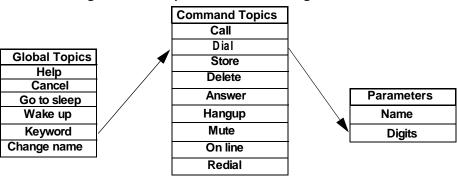

#### 2.2.2 GRAMMAR

A grammar is used to define the structure of the commands. The ISD-SR3000 is designed to work with multiple topics or a finite-state grammar. This type of grammar is designed to limit perplexity (the number of possible branches during recognition) by pre-defining the number of allowable words at a given state. For example, a prompt that requires a "yes" or "no" response has a perplexity of two. Greater perplexities increase the chances for substitution errors. During recognition, a limited number of topics are active. Topics are groups of words that are active at a given time. For example, in a voice dialing application, digit topics are active after the user issues the "dial" command. No other topics are open (except the global topics such as "cancel" or "help") so that the recognizer is only trying to recognize digits. This type of grammar and active topics inherently increases recognition accuracy.

Figure 2-36: Topic and Grammar Organization

Figure 2-36 shows an example of organizing the commands into menu structure format. From this example, it can be seen how topics are linked, and how only specific topics are active. This is a voice dialing command set furnished as ISD's sample application. Independent VUIs and vocabulary can be developed, but it is necessary to follow the grammar syntax as shown here.

#### 2.2.3 VOCABULARY

A vocabulary defines the following characteristics of the ISD-SR3000:

- Speaker-independent command words and digits for which ISD-SR3000 responds

- Topics under which the commands and digits are organized

- Mapping of tokens to the vocabulary

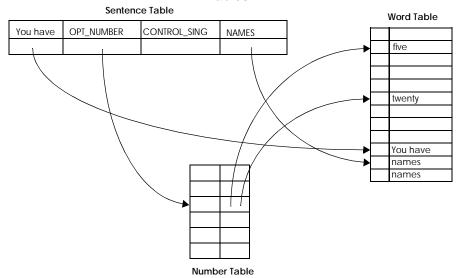

ISD-SR3000 is designed to work with an application specific vocabulary set. The total vocabulary size is determined by available external memory. When the processor recognizes the commands, tokens (values) are returned to the host controller. These tokens represent spoken words. The host controller maintains a lookup table of the available words and their corresponding token numbers. The host controller can use the tokens to accomplish tasks, such as generating DTMF for dialing a phone number.

ISD supplies recommended vocabulary sets as part of the VUI for specific applications. The vocabulary sets have been carefully selected to ensure high recognition (avoiding words that may be phonetically confused) and effective user utility. The accuracy specifications for ISD-SR3000 are based on the ISD provided commands. It is possible to create custom vocabulary sets for specific applications. Contact ISD for information about vocabulary development tools. The vocabulary can be stored either in external ROM or Flash memory.

#### 2.2.4 **LANGUAGE**

ISD-SR3000 uses a set of acoustic models designed to recognize a given language. Currently, the supported languages are American English and German. Additional languages require different acoustic models. Contact ISD for availability of additional languages.

# 2.2.5 ADDITIONAL COMPONENTS

### **MESSAGE**

A message is a compressed recording stored in the ISD-SR3000 memory. This message can be compressed, when using the R (Record Message) command, at 4.7, 6.7 or 8.7kbits/s.

#### **NOISE TOKENS**

Each topic can be supplemented with additional tokens that will absorb the 'out of vocabulary' words. These tokens can be added upon user request with ISD's development tools. These tokens are not assigned an index number like the other words in the topic table. Once the engine recognizes a word as a noise token, the ISD-SR3000 returns the noise topic identifier (0xFD) instead of the current topic.

# **CEPSTRA VALUES**

The cepstra coefficients are responsible for normalizing the voice input channel. The ISD-SR3000 contains 15 cepstra values starting from index 0.

### **VOICE TAG**

A voice tag is a recorded message of a user-added word. This message can be compressed, when using the RR (Record for Reco) command, at 4.7, 6.7 or 8.7kbits/s.

# 2.3 INITIALIZATION

After the system is powered up, it is the host controller's responsibility to initialize the ISD-SR3000. This initialization includes: resetting the chip using the RESET signal, configuring the hardware environment using the CFG command (CODEC and memory types and parameters, etc.), and issuing the INIT and TUNE commands. The TUNE and CFG commands are required only if the system settings are different from the ISD-SR3000's default values.

Refer to the section ISD-SR3000 Initialization on page 2-68 for an example illustrating the system initialization procedure for the ISD-SR3000.

# 2.4 RECO ENGINE MANAGEMENT

After the system has been initialized (including setting the vocabulary for the prompts) it is the host controller's responsibility to initialize the recognition engine. This includes loading of topics, enabling topics and activating the recognition engine. It is recommended that you load all the topics if the system memory size enables it, rather then loading and unloading a topic each time one needs to be enabled.

Once the recognition engine is initialized, the host controller should wait for the EV\_RECO\_QUEUE bit in the status register to be set. When the ISD-SR3000 sets this bit, it automatically asserts the MWRQST line as an indication for the host controller to read this register (by issuing the GSW command). When the host controller has identified this bit, it should start retrieving the recognized words (noted as topic number and token number) from the ISD-SR3000 recognition queue buffer using the GNR command. It is the host controller's responsibility to interpret the incoming words into grammar commands using predefined tables. (These tables are created by the ISD development tool). When the host controller interprets a valid command, it can then respond by executing commands such as stopping the recognition engine, playing a prompt or a tone (only after the recognition engine is disabled), changing menus and topics, adding or deleting user voice tags (a new acoustic word), operating an external device, etc. The recognition process is half-duplex. When the ISD-SR3000 is playing back audio, recognition is not active.

Refer to the section Example Operation Procedures on page 2-68 for examples illustrating the normal operation procedure for the ISD-SR3000 engine and the adding of a voice tag.

# 2.5 HOST CONTROLLER INTERFACE

MICROWIRE/PLUS™ is a synchronous serial communication protocol that minimizes the number of connections, and thus the cost, of communicating with peripherals.

The ISD-SR3000 MICROWIRE interface implements the MICROWIRE/PLUS interface in slave mode, with an additional ready signal. It enables a host controller to interface efficiently with the ISD-SR3000 processor application.

The host controller is the protocol master and provides the clock for the protocol. The ISD-SR3000 processor supports clock rates of up to 400kHz. This transfer rate refers to the bit transfer. The actual throughput is slower due to byte processing by the ISD-SR3000 processor and the host controller.

Communication is handled in bursts of eight bits (one byte). In each burst the ISD-SR3000 processor is able to receive and transmit eight bits of data. After eight bits have been transferred, an internal interrupt is issued for the ISD-SR3000 processor to process the byte, or to prepare another byte for sending. In parallel, the ISD-SR3000 processor sets MWRDY to 1, to signal the host controller that it is busy with the byte processing. Another byte can be transferred only when the MWRDY signal is cleared to 0 by the ISD-SR3000 processor. When the ISD-SR3000 processor transmits data, it expects to receive the value 0xAA before each transmitted byte. The ISD-SR3000 processor reports any status change by clearing the MWRQST signal to 0.

If processor command's parameter is larger than one byte, the host controller transmits the Most Significant Byte (MSB) first. If a return value is larger than one byte, the ISD-SR3000 processor transmits the MSB first.

#### SIGNAL DESCRIPTION

The following signals are used for the interface protocol. Input and output are relative to the ISD-SR3000.

# 2.5.1 INPUT SIGNALS

#### **MWDIN**

MICROWIRE Data In. Used for input only, for transferring data from the host controller to the ISD-SR3000.

#### **MWCLK**

This signal serves as the synchronization clock during communication. One bit of data is transferred on every clock cycle. The input data is available on MWDIN, and is latched on the clock's rising edge. The transmitted data is <u>output</u> on MWDOUT, on the clock's falling edge. The signal should remain low when switching MWCS.

# **MWCS**

MICROWIRE Chip Select. The MWCS signal is cleared to 0, to indicate that the ISD-SR3000 is being accessed. Setting MWCS to 1 causes the ISD-SR3000 to start driving MWDOUT with bit 7 of the transmitted value. Setting the MWCS signal resets the transfer-bit counter of the protocol. Thus, the MWCS signal is used to synchronize the ISD-SR3000 and the host controller to recognize the beginning of the byte transfer.

To prevent false detection of access to the ISD-SR3000, due to spikes on the MWCLK signal, use this chip select signal to toggle the MWCLK input signal (only when the ISD-SR3000 is open for communication.)

#### 2.5.2 OUTPUT SIGNALS

#### **MWDOUT**

MICROWIRE Data Out. Used for output only, for transferring data from the ISD-SR3000 to the host controller. When the ISD-SR3000 receives data, it is echoed back to the host controller on this signal, unless the received data is 0xAA. In this case, the ISD-SR3000 echoes a command's return value.

# **MWRDY**

MICROWIRE Ready. When active (0), this signal indicates that the ISD-SR3000 is ready to transfer (receive or transmit) another byte of data.

This signal is set to 1 by the ISD-SR3000 after each byte transfer has been completed. It remains 1 while the ISD-SR3000 is busy reading the byte, writing the next byte or executing the received command (after the last parameter has been received). MWRDY is cleared to 0 after reset. For proper operation after a hardware reset, this signal should be pulled up.

### **MWRQST**

MICROWIRE Request. When active (0), this signal indicates that new status information is available. MWRQST is deactivated (set to 1), after the ISD-SR3000 receives a GSW (Get Status Word) command from the host controller. After reset, this signal becomes active (0) to indicate that a reset occurred. MWRQST, unlike all the signals of the communication protocol, is an asynchronous line that is controlled by the ISD-SR3000 firmware.

#### 2.5.3 SIGNAL USE IN THE INTERFACE PROTOCOL

After reset, both MWRQST and MWRDY are cleared to 0.

The MWRQST signal is activated to indicate that a reset occurred. The EV\_RESET bit in the status register is used to indicate a reset condition.

The GSW command should be issued after reset to verify that the EV RESET event occurred, and to deactivate the MWRQST signal.

While the MWCS signal is active (0), the ISD-SR3000 reads data from MWDIN on every rising edge of MWCLK. The ISD-SR3000 also writes every bit back to MWDOUT. This bit is either the same bit, which was read from MWDIN (in this case it is written back as a synchronization echo after some propagation delay), or it is a bit of a value the ISD-SR3000 transmits to the host controller (in this case it is written on every falling edge of the clock).

When a command has more than one parameter/return-value, the parameters/return-values are transmitted in the order of appearance. If a parameter/return-value is more than one byte long, the bytes are transmitted from the most significant to the least significant.

The MWRDY signal is used as follows:

- 1. Active (0) MWRDY signals the host controller that the last eight bits of data transferred to/from the voice module were accepted and processed (see below).

- The MWRDY signal is deactivated (set to 1 by the ISD-SR3000) after 8-bits of data were transferred to/from the ISD-SR3000. The bit is set following the falling edge of the eighth MWCLK clock-cycle.