初步的

256k x18 pipelined sram 和 nobl™ architecture

CY7C1352B

Cypress 半导体 公司

• 3901 北 第一 街道 • San Jose • ca 95134 • 408-943-2600

将 26, 2000

特性

• 管脚 兼容 和 functionally 相等的 至 zbt™

设备 mcm63z818 和 mt55l256l18p

• 支持 166-mhz 总线 行动 和 零 wait states

— 数据 是 transferred 在 每 时钟

• 内部 自-安排时间 输出 缓存区 控制 至 eliminate

这 需要 至 使用 oe

• 全部地 注册 (输入 和 输出) 为 pipelined

运作

• 字节 写 能力

• 256k x 18 一般 i/o architecture

• 单独的 3.3v 电源 供应

• 快 时钟-至-输出 时间

— 3.5 ns (为 166-mhz 设备)

— 3.8 ns (为 150-mhz 设备)

— 4.0 ns (为 143-mhz 设备)

— 4.2 ns (为 133-mhz 设备)

— 5.0 ns (为 100-mhz 设备)

— 7.0 ns (为 80-mhz 设备)

• 时钟 使能 (cen

) 管脚 至 suspend 运作

• 同步的 自-安排时间 写

• 异步的 输出 使能

• 电子元件工业联合会-标准 100-管脚 tqfp 包装

• burst capability—linear 或者 interleaved burst 顺序

• 低 备用物品 电源

函数的 描述

这 cy7c1352b 是 一个 3.3v 256k 用 18 同步的-pipelined

burst sram 设计 specifically 至 支持 unlimited 真实

后面的-至-后面的 读/写 行动 没有 这 嵌入 的

wait states. 这 cy7c1352b 是 配备 和 这 先进的

非 总线 latency™ (nobl™) 逻辑 必需的 至 使能 consec-

utive 读/写 行动 和 数据 正在 transferred 在 ev-

ery 时钟 循环. 这个 特性 dramatically 改进 这

throughput 的 这 sram, 特别 在 系统 那 需要

frequent 读/写 transitions. 这 cy7c1352b 是 管脚/func-

tionally 兼容 至 zbt srams mcm63z819 和

mt55l256l18p.

所有 同步的 输入 通过 通过 输入 寄存器 控制

用 这 rising 边缘 的 这 时钟. 所有 数据 输出 通过 通过

输出 寄存器 控制 用 这 rising 边缘 的 这 时钟. 这

时钟 输入 是 qualified 用 这 时钟 使能 (cen

) 信号, 这个

当 deasserted suspends 运作 和 extends 这 previ-

ous 时钟 循环. 最大 进入 延迟 从 这 时钟 上升 是

3.5 ns (166-mhz 设备).

写 行动 是 控制 用 这 四 字节 写 选择

(bws

[1:0]

) 和 一个 写 使能 (我们) 输入. 所有 写 是 con-

ducted 和 在-碎片 同步的 自-安排时间 写 电路系统.

三 同步的 碎片 使能 (ce

1

, ce

2

, ce

3

) 和 一个

异步的 输出 使能 (oe

) 提供 为 容易 bank se-

lection 和 输出 三-状态 控制. 在 顺序 至 避免 总线

contention, 这 输出 驱动器 是 synchronously 三-陈述

在 这 数据 portion 的 一个 写 sequence.

.

nobl 和 非 总线 latency 是 商标 的 cypress 半导体 公司.

zbt 是 一个 商标 的 整体的 设备 技术.

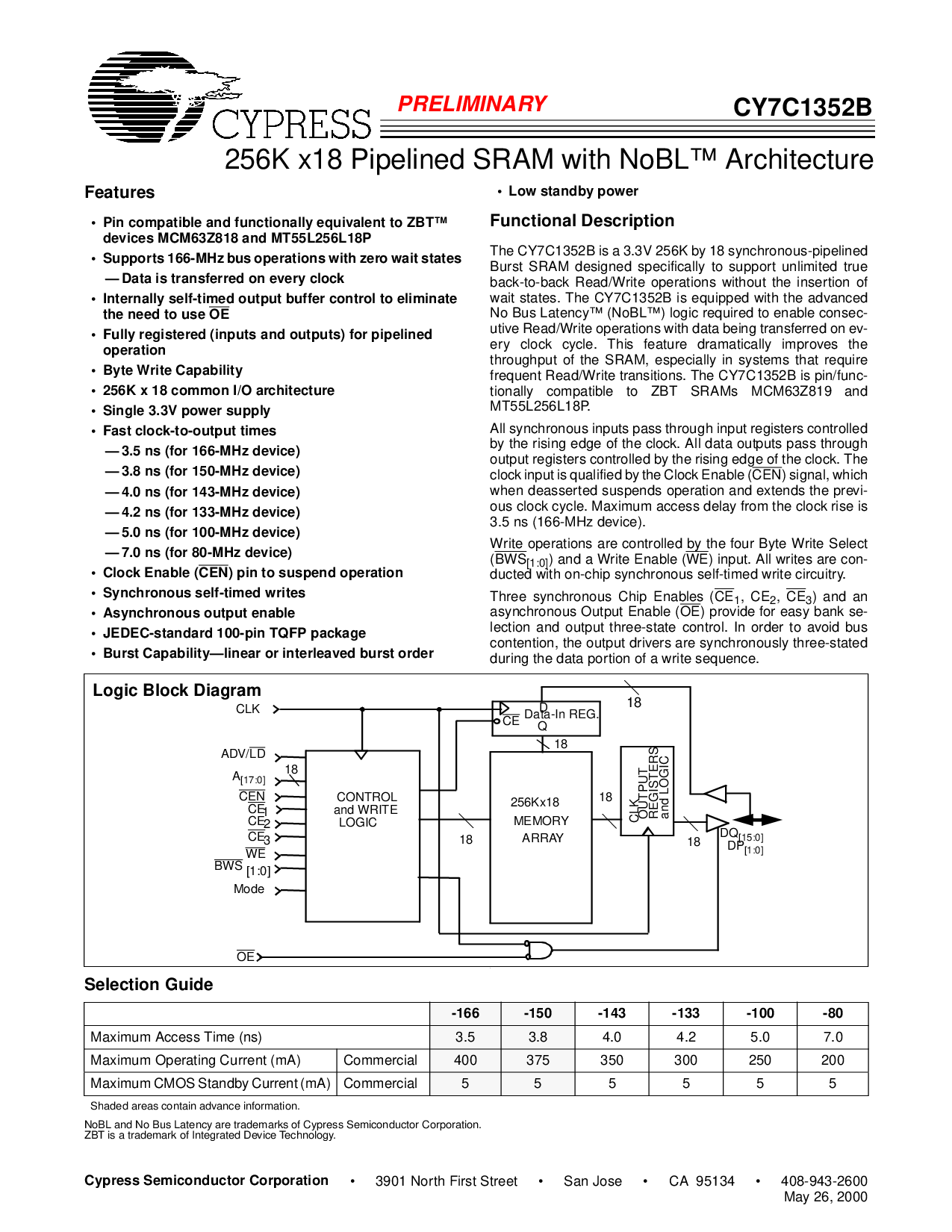

CLK

一个

[17:0]

CEN

我们

BWS

CE

1

CE

CE

2

OE

输出

256Kx18

记忆

排列

CLK

逻辑 块 图解

DQ

[15:0]

数据-在 reg.

Q

D

CE

控制

和 写

逻辑

3

[1:0]

寄存器

和 逻辑

adv/ld

18

18

18

18

18

18

DP

[1:0]

模式

选择 手册

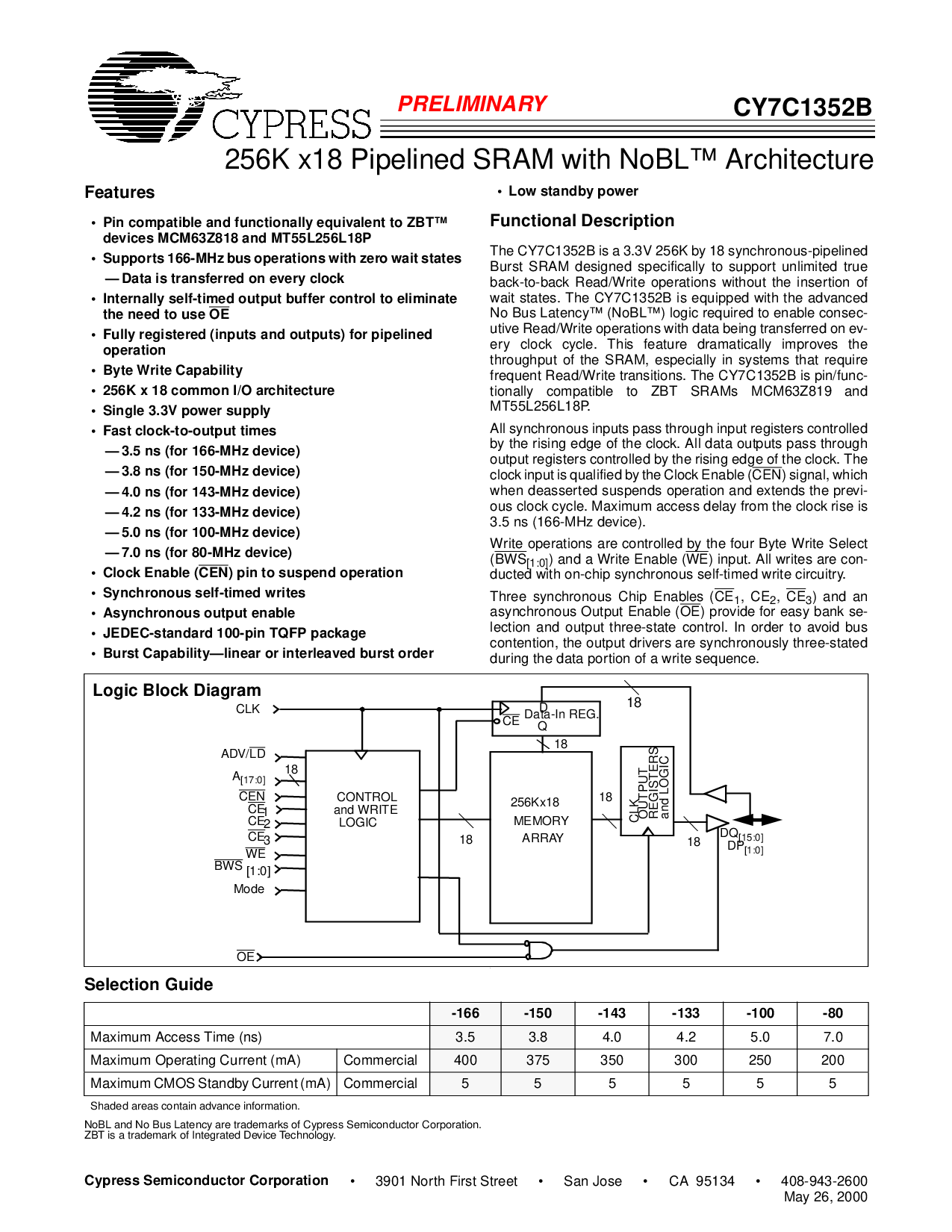

-166 -150 -143 -133 -100 -80

最大 进入 时间 (ns) 3.5 3.8 4.0 4.2 5.0 7.0

最大 运行 电流 (毫安) 商业的 400 375 350 300 250 200

最大 cmos 备用物品 电流 (毫安) 商业的 5 5555 5

shaded areas 包含 进步 信息.