MOTOROLA

半导体 技术的 数据

3–73

rev 5

motorola, 公司 1996

3/93

二进制的 至 1-8 解码器 (低)

这 mc10161 是 设计 至 decode 一个 三 位 输入 文字 至 一个 一个 的 eight

线条 输出. 这 选择 输出 将 是 低 当 所有 其它 输出 将 是 高. 这

使能 输入, 当 也 或者 两个都 是 高, 强迫 所有 输出 高.

这 mc10161 是 一个 真实 并行的 解码器. 非 序列 gating 是 使用 内部,

eliminating unequal 延迟 时间 建立 在 其它 decoders. 这个 设计 提供

这 完全同样的 4 ns 延迟 从 任何 地址 或者 使能 输入 至 任何 输出.

一个 完全 mux/demux 运作 在 16 位 为 数据 分发 是 illustrated

在 图示 1. 这个 系统, 使用 这 mc10136 控制 counters, 有 这

能力 的 incrementing, decrementing 或者 支持 数据 途径. 当 两个都

s0 和 s1 是 低, 这 index counters 重置, 因此 initializing 两个都 这 mux 和

demux 单位. 这 四 二进制的 输出 的 这 计数器 是 缓冲 用 这

mc10101s 至 send twisted–pair 选择 数据 至 这 多路调制器/demultiplexer 至

单位.

P

D

= 315 mw 典型值/pkg (非 加载)

t

pd

= 4.0 ns 典型值

t

r

, t

f

= 2.0 ns 典型值 (20%–80%)

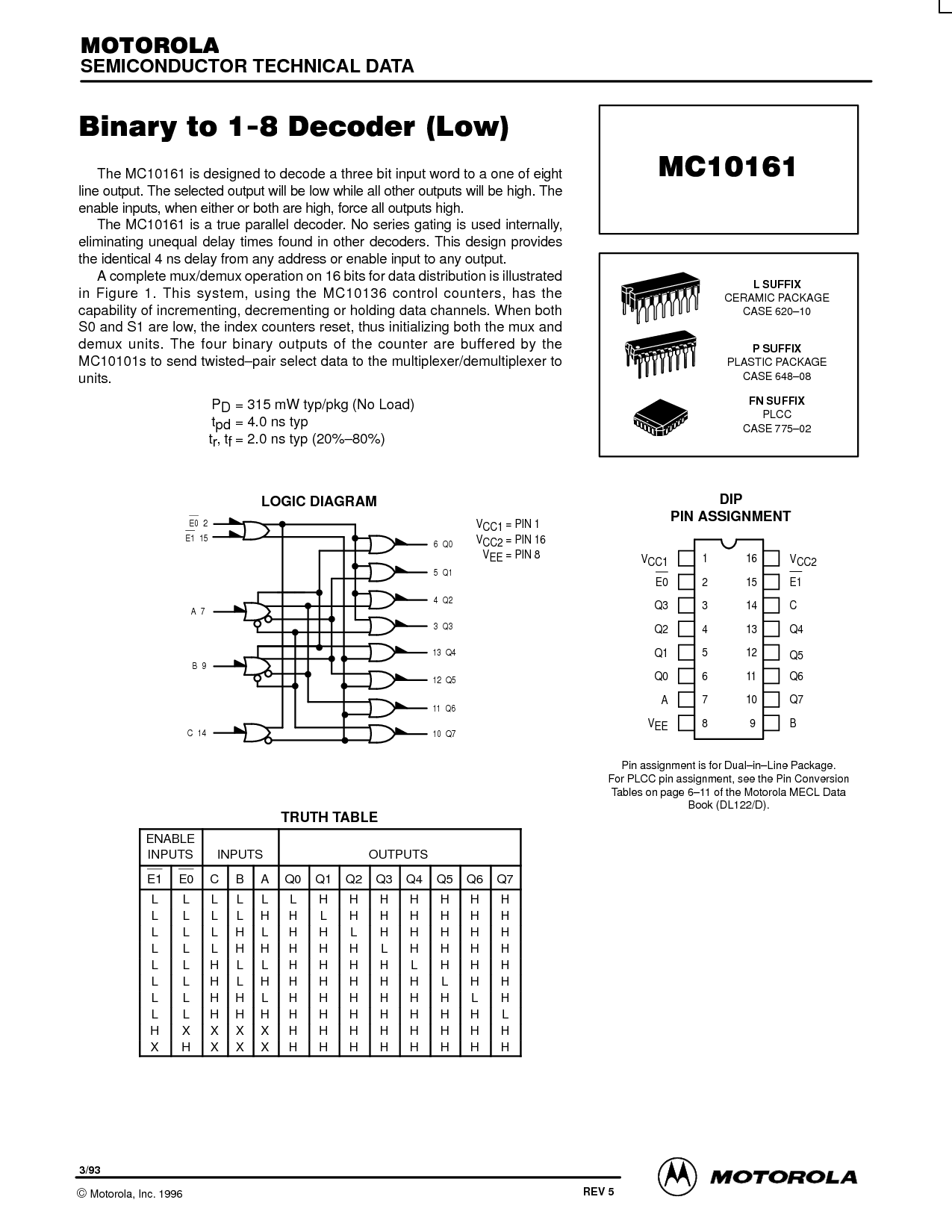

逻辑 图解

V

CC1

= 管脚 1

V

CC2

= 管脚 16

V

EE

= 管脚 8

E0 2

E1

15

A7

B9

C14

6Q0

5Q1

4Q2

3Q3

13 Q4

12 Q5

11 Q6

10 Q7

真实 表格

使能

输入

输入 输出

E1 E0 C B 一个 Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7

L L L L L L H H H H H H H

L L L L H H L H H H H H H

L L L H L H H L H H H H H

L L L H H H H H L H H H H

L L H L L H H H H L H H H

L L H L H H H H H H L H H

L L H H L H H H H H H L H

L L H H H H H H H H H H L

H X X X X H H H H H H H H

X H X X X H H H H H H H H

MC10161

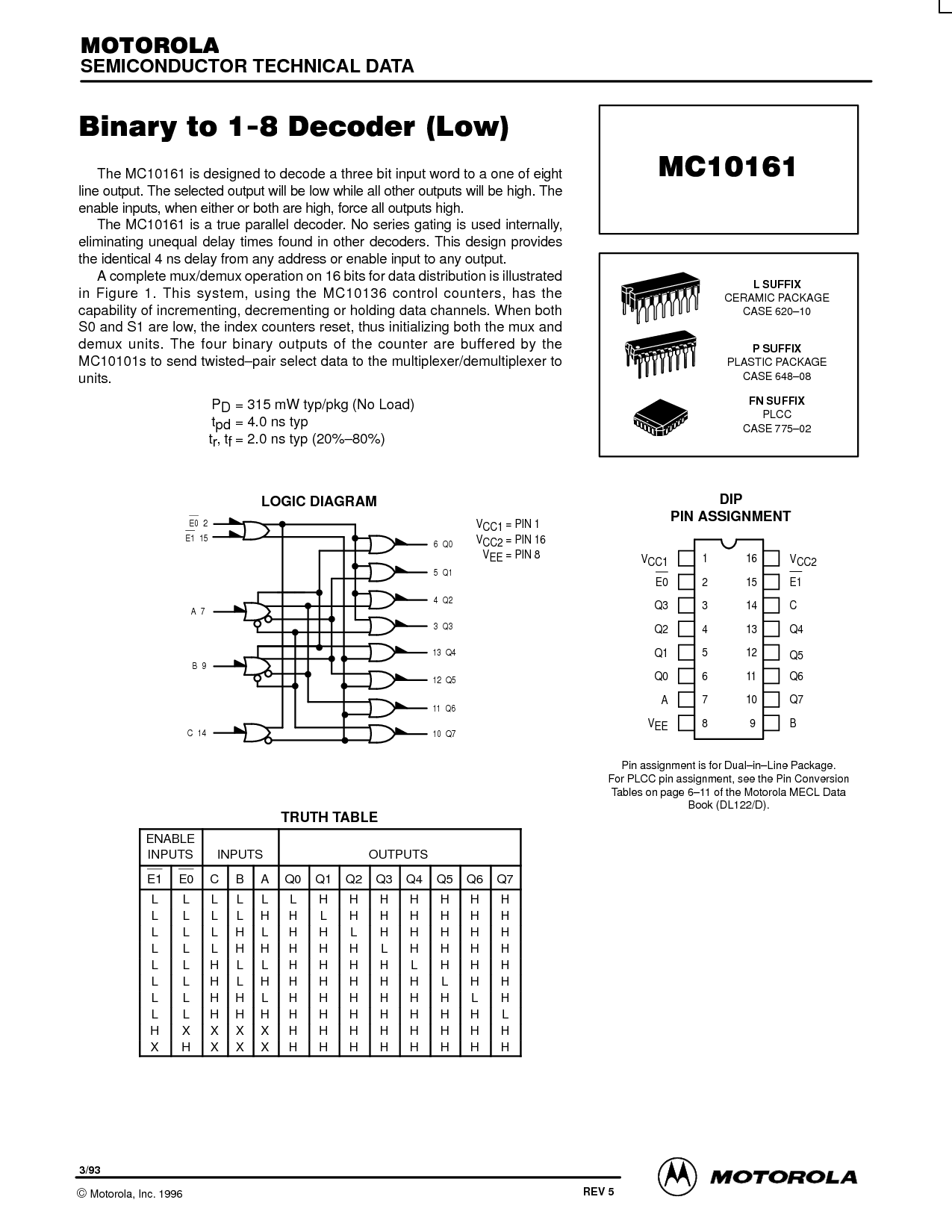

插件

管脚 分派

V

CC1

E0

Q3

Q2

Q1

Q0

一个

V

EE

V

CC2

E1

C

Q4

Q5

Q6

Q7

B

16

15

14

13

12

11

10

9

1

2

3

4

5

6

7

8

管脚 分派 是 为 dual–in–line 包装.

为 plcc 管脚 分派, 看 这 管脚 转换

tables 在 页 6–11 的 这 motorola mecl 数据

书 (dl122/d).

l 后缀

陶瓷的 包装

情况 620–10

p 后缀

塑料 包装

情况 648–08

fn 后缀

PLCC

情况 775–02