1/10december 2001

■

高 速: t

PD

= 3.8ns (典型值.) 在 v

CC

= 5v

■

低 电源 消耗:

I

CC

= 1

µ

一个(最大值.) 在 t

一个

=25°C

■

兼容 和 ttl 输出:

V

IH

= 2v (最小值), v

IL

= 0.8v (最大值)

■

电源 向下 保护 在 输入

和 输出

■

对称的 输出 阻抗:

|I

OH

| = i

OL

= 8ma (最小值)

■

保持平衡 传播 延迟:

t

PLH

≅

t

PHL

■

运行 电压 范围:

V

CC

(opr) = 4.5v 至 5.5v

■

改进 获得-向上 免除

描述

这 74v2t125 是 一个 先进的 高-速 cmos

双 总线 缓存区 fabricated 和 sub-micron

硅 门 和 翻倍-layer metal 线路 c

2

MOS

tecnology.

3-状态 控制 输入 ng

有 至 是 设置 高 至

放置 这 输出 在 这 高 阻抗 状态.

电源 向下 保护 是 提供 在 所有 输入

和 输出 和 0 至 7v 能 是 accepted 在

输入 和 非 关于 至 这 供应 电压. 这个

设备 能 是 使用 至 接口 3v 至 5v 系统

和 它 是 完美的 为 可携带的 产品 像

个人的 数字的 assistant, camcorder 和 所有

电池-powered 设备.

所有 输入 和 输出 是 配备 和

保护 电路 相反 静态的 释放, 给

它们 静电释放 免除 和 瞬时 excess 电压.

74V2T125

双 总线 缓存区 (3-状态)

这个 是 初步的 信息 在 一个 新 产品 now 在 开发 是 或者 undergoing evaluation. 详细信息 主题 至 改变 没有 注意.

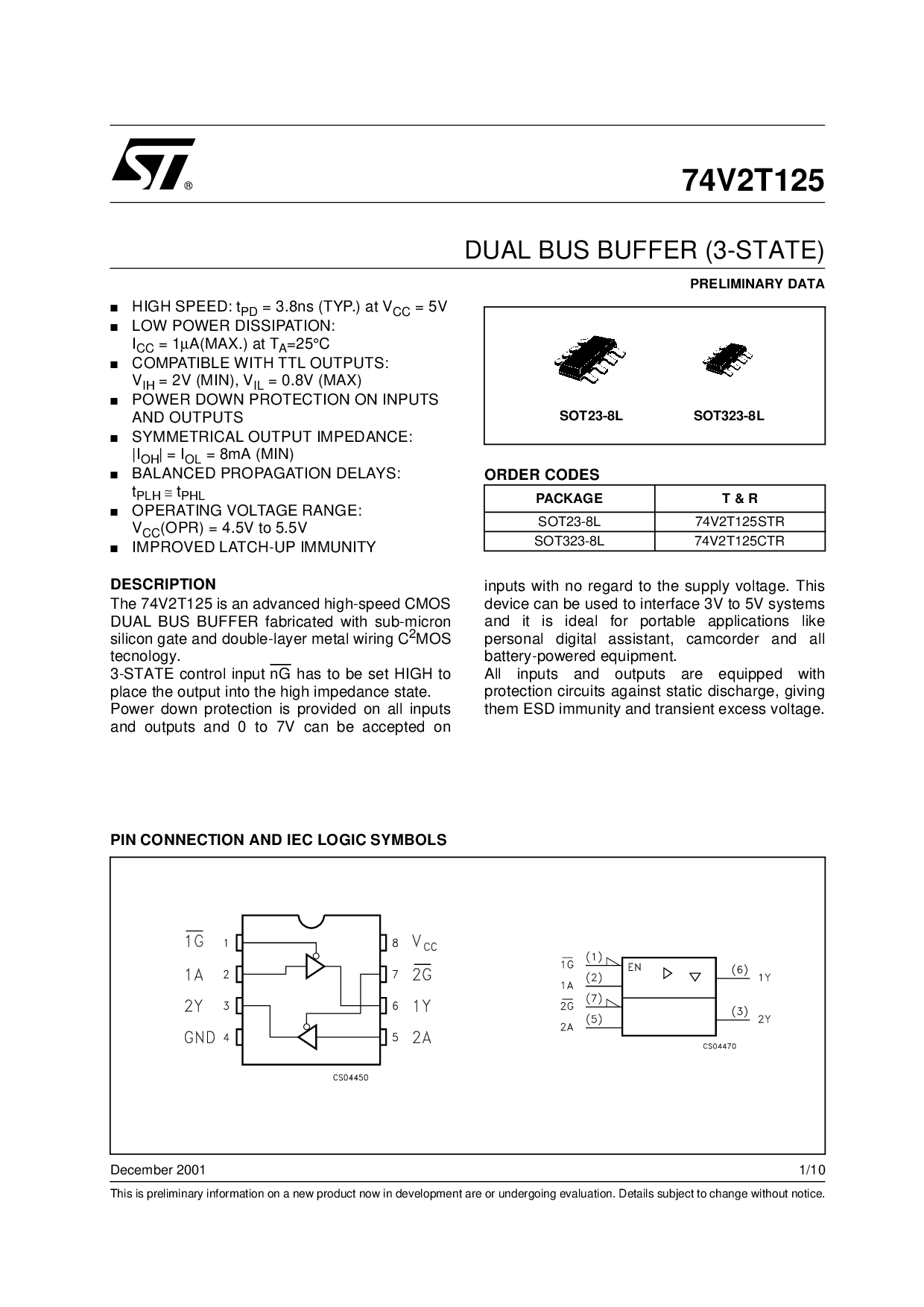

管脚 连接 和 iec 逻辑 symbols

顺序 代号

包装 t &放大; r

sot23-8l 74V2T125STR

sot323-8l 74V2T125CTR

sot23-8l sot323-8l

初步的 数据