1

© 1998 用 catalyst 半导体, 公司

特性 主题 至 改变 没有 注意

CAT28C16A

16k-位 cmos 并行的 e

2

PROM

特性

■

快 读 进入 时间: 200 ns

■

低 电源 cmos 消耗:

–active: 25 毫安 最大值

–standby: 100

µ

一个 最大值

■

简单的 写 运作:

–on-碎片 地址 和 数据 latches

–self-安排时间 写 循环 和 自动-clear

■

快 写 循环 时间: 10ms 最大值

■

终止 的 写 发现:

DATADATA

DATADATA

数据

Polling

■

硬件 写 保护

■

cmos 和 ttl 兼容 i/o

■

10,000 程序/擦掉 循环

■

10 年 数据 保持

■

商业的, 工业的 和 automotive

温度 范围

5089 fhd f02

描述

这 cat28c16a 是 一个 快, 低 电源, 5v-仅有的 cmos

并行的 e

2

prom 有组织的 作 2k x 8-位. 它 需要 一个

简单的 接口 为 在-系统 程序编制. 在-碎片

地址 和 数据 latches, 自-安排时间 写 循环 和

自动-clear 和 v

CC

电源 向上/向下 写 保护

eliminate 额外的 定时 和 保护 硬件.

数据

polling 信号 这 开始 和 终止 的 这 自-安排时间

写 循环. additionally, 这 cat28c16a 特性 hard-

ware 写 保护.

这 cat28c16a 是 制造的 使用 catalyst’s ad-

vanced cmos floating 门 技术. 它 是 设计 至

endure 10,000 程序/擦掉 循环 和 有 一个 数据

保持 的 10 年. 这 设备 是 有 在 电子元件工业联合会

批准 24-管脚 插件 和 soic 或者 32-管脚 plcc 包装-

ages.

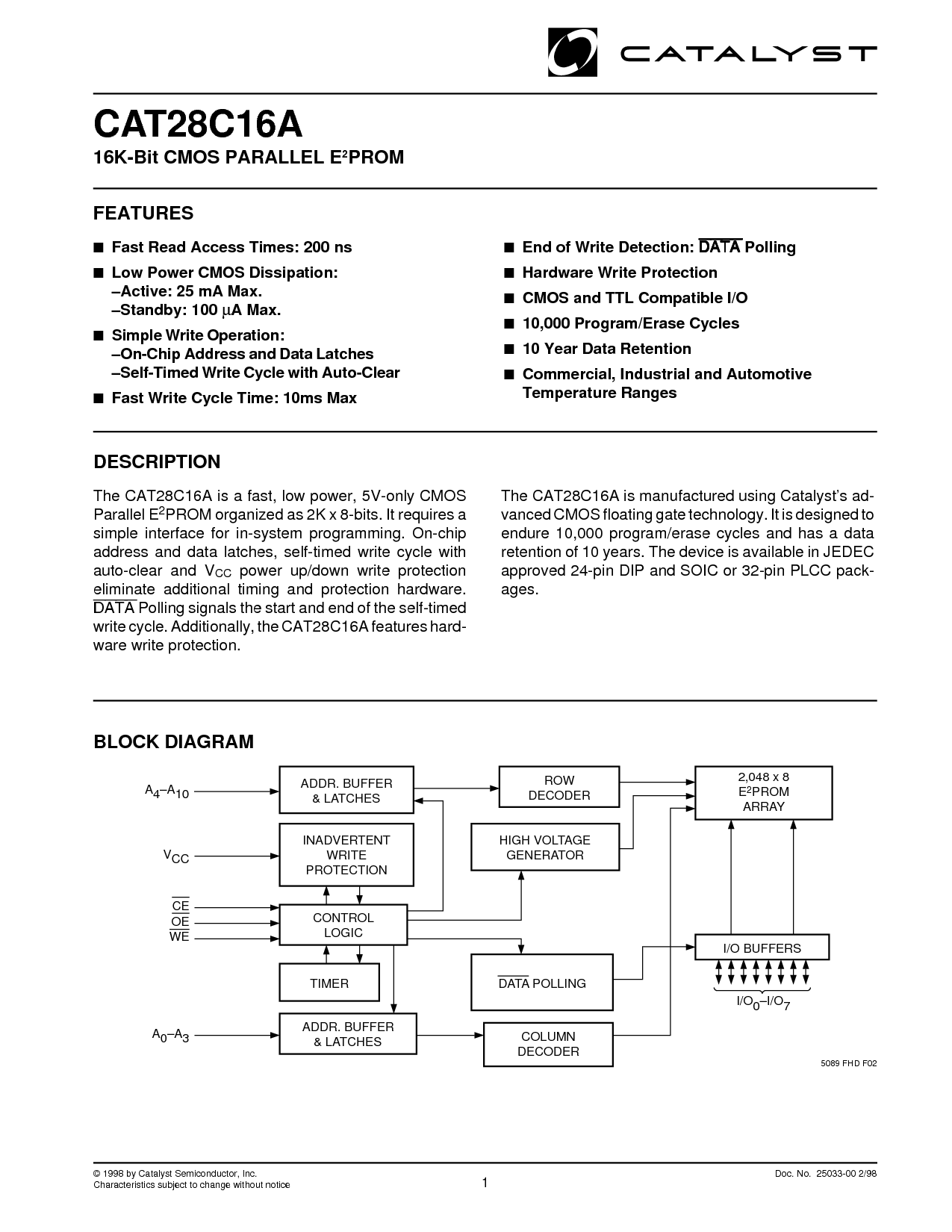

块 图解

地址. 缓存区

&放大; latches

地址. 缓存区

&放大; latches

INADVERTENT

写

保护

控制

逻辑

计时器

行

解码器

COLUMN

解码器

高 电压

发生器

一个

4

–A

10

CE

OE

我们

一个

0

–A

3

i/o

0

–i/o

7

i/o 缓存区

2,048 x 8

E

2

PROM

排列

V

CC

数据 polling

doc. 非. 25033-00 2/98