idt54/74fct88915tt 55/70/100/133

低 skew pll-为基础 时钟 驱动器 军队 和 商业的 温度 范围

9.7 1

整体的 设备 技术, 公司

这 idt 标志 是 一个 注册 商标 的 整体的 设备 技术, 公司

特性:

• 0.5 micron cmos 技术

• 输入 频率 范围: 10mhz – f2q 最大值 规格

(freq_sel = 高)

• 最大值 输出 频率: 133mhz

• 管脚 和 函数 兼容 和 mc88915t

• 5 非-反相的 输出, 一个 反相的 输出, 一个 2x

输出, 一个

÷

2 输出; 所有 输出 是 ttl-兼容

• 3-状态 输出

• 输出 skew < 500ps (最大值.)

• 职责 循环 扭曲量 < 500ps (最大值.)

• 部分-至-部分 skew: 1ns (从 t

PD

最大值 规格)

• ttl 水平的 输出 电压 摆动

• 64/–15ma 驱动 在 ttl 输出 电压 水平

• 有 在 28 管脚 plcc, lcc 和 ssop 包装

1

军队 和 商业的 温度 范围 8月 1995

1995 整体的 设备 技术, 公司

9.7

dsc-4247/1

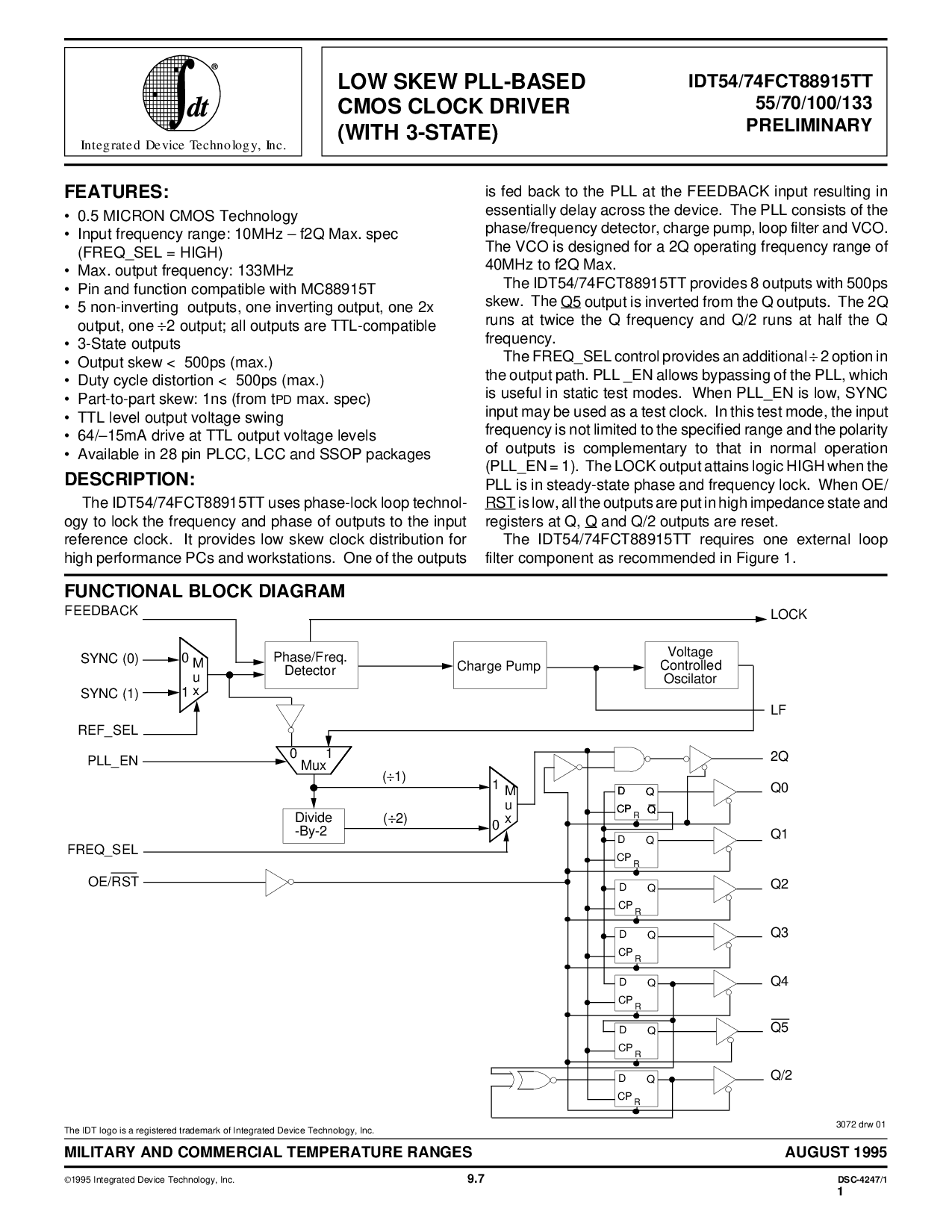

是 喂养 后面的 至 这 pll 在 这 反馈 输入 结果 在

essentially 延迟 横过 这 设备. 这 pll 组成 的 这

阶段/频率 探测器, 承担 打气, 循环 过滤 和 vco.

这 vco 是 设计 为 一个 2q 运行 频率 范围 的

40mhz 至 f2q 最大值

这 idt54/74fct88915tt 提供 8 输出 和 500ps

skew. 这

q5 输出 是 inverted 从 这 q 输出. 这 2q

runs 在 两次 这 q 频率 和 q/2 runs 在 half 这 q

频率.

这 freq_sel 控制 提供 一个 额外的

÷

2 选项 在

这 输出 path. pll _en 准许 bypassing 的 这 pll, 这个

是 有用的 在 静态的 测试 模式. 当 pll_en 是 低, 同步

输入 将 是 使用 作 一个 测试 时钟. 在 这个 测试 模式, 这 输入

频率 是 不 限制 至 这 指定 范围 和 这 极性

的 输出 是 complementary 至 那 在 正常的 运作

(pll_en = 1). 这 锁 输出 attains 逻辑 高 当 这

pll 是 在 稳步的-状态 阶段 和 频率 锁. 当 oe/

rst 是 低, 所有 这 输出 是 放 在 高 阻抗 状态 和

寄存器 在 q, q 和 q/2 输出 是 重置.

这 idt54/74fct88915tt 需要 一个 外部 循环

过滤 组件 作 推荐 在 图示 1.

idt54/74fct88915tt

55/70/100/133

初步的

低 skew pll-为基础

cmos 时钟 驱动器

(和 3-状态)

函数的 块 图解

描述:

这 idt54/74fct88915tt 使用 阶段-锁 循环 technol-

ogy 至 锁 这 频率 和 阶段 的 输出 至 这 输入

涉及 时钟. 它 提供 低 skew 时钟 分发 为

高 效能 pcs 和 workstations. 一个 的 这 输出

阶段/freq.

探测器

M

u

x

0

1

同步 (0)

反馈

同步 (1)

ref_sel

pll_en

Mux

01

分隔

-用-2

(

÷

1)

(

÷

2)

1

0

M

u

x

承担 打气

电压

控制

Oscilator

oe/rst

freq_sel

2Q

Q0

Q1

Q2

Q3

Q4

Q5

q/2

D

Q

CP

Q

R

D

Q

CP

Q

R

D

Q

CP

R

D

Q

CP

R

D

Q

CP

R

D

Q

CP

R

D

Q

CP

R

D

Q

CP

LF

锁

3072 drw 01