pmc-1991025 (r2)

专卖的 和 confidential 至 pmc-sierra, inc., 和 为 它的 客户’ 内部的 使用

2001

pmc-sierra, 公司

PM7385

pmc-sierra,公司

框架 engine 和 数据 link manager

freedm-84a672

特性

• 单独的-碎片 multi-频道 hdlc

控制 和 一个 50 mhz, 16 位 任何-

phy™ 小包装板盒 接口 (appi) 为

转移 的 小包装板盒 数据 使用 一个

外部 控制.

• 支持 向上 至 672 bi-directional

hdlc 途径 assigned 至 一个

最大 的 84 channelised 或者

unchannelised links conveyed 通过 一个

19.44 mhz 可称量的 带宽

interconnect (sbi™) 接口.

• 数据 在 这 sbi 接口 是 分隔

在 三 同步的 payload

envelopes (spes). 各自 spe 能 是

配置 independently 至 carry 数据

为 也 28 t1/j1 links, 21 e1 links, 或者

一个 unchannelised ds-3 link.

• 支持 三 bi-directional hdlc

途径 各自 assigned 至 一个

unchannelised link 和 arbitrary 比率

link 的 向上 至 51.84 mhz 当 sysclk

是 运动 在 45 mhz. 各自 link 将 是

配置 individually 至 替代 一个

的 这 spes conveyed 在 这 sbi

接口.

• 为 各自 频道, 这 hdlc 接受者

支持 可编程序的 标记 sequence

发现, 位 de-stuffing 和 框架

审查 sequence validation. 这

接受者 支持 这 validation 的 两个都

crc-ccitt 和 crc-32 框架 审查

sequences.

• 为 各自 频道, 这 hdlc

传输者 支持 可编程序的

标记 sequence 一代, 位 stuffing

和 框架 审查 sequence 一代.

这 传输者 支持 这

一代 的 两个都 crc-ccitt 和

crc-32 框架 审查 sequences. 这

传输者 也 aborts packets 下面

这 方向 的 这 外部 控制

或者 automatically 当 这 频道

underflows.

• 提供 32 kbytes 的 在-碎片 记忆

为 partial 小包装板盒 buffering 在 两个都 这

transmit 和 这 receive 方向.

这个 记忆 将 是 配置 至

支持 一个 多样性 的 不同的 频道

配置 从 一个 单独的 频道

和 32 kbytes 的 buffering 至 672

途径, 各自 和 一个 最小 的 48

字节 的 buffering.

• 提供 一个 16 位 微处理器

接口 为 配置 和 状态

monitoring.

• 提供 一个 标准 five 信号

p1149.1 jtag 测试 端口 为 boundary

scan 板 测试 目的.

• 支持 3.3 volt tolerant i/o.

• 352 管脚 增强 球 grid 排列

(sbga) 包装.

产品

• ppp 接口 为 routers.

• 互联网/边缘 routers.

• 框架 接转/multiservice switches.

• 小包装板盒-为基础 dslam 设备.

• 偏远的 进入 concentrators.

• multiservice 进入 concentrators.

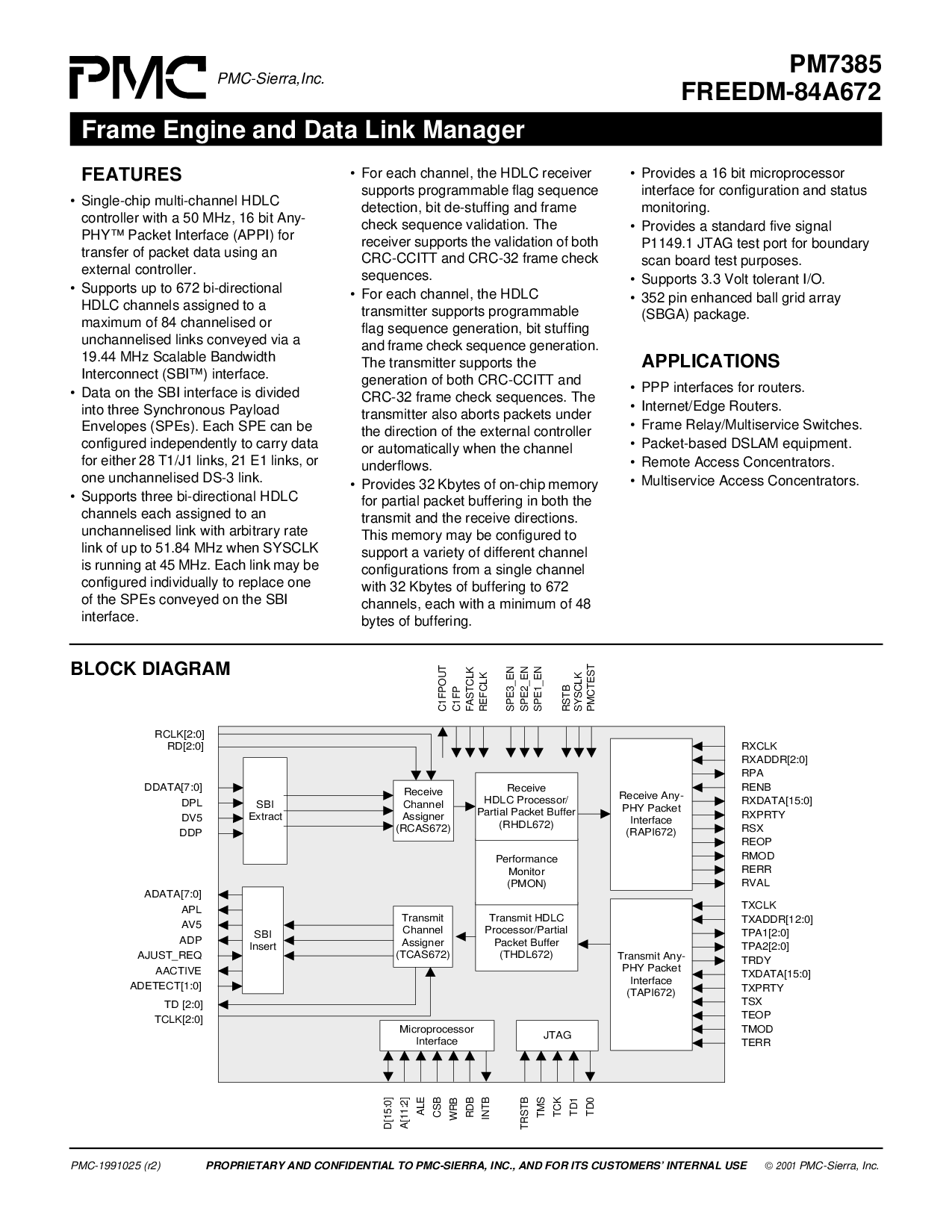

ddata[7:0]

DPL

DV5

DDP

SBI

Extract

SBI

Insert

transmit hdlc

处理器/partial

小包装板盒 缓存区

(thdl672)

效能

监控

(pmon)

adata[7:0]

APL

AV5

ADP

ajust_req

AACTIVE

adetect[1:0]

Receive

频道

Assigner

(rcas672)

Transmit

频道

Assigner

(tcas672)

Receive

hdlc 处理器/

partial 小包装板盒 缓存区

(rhdl672)

tclk[2:0]

td [2:0]

JTAG

TD0

TD1

TCK

TMS

TRSTB

rd[2:0]

rclk[2:0]

spe1_en

spe2_en

spe3_en

REFCLK

FASTCLK

C1FP

C1FPOUT

微处理器

接口

WRB

CSB

ALE

a[11:2]

d[15:0]

INTB

RDB

transmit 任何-

phy 小包装板盒

接口

(tapi672)

txaddr[12:0]

TXCLK

tpa1[2:0]

tpa2[2:0]

TRDY

txdata[15:0]

TXPRTY

TSX

TEOP

TMOD

TERR

receive 任何-

phy 小包装板盒

接口

(rapi672)

rxaddr[2:0]

RXCLK

RPA

RENB

rxdata[15:0]

RXPRTY

RSX

REOP

RMOD

RERR

RVAL

RSTB

SYSCLK

PMCTEST

块 图解