1/11february 2003

■

高 速:

f

最大值

= 185 MHz (典型值.) 在 V

CC

=5V

■

低 电源 消耗:

I

CC

=4

µ

一个 (最大值.) 在 T

一个

=25°C

■

高 噪音 免除:

V

NIH

=V

NIL

= 28% V

CC

(最小值.)

■

电源 向下 保护 在 输入

■

对称的 输出 阻抗:

|I

OH

|=I

OL

=8ma(最小值)

■

保持平衡 传播 延迟:

t

PLH

≅

t

PHL

■

运行 电压 范围:

V

CC

(opr) = 2V 至 5.5v

■

管脚 和 函数 兼容 和

74 序列 16374

■

改进 获得-向上 免除

■

低 噪音: V

OLP

= 0.9v (最大值.)

描述

这 74VHC16374 是 一个 先进的 高-速

FLIP FLOP 和 3 状态 输出 非

反相的 fabricated 和 sub-micron 硅

门 和 翻倍-layer metal 线路 C

2

MOS

技术.

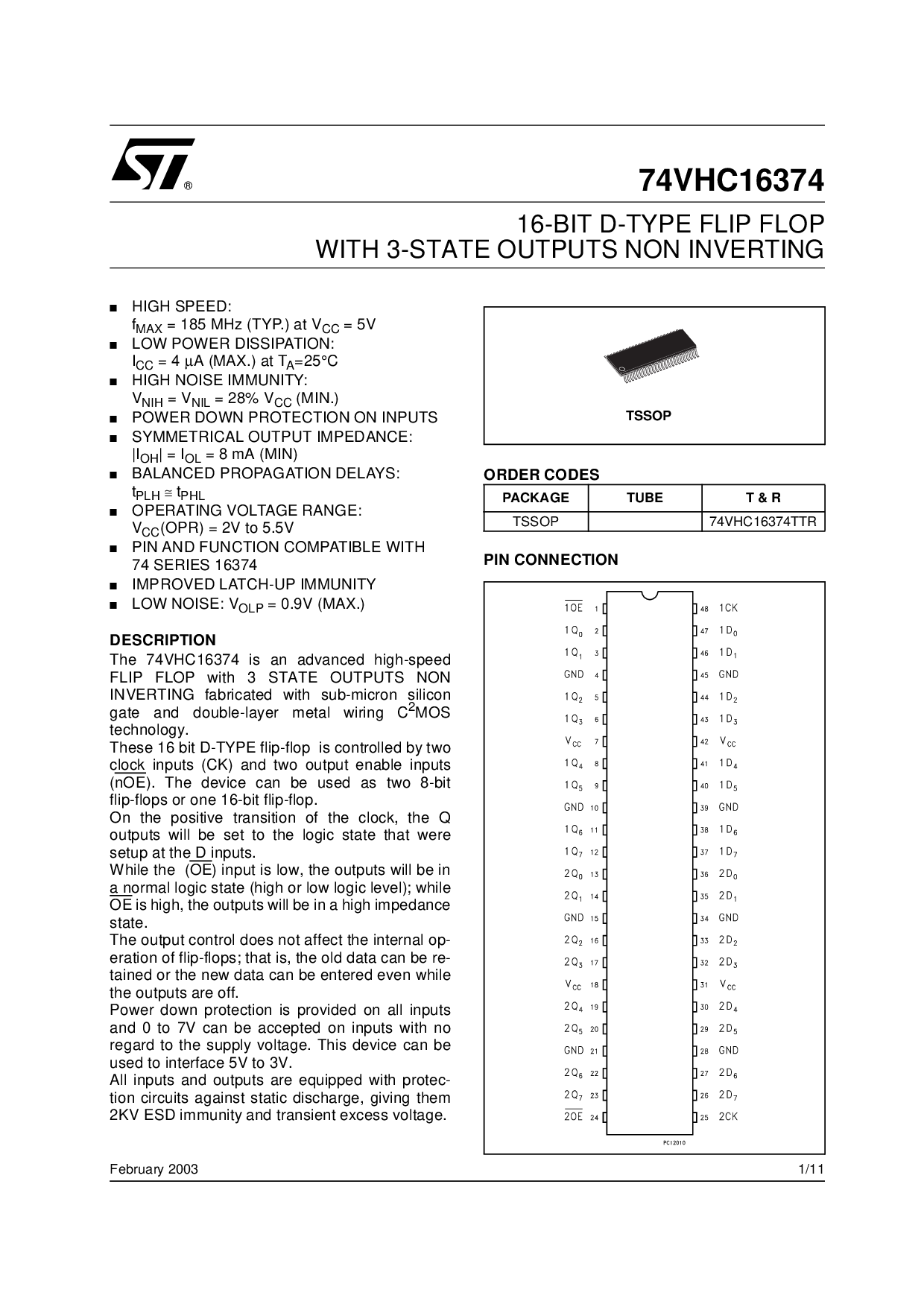

这些 16 位 d-类型 flip-flop 是 控制 用 二

时钟 输入 (ck) 和 二 输出 使能 输入

(非E

). 这 设备 能 是 使用 作 二 8-位

flip-flops 或者 一个 16-位 flip-flop.

在 这 积极的 转变 的 这 时钟, 这 Q

输出 将 是 设置 至 这 逻辑 状态 那 是

建制 在 这 D 输入.

当 这 (oe

) 输入 是 低, 这 输出 将 是 在

一个 正常的 逻辑 状态 (高 或者 低 逻辑 水平的); 当

OE

是 高, 这 输出 将 是 在 一个 高 阻抗

状态.

这 输出 控制 做 不 影响 这 内部的 运算-

限定 的 flip-flops; 那 是, 这 old 数据 能 是 re-

tained 或者 这 新 数据 能 是 entered 甚至 当

这 输出 是 止.

电源 向下 保护 是 提供 在 所有 输入

和 0 至 7V 能 是 accepted 在 输入 和 非

关于 至 这 供应 电压. 这个 设备 能 是

使用 至 接口 5V 至 3v.

所有 输入 和 输出 是 配备 和 protec-

tion 电路 相反 静态的 释放, 给 它们

2KV 静电释放 免除 和 瞬时 excess 电压.

74VHC16374

16-位 d-类型 FLIP FLOP

和 3-状态 输出 非 反相的

顺序 代号

包装 TUBE T &放大; R

TSSOP 74VHC16374TTR

TSSOP

管脚 连接