®

altera 公司 745

Classic

epld 家族

将 1999, ver. 5 数据 薄板

一个-ds-classic-05

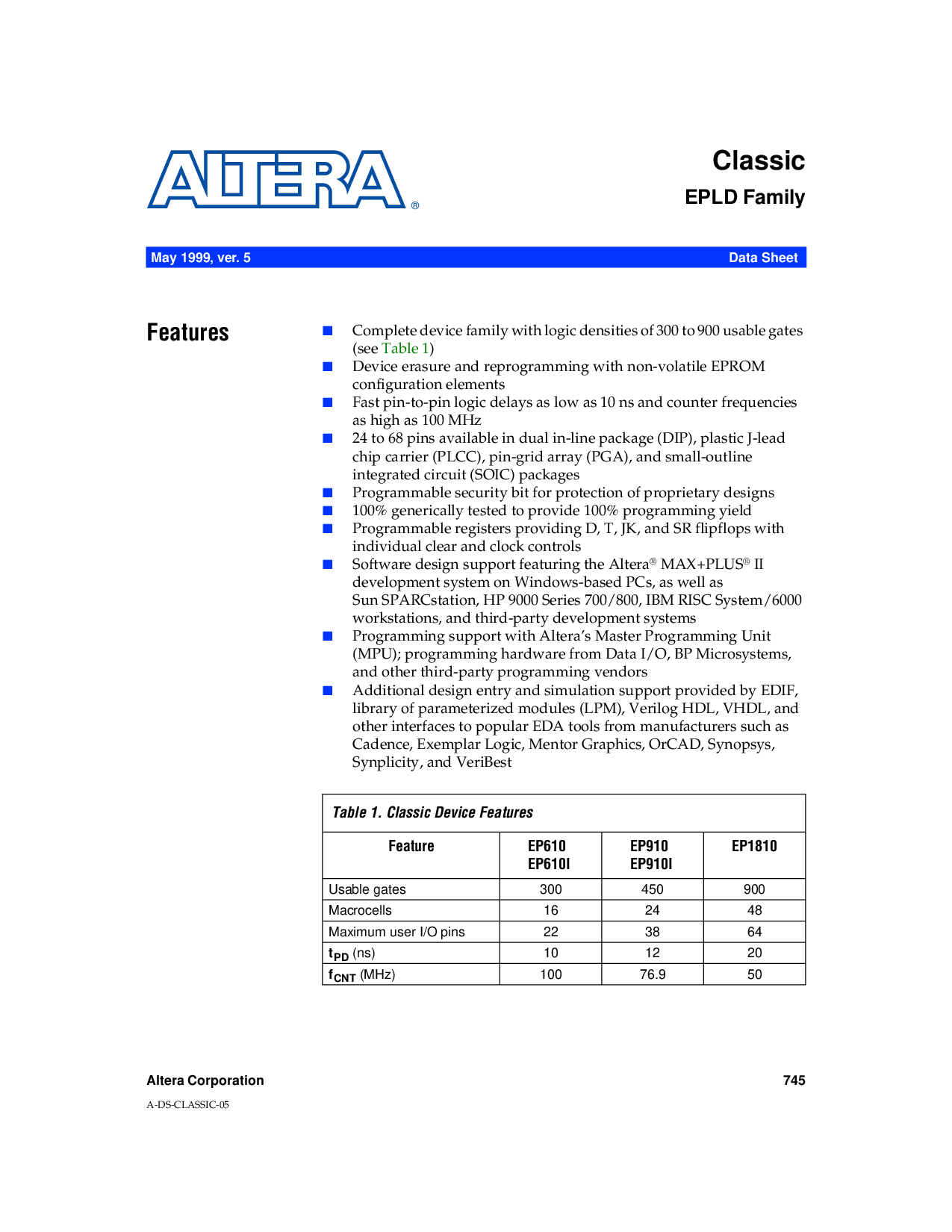

特性

■

完全 设备 家族 和 逻辑 densities 的 300 至 900 usable 门

(看表格 1)

■

设备 erasure 和 reprogramming 和 非-易变的 非易失存储器

配置 elements

■

快 管脚-至-管脚 逻辑 延迟 作 低 作 10 ns 和 计数器 发生率

作 高 作 100 mhz

■

24 至 68 管脚 有 在 双 在-线条 包装 (插件), 塑料 j-含铅的

碎片 运输车 (plcc), 管脚-grid 排列 (pga), 和 小-外形

整体的 电路 (soic) 包装

■

可编程序的 安全 位 为 保护 的 专卖的 设计

■

100

%

generically 测试 至 提供 100

%

程序编制 yield

■

可编程序的 寄存器 供应 d, t, jk, 和 sr flipflops 和

单独的 clear 和 时钟 控制

■

软件 设计 支持 featuring 这 altera

®

MAX+PLUS

®

II

开发 系统 在 windows-为基础 pcs, 作 好 作

sun sparcstation, hp 9000 序列 700/800, ibm risc 系统/6000

workstations, 和 第三-群 开发 系统

■

程序编制 支持 和 altera’s 主控 程序编制 单位

(mpu); 程序编制 硬件 从 数据 i/o, bp microsystems,

和 其它 第三-群 程序编制 vendors

■

额外的 设计 entry 和 simulation 支持 提供 用 edif,

库 的 parameterized modules (lpm), verilog hdl, vhdl, 和

其它 接口 至 popular eda tools 从 manufacturers 此类 作

cadence, exemplar 逻辑, mentor graphics, orcad, synopsys,

synplicity, 和 veribest

表格 1. classic 设备 特性

特性 EP610

EP610I

EP910

EP910I

EP1810

usable 门 300 450 900

Macrocells 16 24 48

最大 用户 i/o 管脚 22 38 64

t

PD

(ns) 10 12 20

f

CNT

(mhz) 100 76.9 50