rev. 0

信息 陈设 用 相似物 设备 是 相信 至 是 精确 和

可依靠的. 不管怎样, 非 责任 是 assumed 用 相似物 设备 为 它的

使用, 也不 为 任何 infringements 的 专利权 或者 其它 权利 的 第三 部

这个将结果从它的使用.非执照是准予用牵涉或者

否则 下面 任何 专利权 或者 专利权 权利 的 相似物 设备.

一个

adsp-2185m

一个 技术 方法, p.o. 盒 9106, norwood, 毫安 02062-9106, 美国

电话: 781/329-4700 world 宽 网 站点: http://www.相似物.com

传真: 781/326-8703 © 相似物 设备, inc., 2000

DSP

Microcomputer

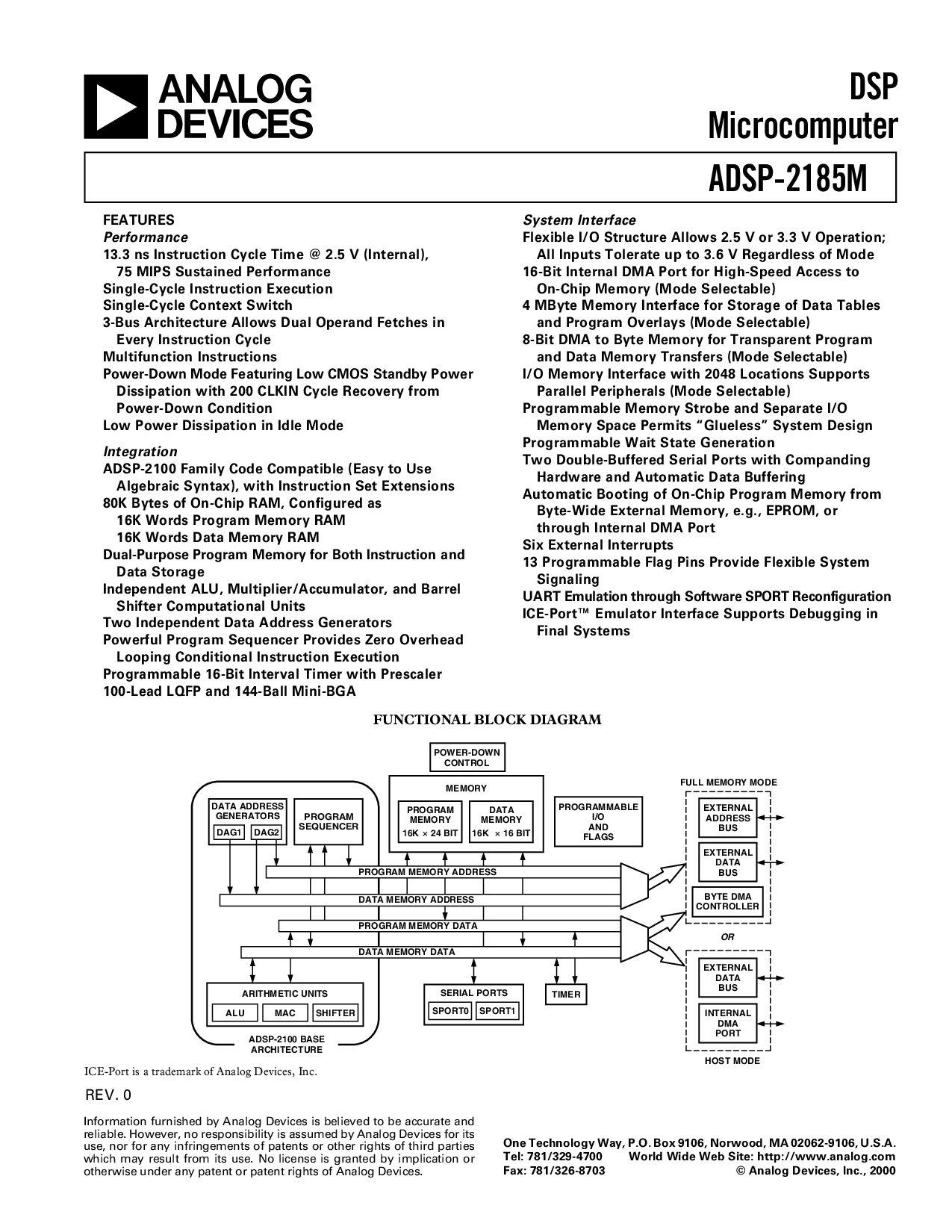

函数的 块 图解

arithmetic 单位

SHIFTERMACALU

程序 记忆 地址

数据 记忆 地址

程序 记忆 数据

数据 记忆 数据

电源-向下

控制

记忆

程序

记忆

16K

24 位

数据

记忆

16K

16 位

外部

地址

总线

外部

数据

总线

字节 dma

控制

全部 记忆 模式

SPORT0

串行 端口

SPORT1

可编程序的

i/o

和

FLAGS

计时器

host 模式

或者

外部

数据

总线

内部的

DMA

端口

DAG1

数据 地址

发生器

DAG2

程序

SEQUENCER

adsp-2100 根基

ARCHITECTURE

ice-端口 是 一个 商标 的 相似物 设备, 公司

特性

效能

13.3 ns 操作指南 循环 时间 @ 2.5 v (内部的),

75 mips sustained 效能

单独的-循环 操作指南 执行

单独的-循环 context 转变

3-总线 architecture 准许 双 operand fetches 在

每 操作指南 循环

multifunction 说明

电源-向下 模式 featuring 低 cmos 备用物品电源

消耗 和 200 clkin 循环 恢复 从

电源-向下 情况

低 电源 消耗 在 空闲 模式

Integration

adsp-2100 家族 代号 兼容 (容易 至 使用

algebraic syntax), 和 操作指南 设置 extensions

80k 字节 的 在-碎片 内存, 配置 作

16k words 程序 记忆 内存

16k words 数据 记忆 内存

双-目的 程序 记忆 为 两个都 操作指南 和

数据 存储

独立 alu, 乘法器/accumulator, 和 barrel

shifter computational 单位

二 独立 数据 地址 发生器

powerful 程序 sequencer 提供 零 overhead

looping conditional 操作指南 执行

可编程序的 16-位 间隔 计时器 和 预分频器

100-含铅的 lqfp 和 144-球 迷你-bga

系统 接口

有伸缩性的 i/o 结构 准许 2.5 v 或者 3.3 v 运作;

所有 输入 tolerate 向上 至 3.6 v regardless 的 模式

16-位 内部的 dma 端口 为 高-速 进入 至

在-碎片 记忆 (模式 可选择的)

4 mbyte 记忆 接口 为 存储 的 数据 tables

和 程序 overlays (模式 可选择的)

8-位 dma 至 字节 记忆 为 transparent 程序

和 数据 记忆 transfers (模式 可选择的)

i/o 记忆 接口 和 2048 locations 支持

并行的 peripherals (模式 可选择的)

可编程序的 记忆 strobe 和 独立的 i/o

记忆 空间 准许 “glueless” 系统 设计

可编程序的 wait 状态 一代

二 翻倍-缓冲 串行 端口 和 companding

硬件 和 自动 数据 buffering

自动 booting 的 在-碎片 程序 记忆 从

字节-宽 外部 记忆, e.g., 非易失存储器, 或者

通过 内部的 dma 端口

六 外部 中断

13 可编程序的 标记 管脚 提供 有伸缩性的 系统

Signaling

uart emulation 通过 软件 sport reconfiguration

ice-port™ emulator 接口 支持 debugging 在

最终 系统