一个

sharc 和 这 sharc 标志 是 注册商标 的 analog 设备, 公司

SHARC

®

embedded 处理器

adsp-21262

rev. b

信息 陈设 用 相似物 设备 是相信 至 是 精确 和 可依靠的.

不管怎样, 非 责任 是 assumed 用 相似物 设备 为 它的 使用, 也不 为 任何

infringements 的 专利权 或者 其它 权利 的 第三 部 那 将 结果 从 它的 使用.

规格 主题 至 改变 没有 非tice. 非 执照 是 准予 用 牵涉

或者 否则 下面 任何 专利权 或者 专利权 权利 的 相似物 设备. 商标 和

注册 商标 是 这 所有物 的 它们的 各自的 所有权人.

一个 技术 方法, p.o. 盒 9106, norwood, 毫安 02062-9106, 美国

电话: 781.329.4700 www.相似物.com

传真: 781.461.3113 © 2005 相似物 设备, 公司 所有 权利 保留.

SUMMARY

高 效能 32-位/40-bit floating-要点 处理器

代号 compatibility—at 组装 水平的, 使用 这 一样

操作指南 设置 作 其它 sharc dsps

单独的-操作指南 多样的-数据 (simd) computational archi-

tecture—two 32-位 ieee floating-要点/32-位 fixed-要点/

40-位 扩展 精确 floating-要点 computational

单位, 各自 和 一个 乘法器, alu, shifter, 和 寄存器 文件

高 带宽 i/o—a 并行的 端口, 一个 spi

®

端口, 六 串行

端口, 一个 数字的 产品接口 (dai), 和 jtag

dai 包含 二 精确 时钟 发生器 (pcgs), 一个

输入 数据 端口 (idp) 那 包含 一个 并行的 数据 acquisi-

tion 端口 (pdap), 和 三 可编程序的 计时器, 所有

下面 软件 控制 用 这 信号 routing 单位 (sru)

在-碎片 memory—2m 位 的 在-碎片 sram 和 一个 专心致志的

4m 位 的 在-碎片 掩饰-可编程序的 只读存储器

这 adsp-21262 是 有 在 商业的 和 工业的

温度 grades. 为 完全 订货 信息,

看订货 手册 在 页 46.

关键 特性

串行 端口 提供 left-justified 样本-一双 和 i

2

s 支持

通过 12 可编程序的 和 同时发生的 receive 或者 trans-

mit 管脚, 这个 支持 向上 至 24 transmit 或者 24 receive i

2

S

途径 的 音频的 当 所有 六 串行 端口 (sports) 是

使能 或者 六 全部 duplex tdm streams 的 向上 至 128

途径 每 框架

在 200 mhz (5 ns) 核心 操作指南 比率, 这 adsp-21262

运作 在 1200 mflops 顶峰/800 mflops sustained

效能 whether 运行 在 fixed- 或者 floating-要点

数据

400 mmacs sustained 效能 在 200 mhz

超级的 harvard architecture—three 独立 buses 为

双 数据 fetch, 操作指南fetch, 和 nonintrusive, 零-

overhead i/o

transfers 在 记忆 和 核心 在 向上 至 四 32-位

floating- 或者 fixed-要点 words 每 循环, sustained

2.4g 字节/s 带宽 在 200 mhz 核心 操作指南 比率

和 900m 字节/秒 是 有 通过 dma

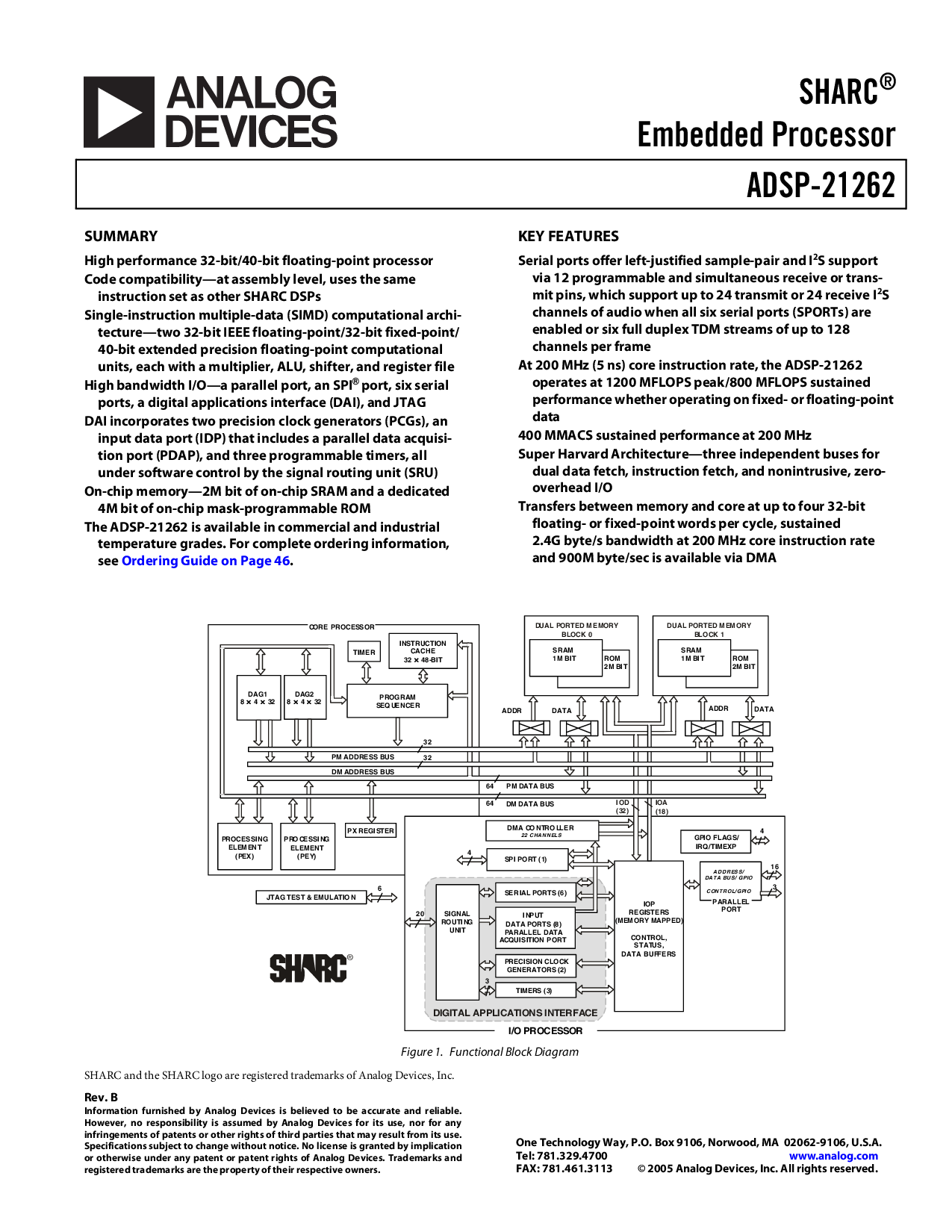

图示 1. 函数al 块 图解

地址

数据

PX寄存器

6

JTAG 测试 &放大; EMULATION

20

3

SERIAL 端口 (6)

输入

数据 端口 (8)

并行的 数据

ACQUISITION 端口

计时器 (3)

SI GNAL

RO U 德州仪器 NG

单位

PRECISI 在 CLO CK

发生器 (2)

数字的 产品 接口

3

16

地址/

数据 总线/ GPIO

控制/gpio

并行的

端口

IOP

寄存器

(记忆 编排)

控制,

状态,

数据 缓存区

4

SPI PO RT (1)

DMA 控制

22 途径

4

GPIO 标记 s/

IRQ /timexp

处理

元素

(pey)

PROCESSING

ELEM ENT

(pex)

计时器

操作指南

CACHE

32

48-位

DAG1

8

4

32

DAG2

8

4

32

32

PM 地址 总线

DM 地址 总线

PM 数据 总线

DM 数据 总线

64

64

核心 处理器

程序

SEQ UE NCE R

地址 数据

SRAM

1M 位 只读存储器

2M 位

双 PORTED 记忆

块 0

SRAM

1M 位 只读存储器

2M 位

双 PORTED 记忆

BLO CK 1

S

IOD

(32)

IOA

(18)

32

i/o 处理器