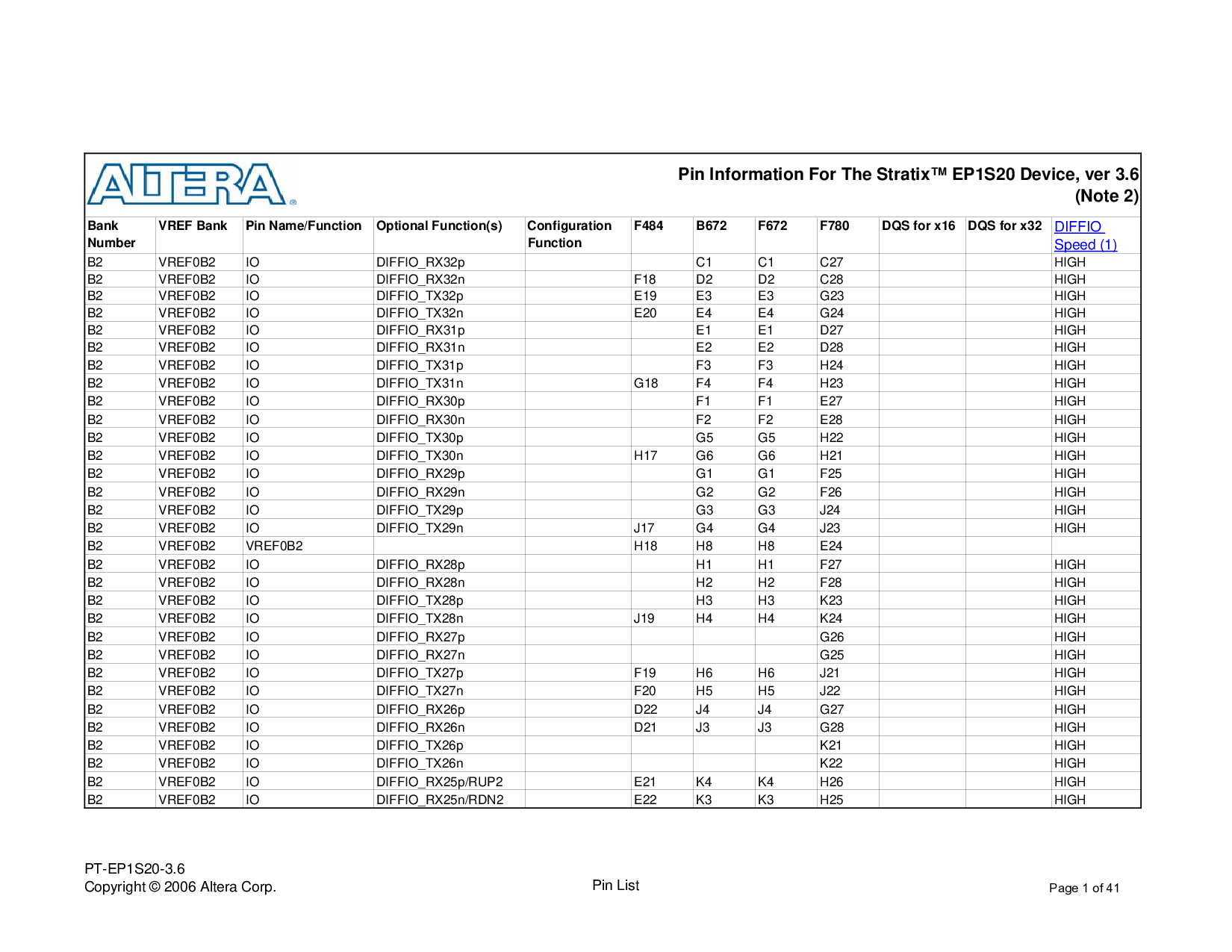

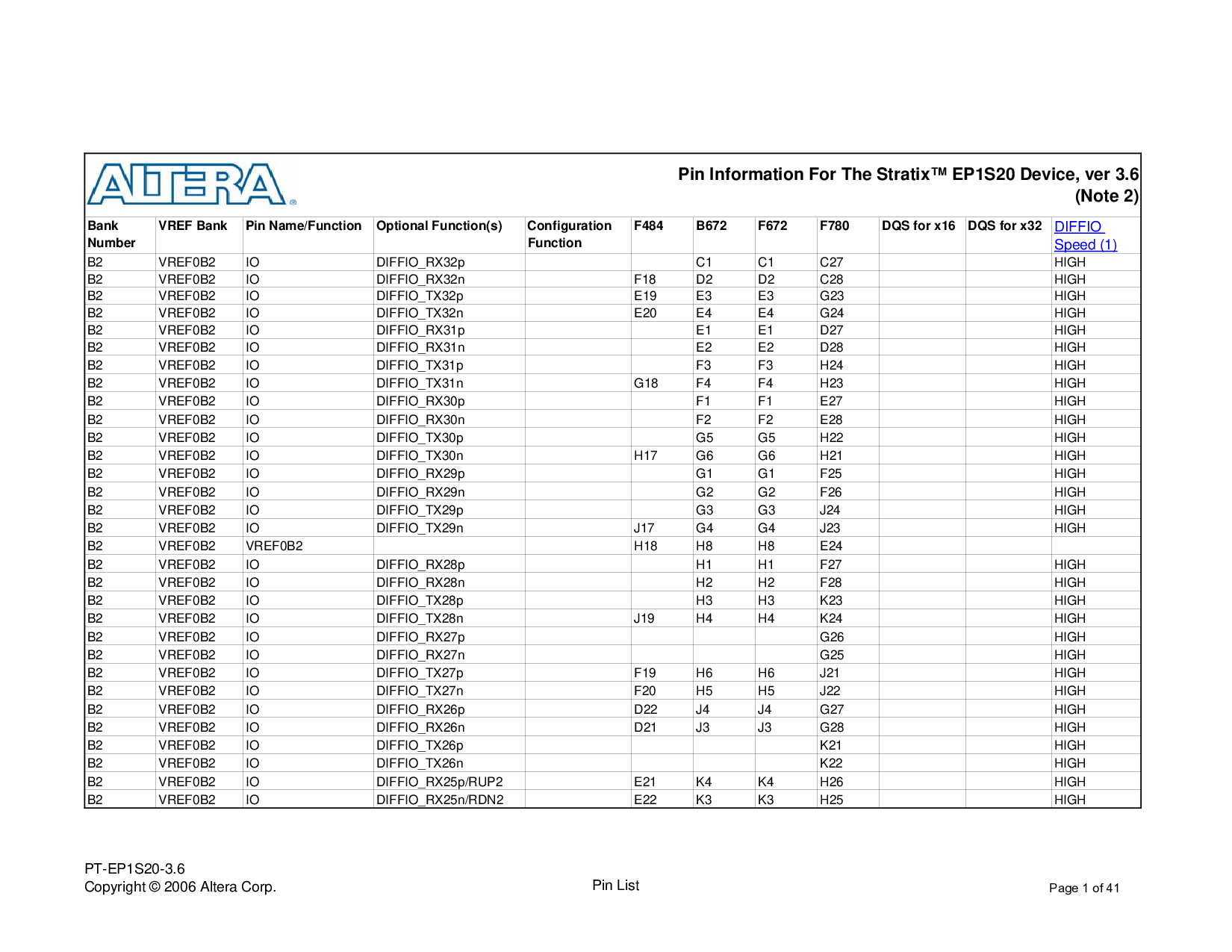

Bank

号码

vref bank 管脚 名字/函数 optional 函数(s) 配置

函数

F484 B672 F672 F780 dqs 为 x16 dqs 为 x32

DIFFIO

速 (1)

B2 VREF0B2 IO diffio_rx32p C1 C1 C27 高

B2 VREF0B2 IO diffio_rx32n F18 D2 D2 C28 高

B2 VREF0B2 IO diffio_tx32p E19 E3 E3 G23 高

B2 VREF0B2 IO diffio_tx32n E20 E4 E4 G24 高

B2 VREF0B2 IO diffio_rx31p E1 E1 D27 高

B2 VREF0B2 IO diffio_rx31n E2 E2 D28 高

B2 VREF0B2 IO diffio_tx31p F3 F3 H24 高

B2 VREF0B2 IO diffio_tx31n G18 F4 F4 H23 高

B2 VREF0B2 IO diffio_rx30p F1 F1 E27 高

B2 VREF0B2 IO diffio_rx30n F2 F2 E28 高

B2 VREF0B2 IO diffio_tx30p G5 G5 H22 高

B2 VREF0B2 IO diffio_tx30n H17 G6 G6 H21 高

B2 VREF0B2 IO diffio_rx29p G1 G1 F25 高

B2 VREF0B2 IO diffio_rx29n G2 G2 F26 高

B2 VREF0B2 IO diffio_tx29p G3 G3 J24 高

B2 VREF0B2 IO diffio_tx29n J17 G4 G4 J23 高

B2 VREF0B2 VREF0B2 H18 H8 H8 E24

B2 VREF0B2 IO diffio_rx28p H1 H1 F27 高

B2 VREF0B2 IO diffio_rx28n H2 H2 F28 高

B2 VREF0B2 IO diffio_tx28p H3 H3 K23 高

B2 VREF0B2 IO diffio_tx28n J19 H4 H4 K24 高

B2 VREF0B2 IO diffio_rx27p G26 高

B2 VREF0B2 IO diffio_rx27n G25 高

B2 VREF0B2 IO diffio_tx27p F19 H6 H6 J21 高

B2 VREF0B2 IO diffio_tx27n F20 H5 H5 J22 高

B2 VREF0B2 IO diffio_rx26p D22 J4 J4 G27 高

B2 VREF0B2 IO diffio_rx26n D21 J3 J3 G28 高

B2 VREF0B2 IO diffio_tx26p K21 高

B2 VREF0B2 IO diffio_tx26n K22 高

B2 VREF0B2 IO diffio_rx25p/rup2 E21 K4 K4 H26 高

B2 VREF0B2 IO diffio_rx25n/rdn2 E22 K3 K3 H25 高

管脚 信息 为 这 stratix™ ep1s20 设备, ver 3.6

(便条 2)

pt-ep1s20-3.6

版权 © 2006 altera corp.

管脚 列表

页 1 的 41