1

特性

•

avr - 高 效能 和 低 电源 risc architecture

•

118 powerful 说明 - 大多数 单独的 时钟 循环 执行

•

8k 字节 的 在-系统 reprogrammable flash

– spi 串行 接口 为 程序 downloading

– 忍耐力: 1,000 写/擦掉 循环

•

512 字节 可擦可编程只读存储器

– 忍耐力: 100,000 写/擦掉 循环

•

512 字节 内部的 sram

•

32 x 8 一般 目的 working 寄存器

•

32 可编程序的 i/o 线条

•

可编程序的 串行 uart

•

spi 串行 接口

•

V

CC

: 2.7 - 6.0v

•

全部地 静态的 运作

– 0 - 8 mhz 4.0 - 6.0v,

– 0 - 4 mhz 2.7 - 4.0v

•

向上 至 8 mips throughput 在 8 mhz

•

一个 8-位 计时器/计数器 和 独立的 预分频器

•

一个 16-位 计时器/计数器 和 独立的 预分频器

和 对比 和 俘获 模式

•

双 pwm

•

外部 和 内部的 中断 来源

•

可编程序的 看门狗 计时器 和 在-碎片 振荡器

•

在-碎片 相似物 比较器

•

低 电源 空闲 和 电源 向下 模式

•

程序编制 锁 为 软件 安全

描述

这 at90s8515 是 一个 低-电源 cmos 8-位 微控制器 为基础 在 这 avr

®

增强 risc architecture. 用 executing powerful 说明 在 一个 单独的 时钟

循环, 这 at90s8515 achieves throughputs approaching 1 mips 每 mhz 准许

这 系统 设计者 至 优化 电源 消耗量 相比 处理 速.

这 avr 核心 结合 一个 rich 操作指南 设置 和 32 一般 目的 working regis-

ters. 所有 这 32 寄存器 是 直接地 连接 至 这 arithmetic 逻辑 单位 (alu),

准许 二 独立 寄存器 至 是 accessed 在 一个 单独的 操作指南 executed

在 一个 时钟 循环. 这 结果 architecture 是 更多 代号 效率高的 当 实现

throughputs 向上 至 ten 时间 faster 比 常规的 cisc 微控制器.

rev. 0841d–06/98

8-位

微控制器

和 8k 字节

在-系统

可编程序的

Flash

AT90S8515

初步的

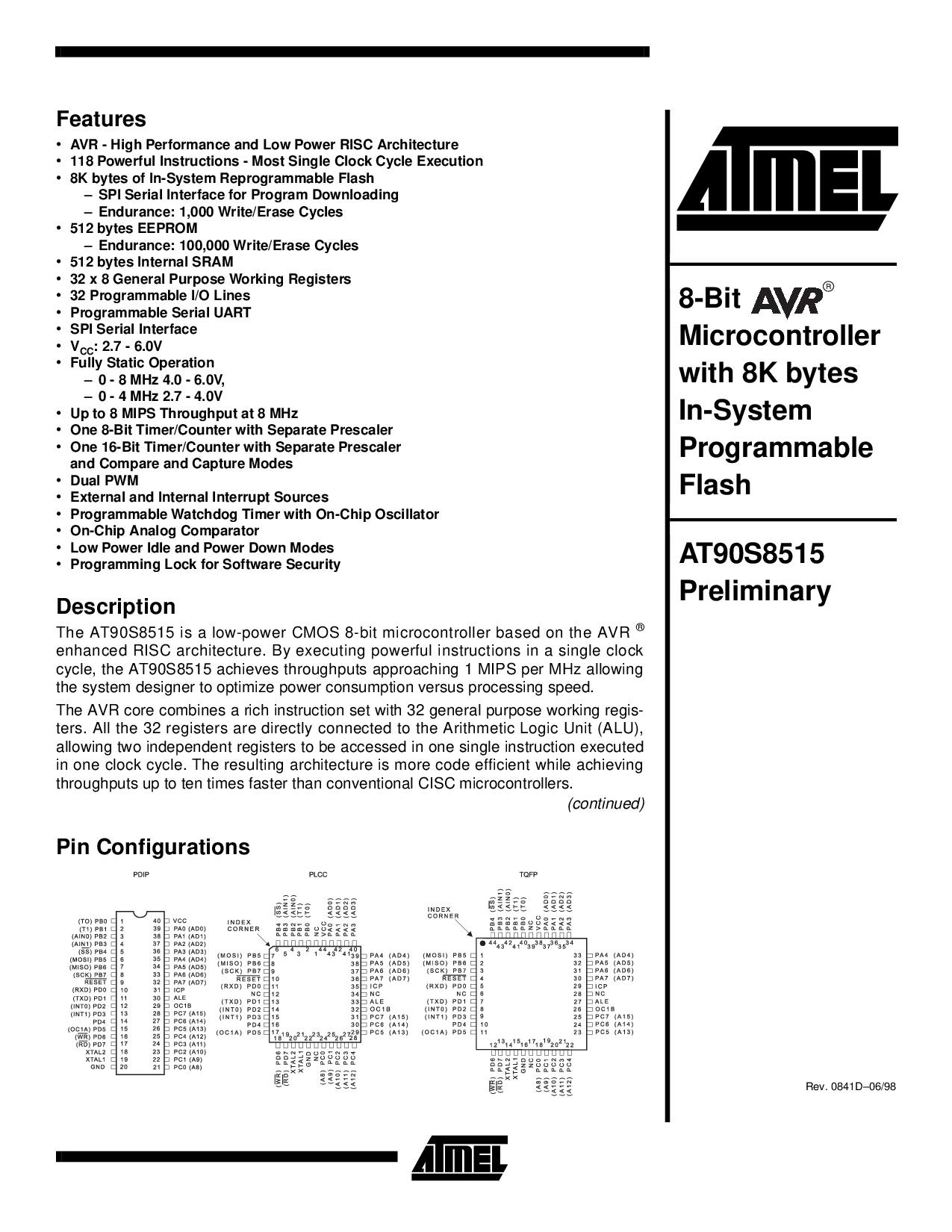

管脚 配置

(持续)