初步

修订 0.3

km681000b 家庭 cmos sram

april 1996

128k x8 有点 低 电源 cmos 静态 ram

这 km681000b 家庭 是 预制 由 samsung's 高级

cmos 流程 技术. 这 家庭 可以 支持 各种

操作 温度 范围 和 有 各种 包装 类型

用于 用户 灵活性 的 系统 设计. 这 家庭 也 支持 低

数据 保留 电压 用于 蓄电池 备份 操作 与 低

数据 保留 电流.

概述 描述特点

¡Ü

流程 技术 : 0.6

§-

CMOS

¡Ü

组织机构 : 128kx8

¡Ü

电源 供应 电压 : 单独 5.0v

¡¾

10%

¡Ü

低 数据 保留 电压 : 2v(最小)

¡Ü

三个 州 输出 和 ttl 兼容

¡Ü

包装 类型 : 电子元件工业联合会 标准

32-倾角, 32-sop, 32-tsop 我 右/f

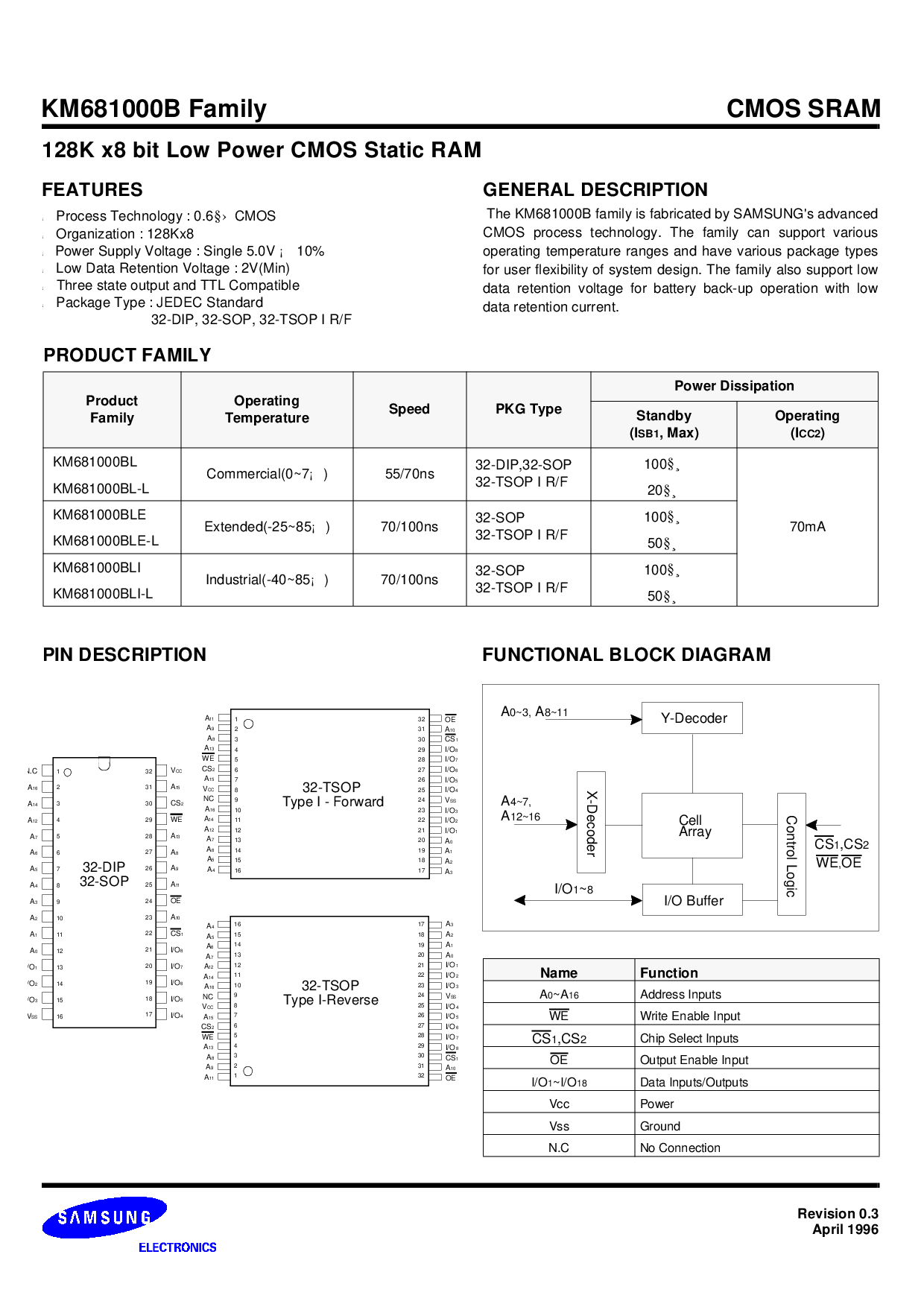

管脚 描述

姓名 功能

一个0~A16 地址 输入

我们 写 启用 输入

cs1,cs2

芯片 选择 输入

oe 输出 启用 输入

我/o1~i/o18 数据 输入/产出

Vcc 电源

vss 接地

n.c 否 连接

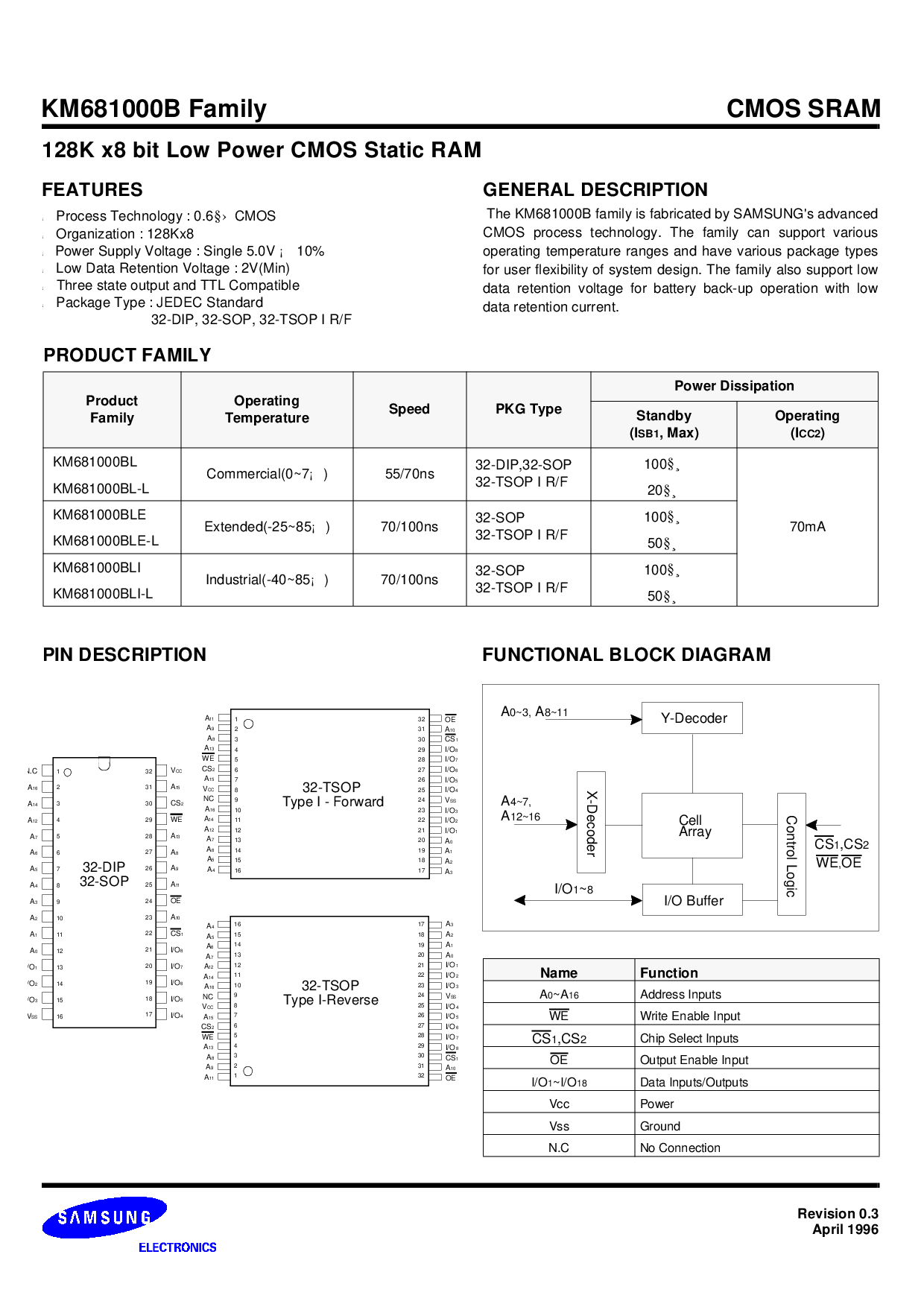

x-解码器

细胞

阵列

产品 家庭

产品

家庭

操作

温度

速度 pkg 类型

电源 耗散

备用

(我SB1, 最大值)

操作

(我CC2)

KM681000BL

商业(0~7

¡É

) 55/70ns

32-倾角,32-sop

32-tsop 我 右/f

100

§Ë

70mA

km681000bl-l

20

§Ë

KM681000BLE

扩展(-25~85

¡É

) 70/100ns

32-sop

32-tsop 我 右/f

100

§Ë

km681000ble-l

50

§Ë

KM681000BLI

工业(-40~85

¡É

) 70/100ns

32-sop

32-tsop 我 右/f

100

§Ë

km681000bli-l

50

§Ë

控制 逻辑

y-解码器

我/o 缓冲区

功能 块 图表

一个0~3,一个8~11

一个4~7,

我/o1~8

32-tsop

类型 我-反向

一个12~16

cs1,cs2

我们,oe

一个11

一个9

一个8

一个13

我们

cs2

一个15

v抄送

nc

一个16

一个14

一个12

一个7

一个6

一个5

一个4

oe

一个10

cs1

我/o8

我/o7

我/o6

我/o5

我/o4

vss

我/o3

我/o2

我/o1

一个0

一个1

一个2

一个3

32-tsop

类型 我 - 前进

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

n.c

一个16

一个14

一个12

一个7

一个6

一个5

一个4

一个3

一个2

一个1

一个0

我/o1

我/o2

我/o3

vss

v抄送

一个15

cs2

我们

一个13

一个8

一个9

一个11

oe

一个10

cs1

我/o8

我/o7

我/o6

我/o5

我/o4

32-倾角

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32-sop

一个11

一个9

一个8

一个13

我们

cs2

一个15

v抄送

nc

一个16

一个14

一个12

一个7

一个6

一个5

一个4

oe

一个10

cs1

我/o8

我/o7

我/o6

我/o5

我/o4

vss

我/o3

我/o2

我/o1

一个0

一个1

一个2

一个3

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16