美国 microsystems, 公司

july 2000

7.11.00

fs6322-05

fs6322-05fs6322-05

fs6322-05

三-pll 时钟 发生器 ic

三-pll 时钟 发生器 icthree-pll 时钟 发生器 ic

三-pll 时钟 发生器 ic

ISO9001

ISO9001ISO9001

ISO9001

1.0 特性

•

三 plls 和 深的 涉及, 反馈, 和 邮递

dividers 至 提供 精确 时钟 发生率

•

多样的 输出 提供 一些 clocking 选项

•

输出 将 是 tristated 为 板 测试

•

s0, s1, 和 s2 输入 modify 输出 发生率 为

设计 flexibility

•

3.3v 运作

•

accepts 5 至 30mhz crystals (看 频率 表格

为 明确的 涉及 发生率 必需的)

•

custom 频率 patterns, pinouts, 和 包装

是 有. 联系 your local ami 销售 repre-

sentative 为 更多 信息.

2.0 描述

这 fs6322 是 一个 只读存储器-为基础 cmos 时钟 发生器 ic

设计 至 降低 费用 和 组件 计数 在 一个 va-

riety 的 电子的 系统.

三 低-jitter 阶段-锁 循环 (plls) 驱动 向上 至 five

低-skew 时钟 输出 至 提供 一个 高 程度 的 flexi-

bility. 这 设备 是 packaged 在 一个 16-管脚 soic 至 迷你-

mize 板 空间.

高-决议 分隔物 能力 准许 一代 的

desired 发生率.

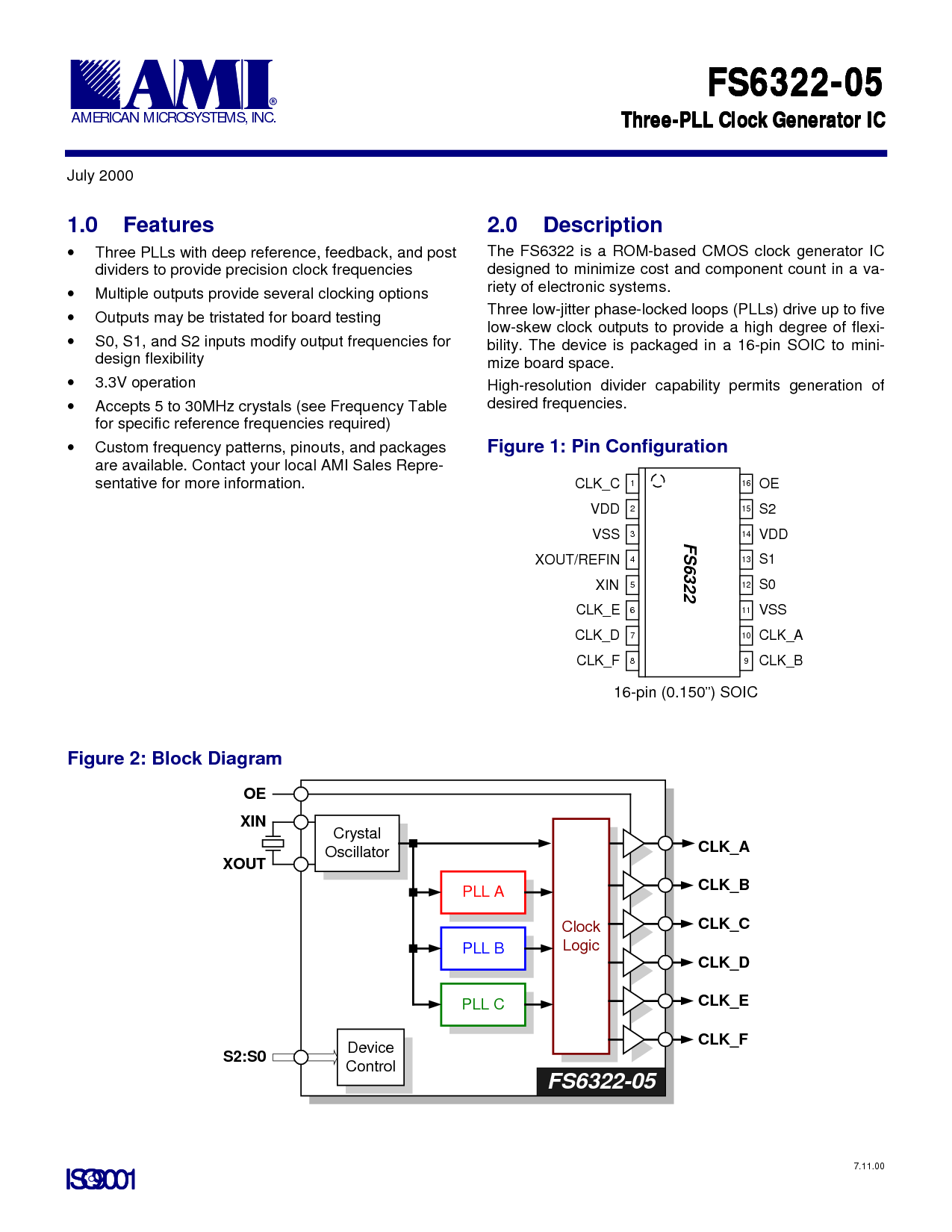

图示 1: 管脚 配置

1 16

2

3

4

5

6

7

8

15

14

13

12

11

10

9

clk_c

VDD

VSS

XIN

xout/refin

clk_e

clk_d

clk_f clk_b

clk_一个

VSS

S0

S1

VDD

S2

OE

FS6322

16-管脚 (0.150”) soic

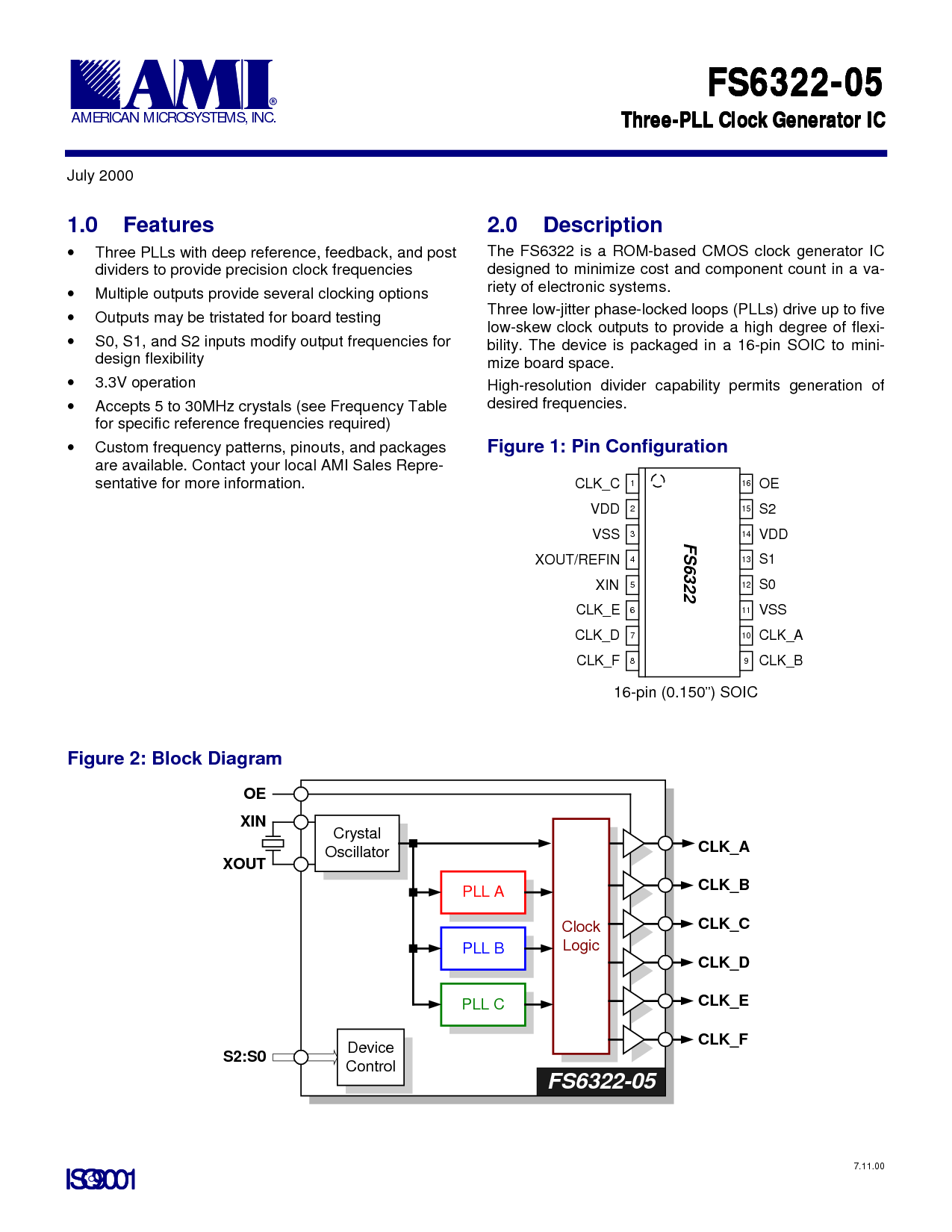

图示 2: 块 图解

fs6322-05

结晶

振荡器

XOUT

XIN

pll 一个

pll b

pll c

时钟

逻辑

clk_e

clk_f

clk_一个

clk_b

clk_c

clk_d

s2:s0

OE

设备

控制