CY2071A

单独的-pll 一般-目的

非易失存储器 可编程序的 时钟 发生器

Cypress 半导体 公司

• 3901 北 第一 街道 • San Jose • ca 95134 • 408-943-2600

文档 #: 38-07139 rev. *a 修订 12月 14, 2002

i

特性 益处

单独的 阶段-锁 循环 architecture

发生 一个 custom 频率 从 一个 外部 源

非易失存储器 programmability

容易 customization 和 快 turnaround

工厂-可编程序的 (cy2071a, cy2071ai) 或者 地方-

可编程序的 (cy2071af, cy2071afi) 设备 选项

程序编制 支持 有 为 所有 opportunities

向上 至 三 configurable 输出

发生 三 related 发生率 从 一个 单独的 设备

低-skew, 低-jitter, 高-精度 输出

满足 核心的 工业 标准 定时 (所需的)东西

内部的 循环 过滤

alleviates 这 需要 为 外部 组件

电源 管理 (oe)

支持 低-电源 产品

频率 选择 选项

3 输出 和 2 用户 可选择的 发生率

configurable 5v 或者 3.3v 运作

支持 工业 标准 设计 platforms

8-管脚 150-mil soic 包装

工业-标准 包装 saves 在 板 空间

选择 手册

部分 号码 输出 输入 频率 范围 输出 频率 范围 Specifics

CY2071A 3

10 mhz

–

25 mhz (外部 结晶)

1 mhz

–

30 mhz (涉及 时钟)

500 khz

–

130 mhz (5v)

500 khz

–

100 mhz (3.3v)

工厂 可编程序的

商业的 温度

CY2071AI 3 10 mhz

–

25 mhz (外部 结晶)

1 mhz

–

30 mhz (涉及 时钟)

500 khz

–

100 mhz (5v)

500 khz

–

80 mhz (3.3v)

工厂 可编程序的

工业的 温度

CY2071AF 3 10 mhz

–

25 mhz (外部 结晶)

1 mhz

–

30 mhz (涉及 时钟)

500 khz

–

100 mhz (5v)

500 khz

–

80 mhz (3.3v)

地方 可编程序的

商业的 温度

CY2071AFI 3 10 mhz

–

25 mhz (外部 结晶)

1 mhz

–

30 mhz (涉及 时钟)

500 khz

–

90 mhz (5v)

500 khz

–

66.6 mhz (3.3v)

地方 可编程序的

工业的 温度

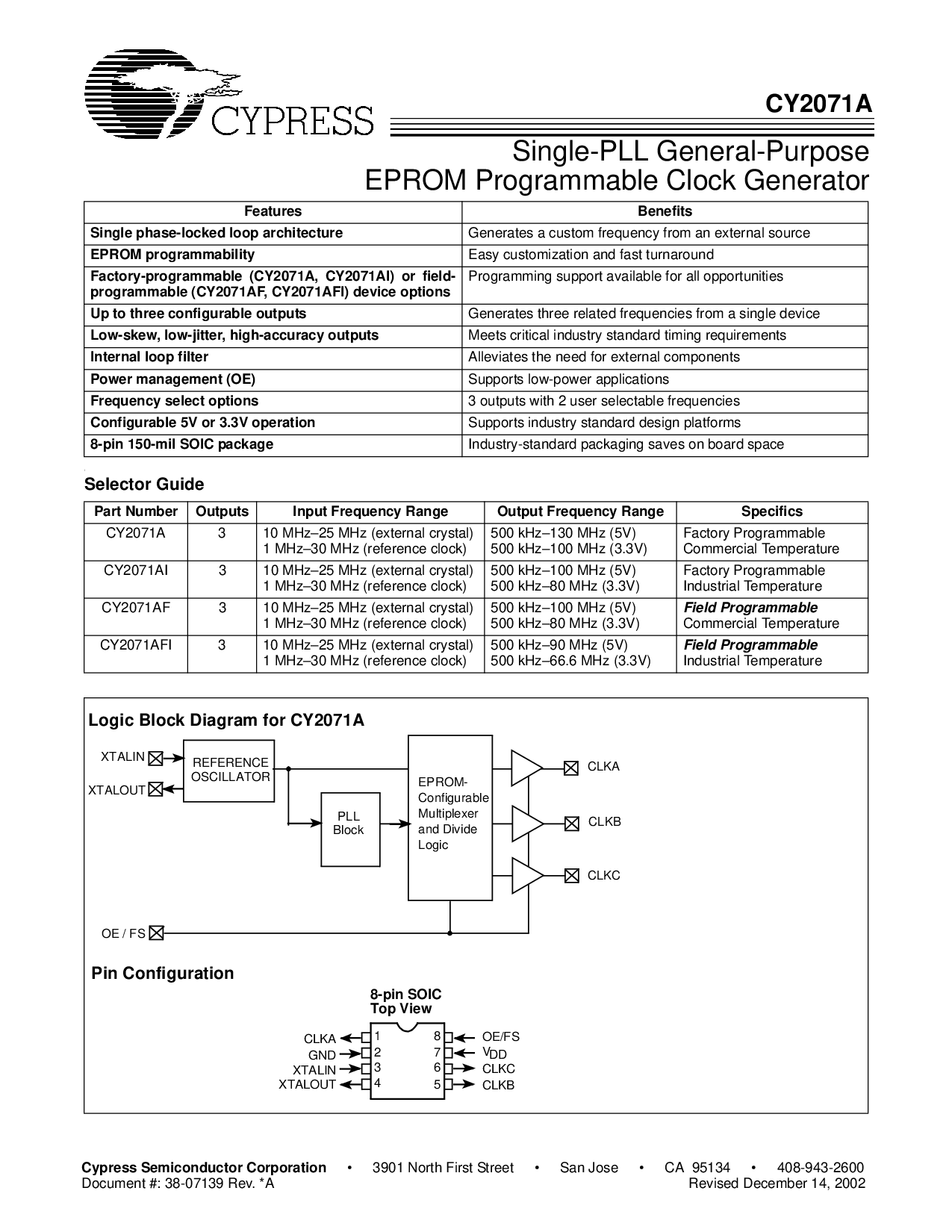

1

2

3

4

5

8

7

6

CLKA

地

XTALIN

XTALOUT

V

DD

oe/fs

CLKC

CLKB

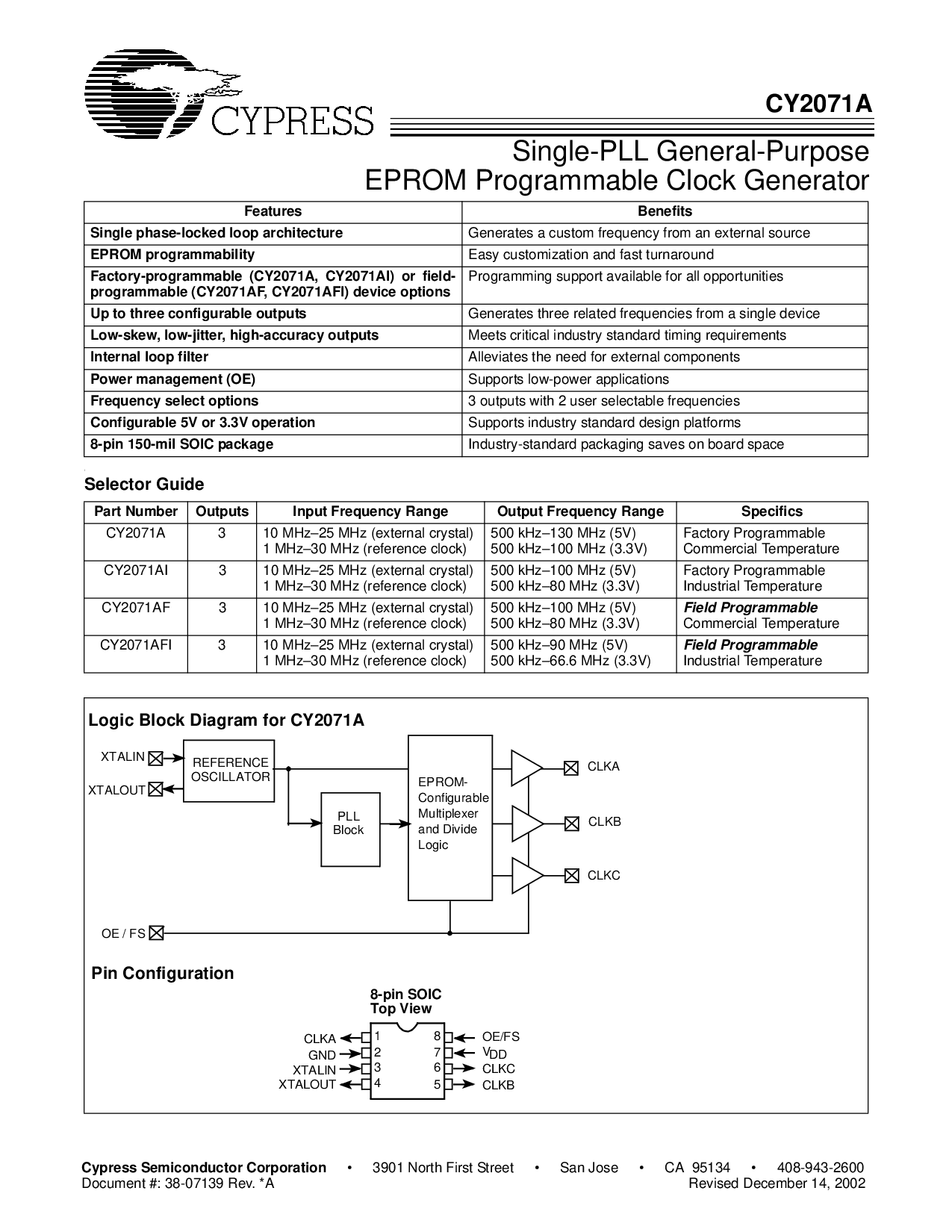

XTALOUT

XTALIN

涉及

振荡器

PLL

块

CLKA

CLKB

CLKC

非易失存储器-

Configurable

多路调制器

和 分隔

逻辑

OE / FS

逻辑 块 图解 为 cy2071a

顶 视图

8-管脚 soic

管脚 配置