3.3v 零 延迟 布菲右

CY2308

柏树 半导体 公司

• 3901 北 第一 街道 • San Jose • ca 95134 • 408-943-2600

文件 #: 38-07146 rev. *c 修订 六月 16, 2004

1CY2308

特点

• 零 输入-输出 传播 延迟, 可调 由

电容式 荷载 开启 fbk 输入

• 多个 配置, 请参见 “available cy2308

configurations” 表

• 多个 低偏斜 产出

— 输出-输出 偏斜 较少 比 200 ps

— 设备-设备 偏斜 较少 比 700 ps

— 两个 银行 的 四 产出, 三个-stateable 由 两个

选择 输入

• 10-mhz 至 133-mhz 操作 范围

• 低 抖动, 较少 比 200 ps 循环-循环 (–1, –1h, –4, –5h)

• 节省空间 16-管脚 150-密耳 soic 包装 或 16-管脚

TSSOP

• 3.3v 操作

• 工业 温度 可用

功能 描述

这 cy2308 是 一个 3.3v 零 延迟 缓冲区 设计 至 分发

高速 时钟 入点 pc, workstat离子, datacom, 电信, 和

其他 高性能 应用程序.

这 零件 有 一个 片上 pll 哪个 锁 至 一个 输入 时钟

已提交 开启 这 参考 管脚. 这 pll 反馈 是 必填项 至 是

驱动 进入 这 fbk 管脚, 和 可以 是 获得 从 一个 的 这

产出. 这 输入-输出 skew 是 保证 至 是 较少

比 350 ps, 和 输出-至-出点put 偏斜 是 保证 至 是

较少 比 200 ps.

这 cy2308 有 两个 银行 的 四 产出 每个, 哪个 可以

是 受控 由 这 选择 输入 作为 显示 入点 这 表 “select

输入 解码.” 如果 全部 输出时钟 是 不 必填项, 银行 b

可以 是 三个-声明. 这 选择 输入 也 允许 这 输入

时钟 至 是 直接 已应用 至 这 输出 用于 芯片 和 系统

测试 目的.

这 cy2308 pll 进入 一个 掉电 州 当 那里 是

否 上升 边缘 开启 这 参考 输入.入点 这个 模式, 全部 产出 是

三态 和 这 pll 是 转弯ed 关, 结果 入点 较少 比

50

µ

一个 的 电流 绘制. 这 pll 关闭 向下 入点 两个 附加

案例 作为 显示 入点 这 “select 输入 decoding” 表.

多个 cy2308 设备 可以 接受 这 相同 输入 时钟 和

分发 它 入点 一个 系统. 入点这个 案例, 这 偏斜 之间 这

产出 的 两个 设备 是 保证 至 是 较少 比 700 ps.

这 cy2308 是 可用 入点 五个 不同的 配置, 作为

显示 入点 这 “available cy2308 configurations” 表 开启 第页

2. 这 cy2308–1 是 这 base 零件, 在哪里 这 输出

频率 相等 这 参考 如果 那里 是 否 计数器 入点 这

反馈 路径. 这 cy2308–1h 是 这 高驱动 版本 的

这 –1, 和 上升 和 坠落 次 开启 这个 设备 是 很多 更快.

这 cy2308–2 允许 这 用户 至 获取 2x 和 1x

频率 开启 每个 输出 银行. 这 精确 配置 和

输出 频率 取决于 开启 哪个 输出 驱动器 这

反馈 管脚. 这 cy2308–3 允许这 用户 至 获取 4x 和

2x 频率 开启 这 产出.

这 cy2308–4 启用 这 用户 至 获取 2x 时钟 开启 全部

产出. 因此, 这 零件 是 极其 多才多艺, 和 可以 是 已使用

入点 一个 品种 的 应用程序.

这 cy2308–5h 是 一个 高驱动 版本 与 参考/2 开启 两者都有

银行.

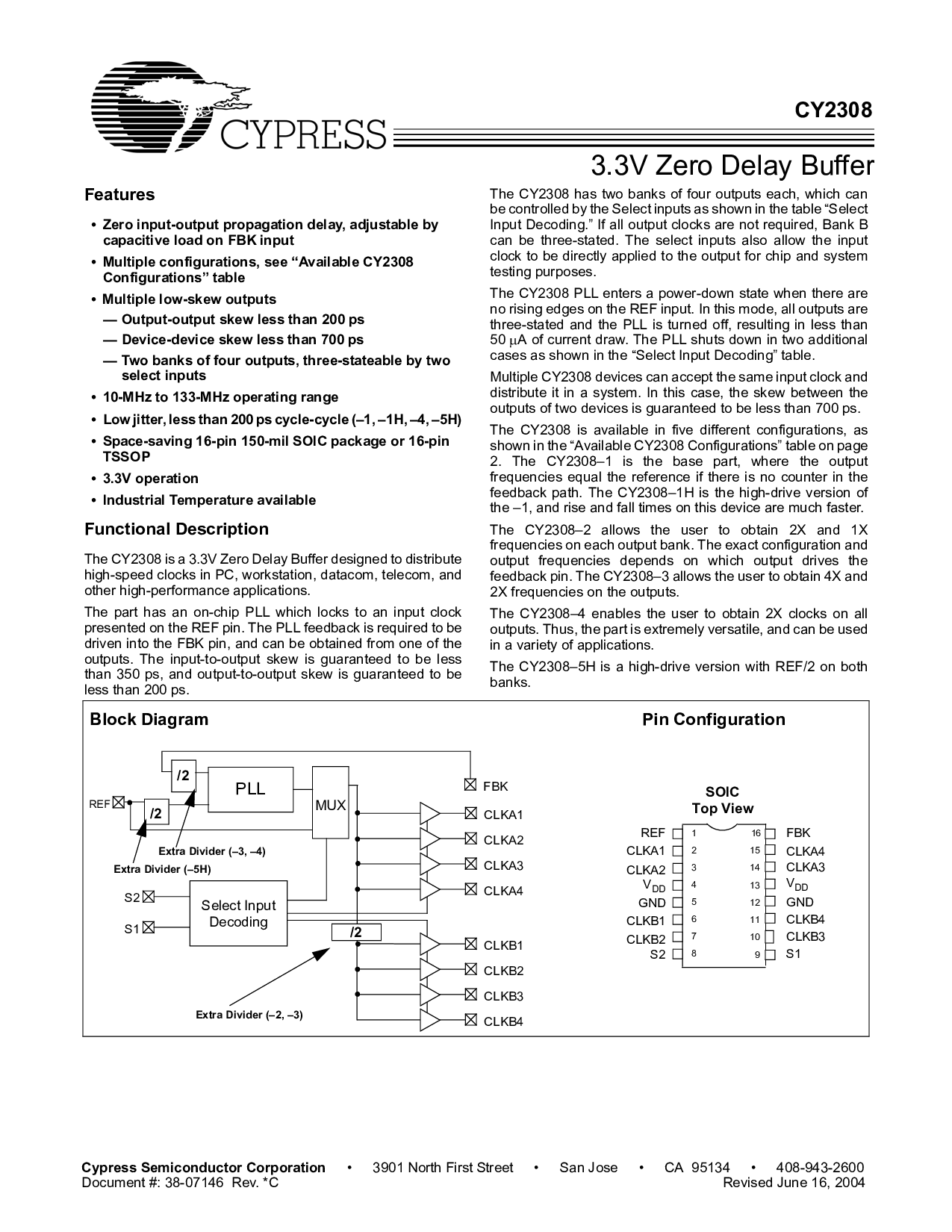

9

16

FBK

CLKA4

CLKA3

v

dd

地

CLKB4

CLKB3

S1

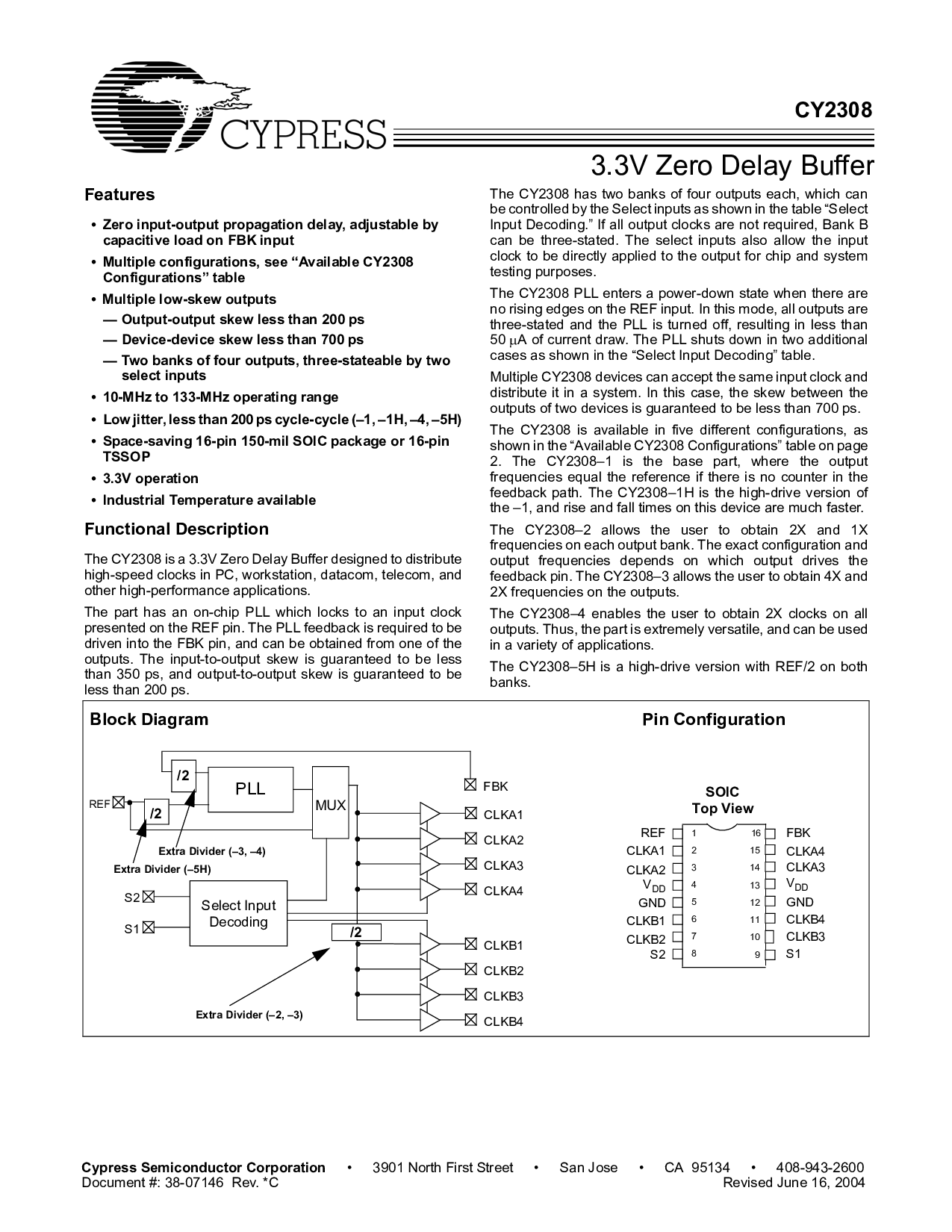

块 图表

1

2

3

4

5

6

7

8

10

11

12

13

14

15

参考

CLKA1

CLKA2

v

dd

地

CLKB1

CLKB2

S2

SOIC

顶部 查看

管脚 配置

参考

CLKA1

CLKA2

CLKA3

CLKA4

FBK

PLL

mux

选择 输入

解码

S2

S1

CLKB1

CLKB2

CLKB3

CLKB4

/2

额外的 分隔器 (–2, –3)

/2

额外的 分隔器 (–3, –4)

额外的 分隔器 (–5h)

/2