ds90cr281/ds90cr282

28-位 频道 Link

一般 描述

这 DS90CR281 传输者 converts 28 位 的 cmos/ttl

数据 在 四 LVDS (低 电压 差别的 signaling) 数据

streams. 一个 阶段-锁 transmit 时钟 是 transmitted 在 par-

allel 和 这 数据 streams 在 一个 fifth LVDS link. 每 循环

的 这 transmit 时钟 28 位 的 输入 数据 是 抽样 和

transmitted. 这 DS90CR282 接受者 converts 这 LVDS

数据 streams 后面的 在 28 位 的 cmos/ttl 数据. 在 一个 trans-

mit 时钟 频率 的 40 mhz, 28 位 的 TTL 数据 是 trans-

mitted 在 一个 比率 的 280 Mbps 每 LVDS 数据 频道. 使用

一个 40 MHz 时钟, 这 数据 throughput 是 1.12 gbit/s

(140 mbytes/s).

这 multiplexing 的 这 数据 线条 提供 一个 substantial

缆索 减少. 长 距离 并行的 单独的-结束 buses

典型地 需要 一个 地面 线 每 起作用的 信号 (和 有

非常 限制 噪音 拒绝 能力). 因此, 为 一个 28-位 宽

数据 总线 和 一个 时钟, 向上 至 58 conductors 是 必需的.

和 这 频道 Link chipset 作 few 作 11 conductors (4

数据 pairs, 1 时钟 一双 和 一个 最小 的 一个

地面) 是 需要. 这个 提供 一个 80

%

减少 在 re-

quired 缆索 宽度, 这个 提供 一个 系统 费用 savings,

减少 连接器 物理的 大小 和 费用, 和 减少

防护 (所需的)东西 预定的 至 这 cables’ 小 表格 fac-

tor.

这 28 cmos/ttl 输入 能 支持 一个 多样性 的 信号

结合体. 为 例子, 7 4-位 nibbles 或者 3 9-位 (字节 +

parity) 和 1 控制.

特性

n

Narrow 总线 减少 缆索 大小 和 费用

n

±

1V 一般 模式 范围 (地面 shifting)

n

290 mV 摆动 LVDS 数据 传递

n

1.12 gbit/s 数据 throughput

n

低 摆动 差别的 电流 模式 驱动器 减少 EMI

n

Rising 边缘 数据 strobe

n

电源 向下 模式

n

Offered 在 低 profile 56-含铅的 TSSOP 包装

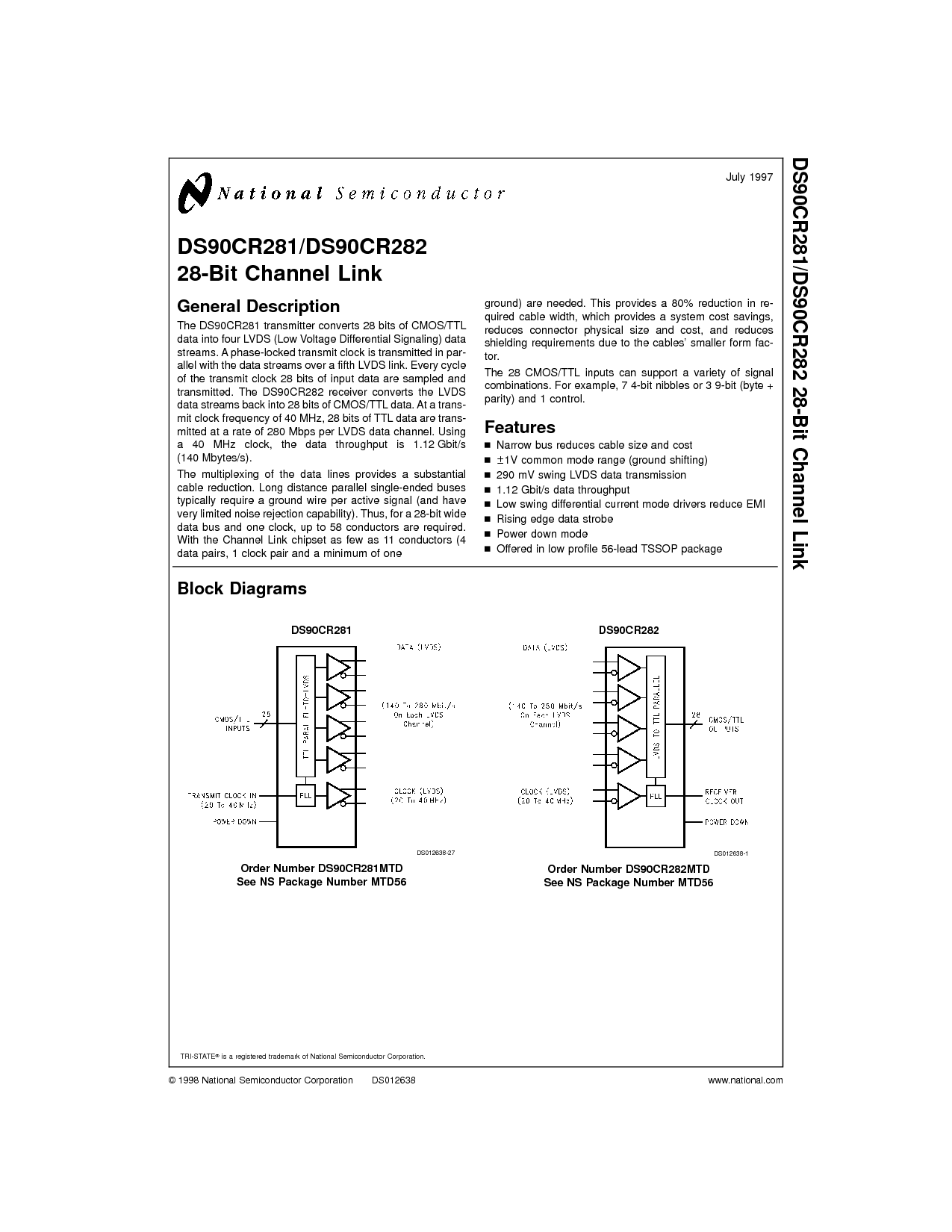

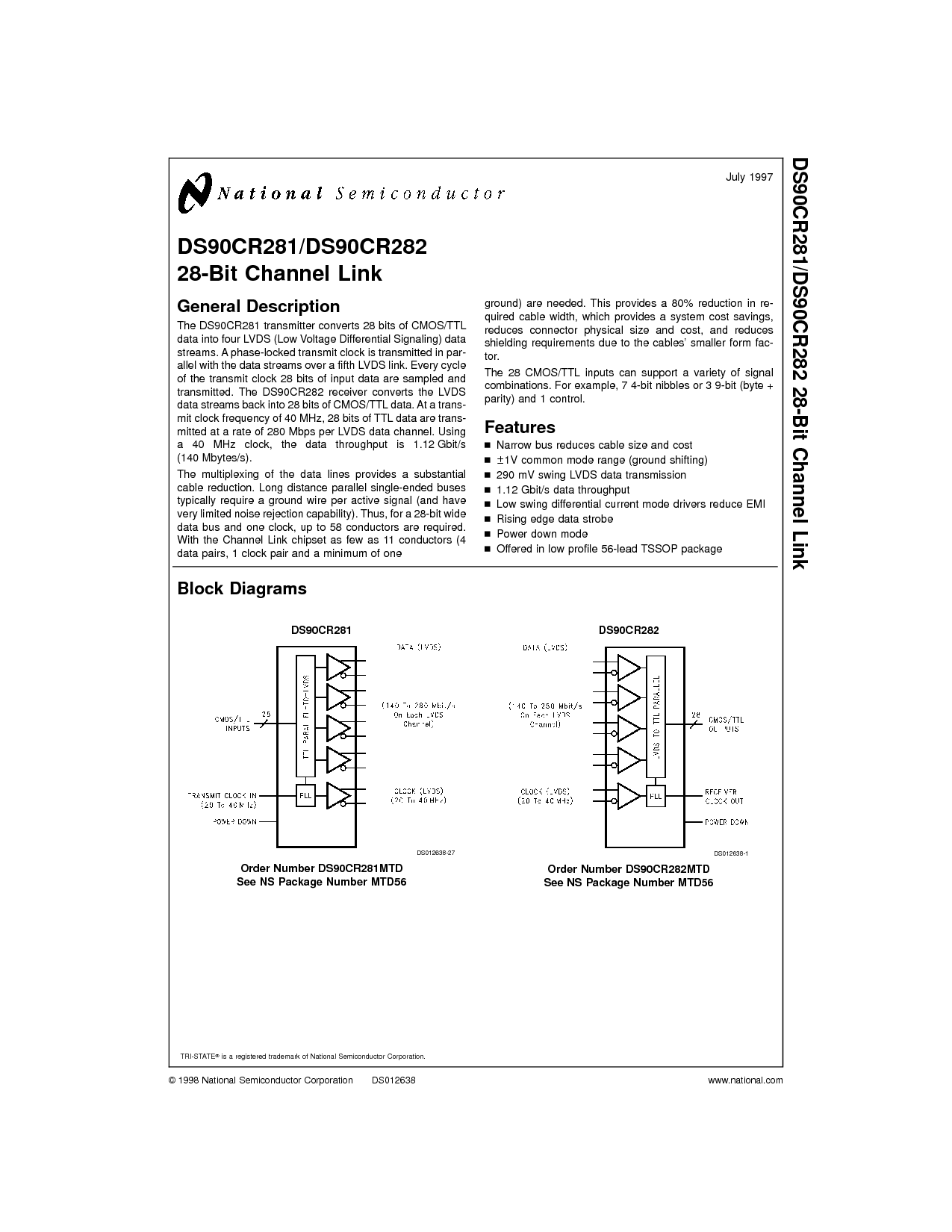

块 图解

触发-状态

®

是 一个 注册 商标 的 国家的 半导体 公司.

DS90CR281

ds012638-27

顺序 号码 DS90CR281MTD

看 NS 包装 号码 MTD56

DS90CR282

ds012638-1

顺序 号码 DS90CR282MTD

看 NS 包装 号码 MTD56

July 1997

ds90cr281/ds90cr282 28-位 频道 Link

© 1998 国家的 半导体 公司 DS012638 www.国家的.com