100331

低 电源 Triple D flip-flop

一般 描述

这 100331 包含 三 d-类型, 边缘-triggered 主控/

从动装置 flip-flops 和 真实 和 complement 输出, 一个 com-

mon 时钟 (cp

C

), 和 主控 设置 (ms) 和 主控 重置

(mr) 输入. 各自 flip-flop 有 单独的 时钟 (cp

n

), 直接

设置 (sd

n

) 和 直接 Clear (cd

n

) 输入. 数据 enters 一个 mas-

ter 当 两个都 CP

n

和 CP

C

是 低 和 transfers 至 一个

从动装置 当 CP

n

或者 CP

C

(或者 两个都) go 高. 这 主控 设置,

主控 重置 和 单独的 CD

n

和 SD

n

输入 override

这 时钟 输入. 所有 输入 有 50 k

Ω

拉-向下 电阻器.

特性

n

35

%

电源 减少 的 这 100131

n

2000V 静电释放 保护

n

管脚/函数 兼容 和 100131

n

电压 补偿 运行 范围

=

−4.2v 至 −5.7v

n

有 至 工业的 等级 温度 范围

n

有 至 标准 微型电路 绘画 (smd)

5962-9153601

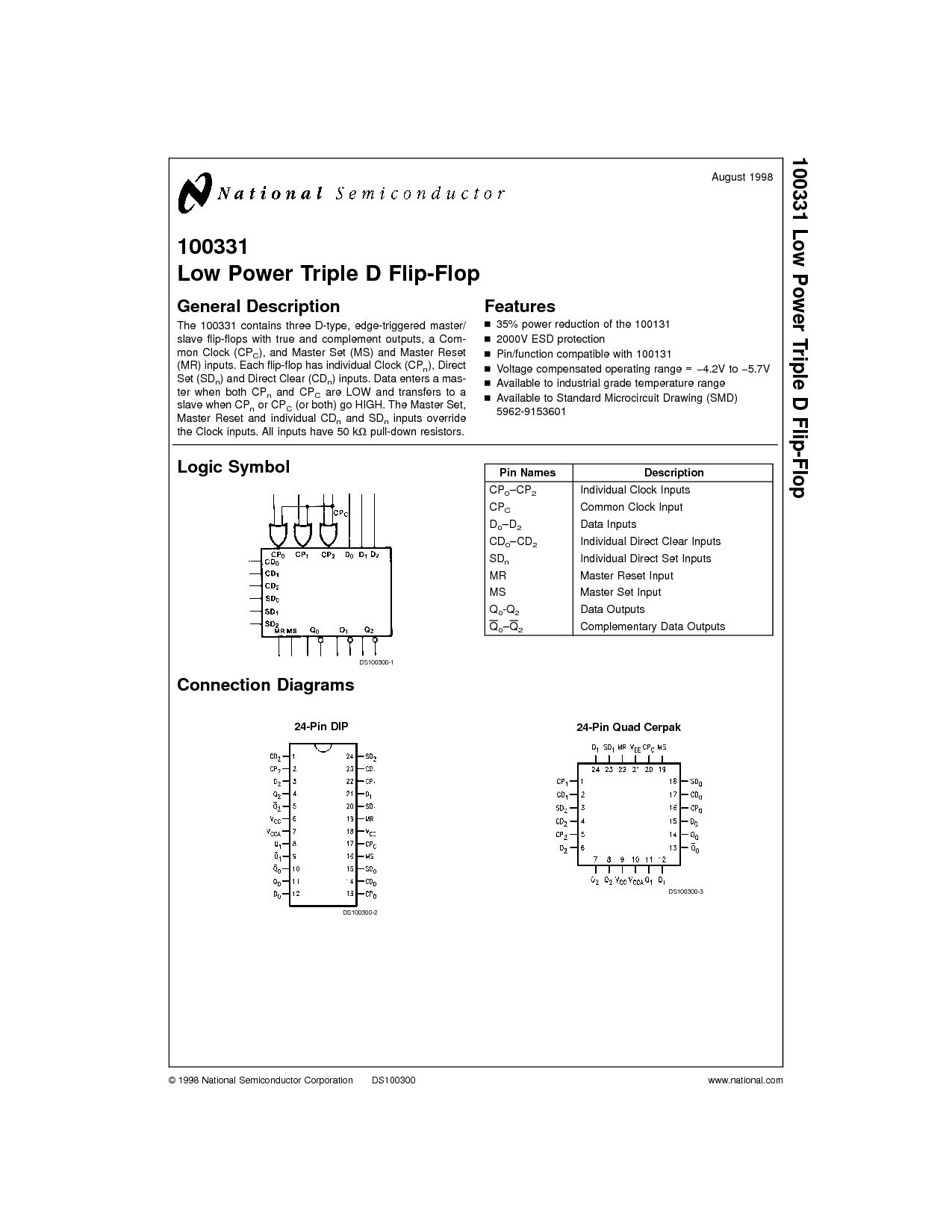

逻辑 标识

管脚 Names 描述

CP

0

–CP

2

单独的 时钟 输入

CP

C

一般 时钟 输入

D

0

–D

2

数据 输入

CD

0

–CD

2

单独的 直接 Clear 输入

SD

n

单独的 直接 设置 输入

MR 主控 重置 输入

MS 主控 设置 输入

Q

0

-q

2

数据 输出

Q

0

–Q

2

Complementary 数据 输出

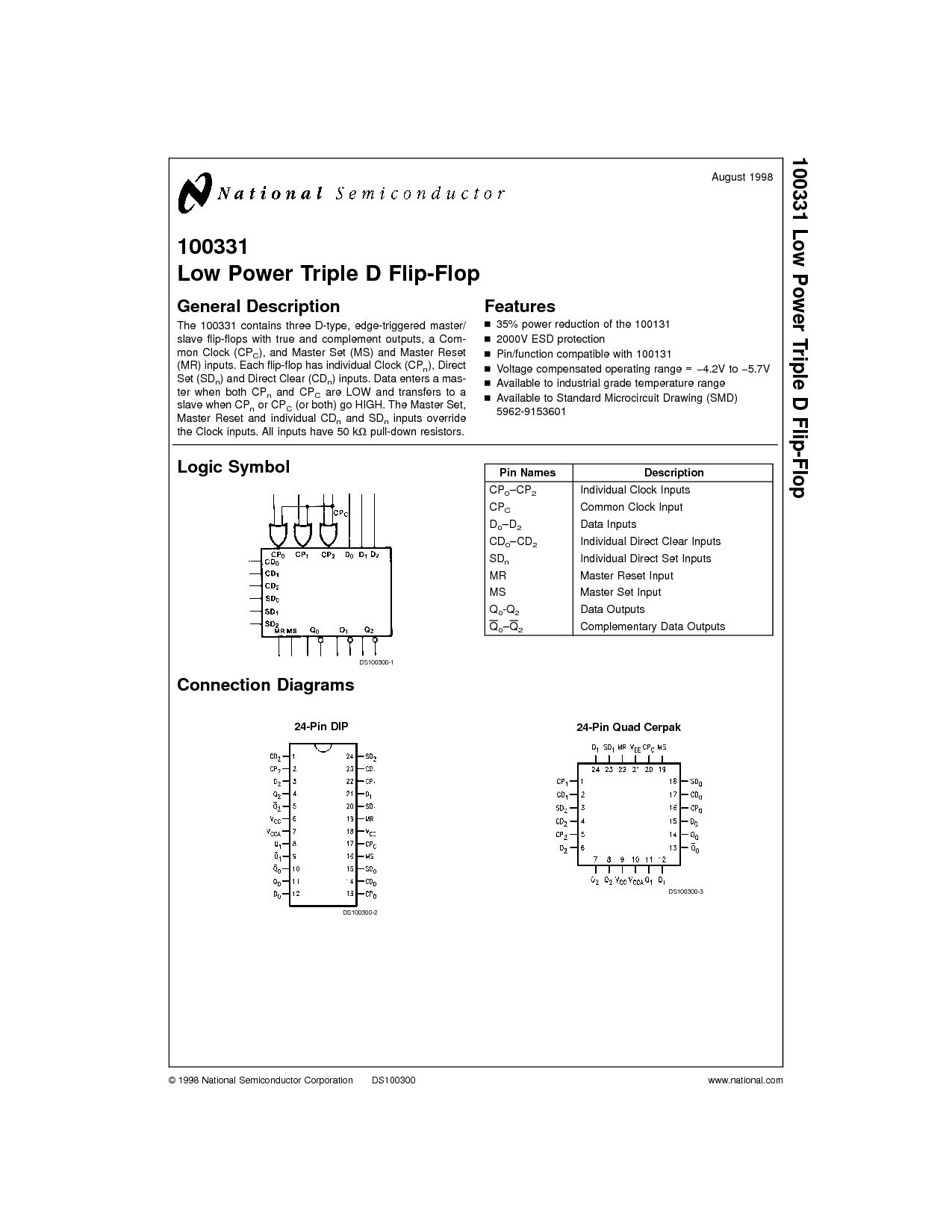

连接 图解

ds100300-1

24-管脚 插件

ds100300-2

24-管脚 四方形 Cerpak

ds100300-3

8月 1998

100331 低 电源 Triple D flip-flop

© 1998 国家的 半导体 公司 DS100300 www.国家的.com