®

altera 公司 1

flex 8000

可编程序的 逻辑

设备 家族

九月 1998, ver. 9.11 数据 薄板

一个-ds-f8000-09.11

flex 8000

3

特性...

■

低-费用, 高-密度, 寄存器-rich cmos 可编程序的 逻辑

设备 (pld) 家族 (看表格 1)

– 2,500 至 16,000 usable 门

– 282 至 1,500 寄存器

■

系统-水平的 特性

– 在-电路 reconfigurability (icr) 通过 外部 配置

非易失存储器 或者 intelligent 控制

– 全部地 一致的 和 这 附带的 组件 interconnect

(pci) 标准

– 建造-在 joint-测试 action 组 (jtag) boundary-scan 测试 (bst)

电路系统 一致的 和 ieee 标准. 1149.1-1990 在 选择 设备

– MultiVolt

™

i/o 接口 enabling 设备 核心 至 run 在 5.0 v,

当 i/o 管脚 是 兼容 和 5.0-v 和 3.3-v 逻辑 水平

– 低 电源 消耗量 (典型 规格 较少 比 0.5 毫安

在 备用物品 模式)

■

有伸缩性的 interconnect

– FastTrack

™

interconnect 持续的 routing 结构 为 快,

predictable interconnect 延迟

– 专心致志的 carry chain 那 实现 arithmetic 功能 此类

作 快 adders, counters, 和 comparators (automatically 使用 用

软件 tools 和 megafunctions)

– 专心致志的 cascade chain 那 实现 高-速, 高-风扇-在

逻辑 功能 (automatically 使用 用 软件 tools 和

megafunctions)

– 触发-状态 emulation 那 实现 内部的 触发-状态 nets

■

powerful i/o 管脚

– 可编程序的 输出 回转-比率 控制 减少 切换 噪音

■

附带的 寄存器 为 快 建制 和 时钟-至-输出 延迟

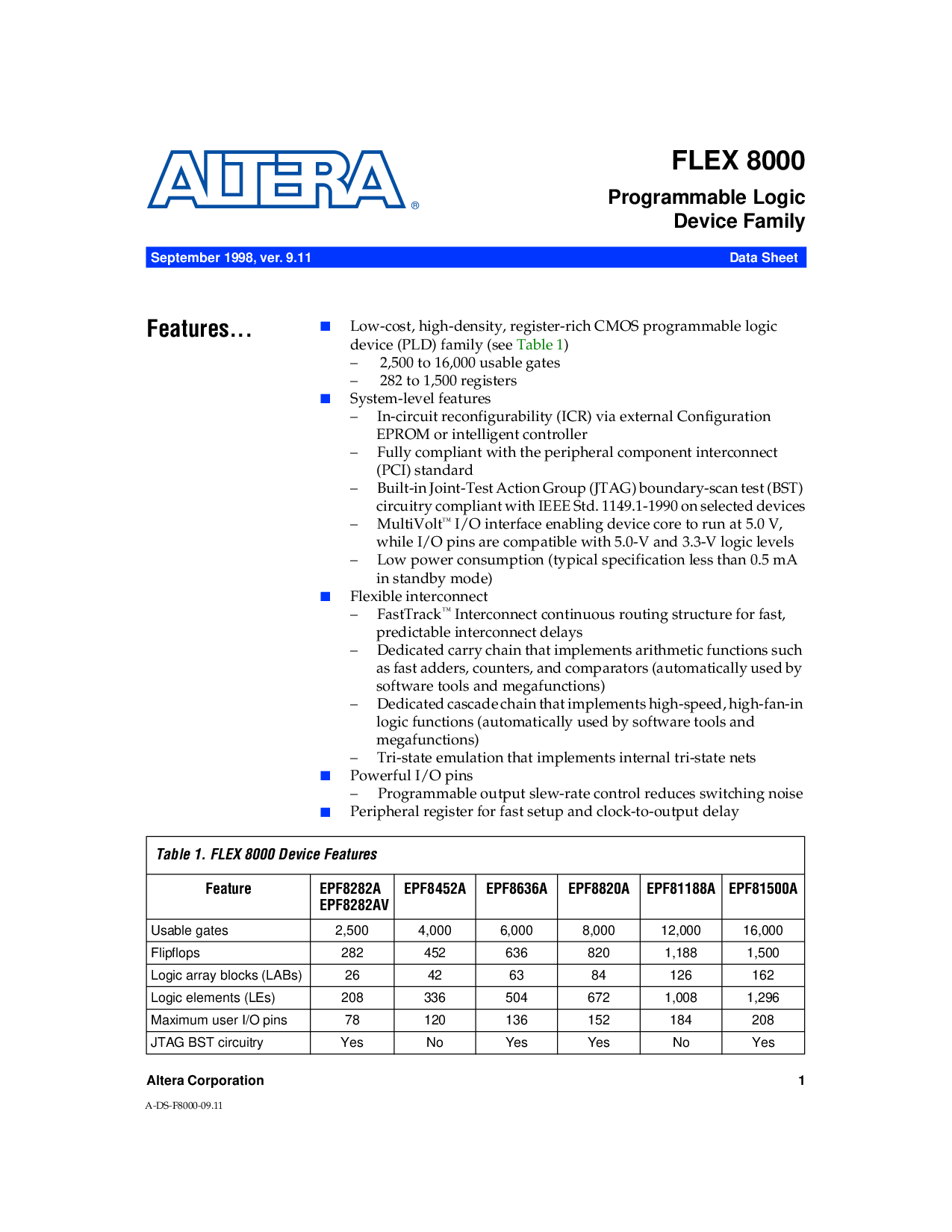

表格 1. flex 8000 设备 特性

特性 EPF8282A

EPF8282AV

EPF8452A EPF8636A EPF8820A EPF81188A EPF81500A

usable 门 2,500 4,000 6,000 8,000 12,000 16,000

Flipflops 282 452 636 820 1,188 1,500

逻辑 排列 blocks (labs) 26 42 63 84 126 162

逻辑 elements (les) 208 336 504 672 1,008 1,296

最大 用户 i/o 管脚 78 120 136 152 184 208

jtag bst 电路系统 Yes 非 Yes Yes 非 Yes