HY57V653220B

4 banks x 512k x 32bit 同步的 dram

这个 文档 是 一个 一般 产品 descripti在 和 是 主题 至 改变 没有 注意.hynix 半导体 做 不 假设 任何

责任 为 使用 的 电路 描述. 非 专利权 许可 是 暗指.

rev.1.6/dec. 011

描述

这 hynix hy57v653220b 是 一个 67,108,864-位 cmos 同步的 dram, ideally suited 为 这 记忆 产品

这个 需要 宽 数据 i/o 和 高 带宽. hy57v653220b 是 有组织的 作 4banks 的 524,288x32.

hy57v653220b 是 offering 全部地 同步的 运作 关联 至 一个 积极的 边缘 的 这 时钟. 所有 输入 和 输出-

puts 是 同步 和 这 rising 边缘 的 这 时钟 输入. 这 数据 paths 是 内部 pipelined 至 达到 非常

高 带宽. 所有 输入 和 输出 电压 水平 是 兼容 和 lvttl.

可编程序的 选项 包含 这 长度 的 pipeline (读 latency 的 2 或者 3), 这 号码 的 consecutive 读 或者 写

循环 initiated 用 一个 单独的 控制 command (burst 长度 的 1,2,4,8 或者 全部 页), 和 这 burst 计数

sequence(sequential 或者 interleave). 一个 burst 的 读 或者 写 循环 在 progress 能 是 terminated 用 一个 burst terminate

command 或者 能 是 interrupted 和 replaced 用 一个 新 burst 读 或者 写 command 在 任何 循环. (这个 pipelined

设计 是 不 restricted 用 一个 `2n` rule.)

特性

• 电子元件工业联合会 标准 3.3v 电源 供应

• 所有 设备 管脚 是 兼容 和 lvttl 接口

• 电子元件工业联合会 标准 400mil 86pin tsop-ii 和 0.5mm 的

管脚 程度

• 所有 输入 和 输出 关联 至 积极的 边缘 的

系统 时钟

• 数据 掩饰 函数 用 dqm0,1,2 和 3

• 内部的 四 banks 运作

• 自动 refresh 和 自 refresh

• 4096 refresh 循环 / 64ms

• 可编程序的 burst 长度 和 burst 类型

- 1, 2, 4, 8 或者 全部 页 为 sequential burst

- 1, 2, 4 或者 8 为 interleave burst

• 可编程序的 cas

latency ; 2, 3 clocks

• burst 读 单独的 写 运作

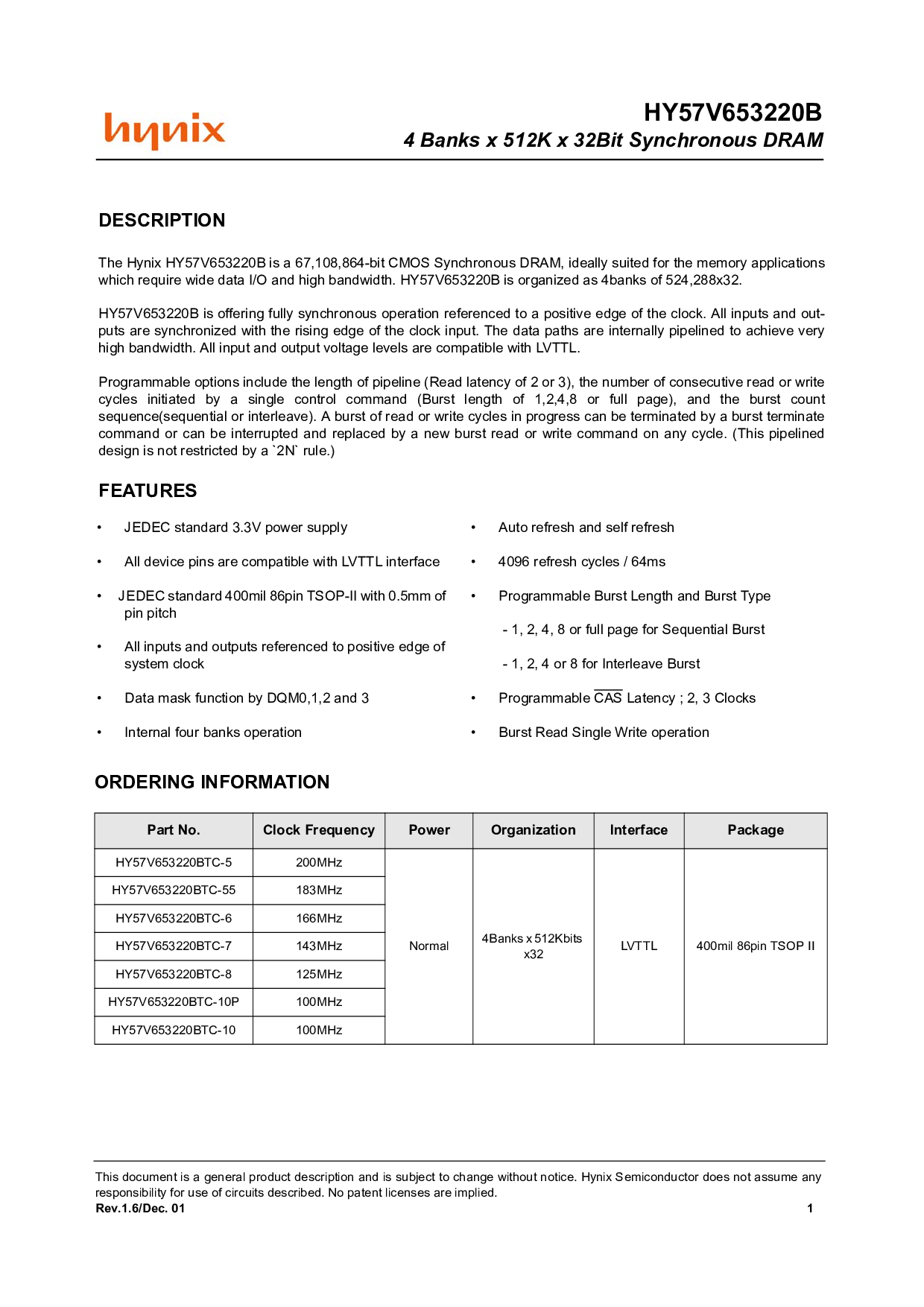

订货 信息

部分 非. 时钟 频率 电源 Organization 接口 包装

hy57v653220btc-5 200MHz

正常的

4banks x 512kbits

x32

LVTTL 400mil 86pin tsop ii

hy57v653220btc-55 183MHz

hy57v653220btc-6 166MHz

hy57v653220btc-7 143MHz

hy57v653220btc-8 125MHz

hy57v653220btc-10p 100MHz

hy57v653220btc-10 100MHz