1

特点

•

串行 外围设备 接口 (spi) 兼容

•

支架 spi 模式 0 (0,0) 和 3 (1,1)

•

20 mhz 时钟 费率

•

字节 模式 和 256-字节 第页 模式 用于 程序 运营

•

部门 体系结构:

– 两个 扇区 与 32k 字节数 每个 (512k)

– 四 扇区 与 32k 字节数 每个 (1m)

– 128 页数 按 部门

•

产品 标识 模式

•

低电压 操作

– 2.7 (v

抄送

= 2.7v 至 3.6v)

•

部门 写 保护

•

写 保护 (wp) 管脚 和 写 禁用 说明 用于

两者都有 硬件 和 软件 数据 保护

•

自定时 程序 循环 (60 µs/字节 典型)

•

自定时 部门 擦除 循环 (1 第二/部门 典型)

•

单独 循环 重新编程 (擦除 和 程序) 用于 状态 注册

•

高 可靠性

– 耐力: 10,000 写 循环次数 典型

•

8-铅 电子元件工业联合会 soic

描述

这 at25f512/1024 提供 524,288/1,048,576 比特 的 串行 可重新编程 闪光灯

记忆 有组织的 作为 65,536/131,072 字词 的 8 比特 每个. 这 设备 是 优化

用于 使用 入点 许多 工业 和 商业 应用程序 在哪里 低功耗 和 低-电压-

年龄 操作 是 必不可少的. 这 at25f512/1024 是 可用 入点 一个 节省空间 8-铅

电子元件工业联合会 soic 包装.

这 at25f512/1024 是 已启用 通过 这 芯片 选择 管脚 (cs

) 和 已访问 通过 一个

3-电线 接口 由 的 串行 数据 输入 (si), 串行 数据 输出 (所以), 和

串行 时钟 (sck). 全部 写 循环次数 是 完全 自我-定时.

块 写 保护 用于 顶部 1/4, 顶部 1/2 或 这 整个 记忆 阵列 (1m) 或

整个 记忆 阵列 (512k) 是 已启用 由 编程 这 状态 注册. 分开

写 启用 和 写 禁用 说明 是 提供 用于 附加 数据 保护.

硬件 数据 保护 是 提供 通过 这 wp

管脚 至 保护 反对 无意

写 尝试次数 至 这 状态 注册. 这 保持

管脚 将 是 已使用 至 挂起 任何 串行

通信 无 重置 这 串行 顺序.

右e?v.1440M–se?e?p右–7/03

spi 串行

记忆

512k (65,536 x 8)

1m (131,072 x 8)

在25f512

AT25F1024

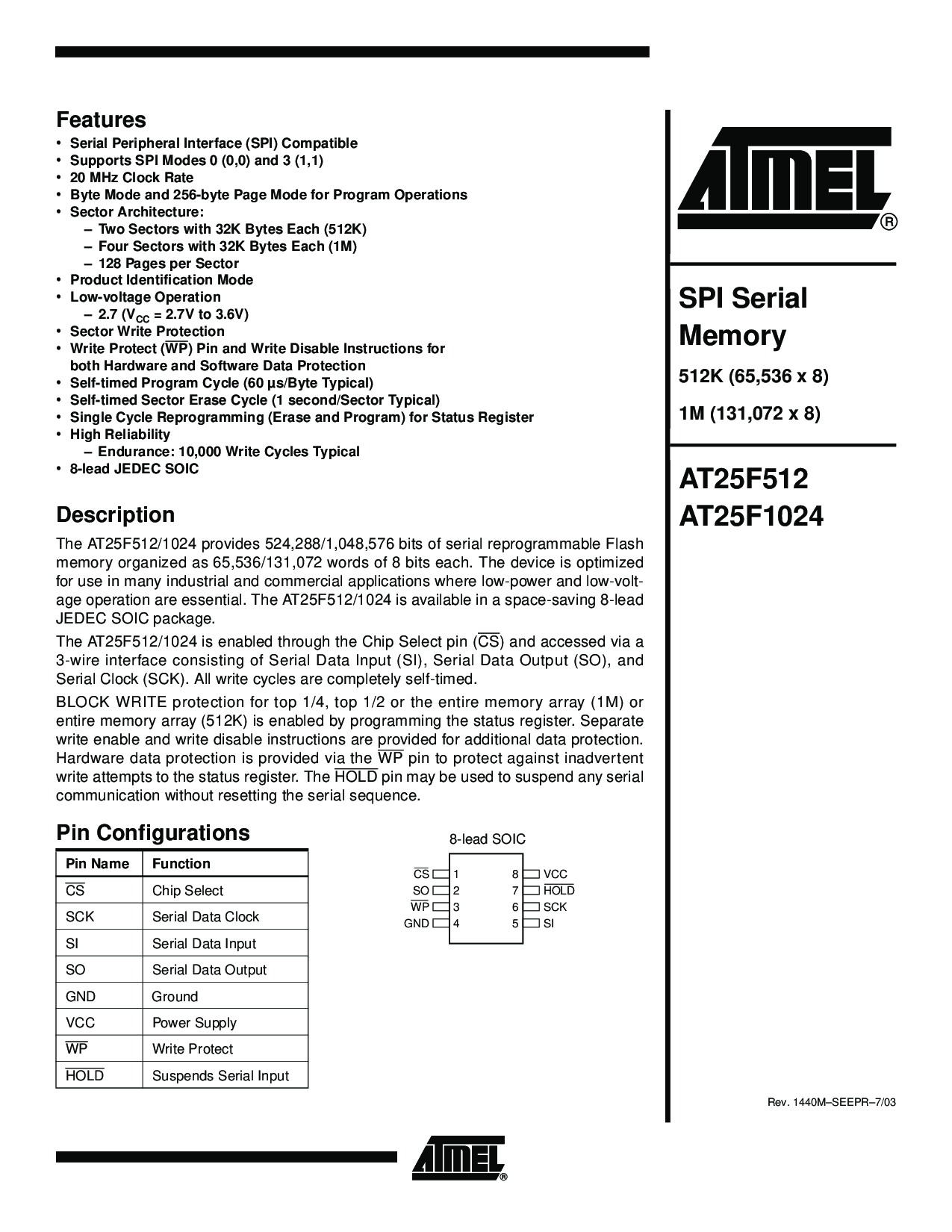

管脚 配置

管脚 姓名 功能

cs

芯片 选择

sck 串行 数据 时钟

si 串行 数据 输入

所以 串行 数据 输出

地 接地

VCC 电源 供应

WP

写 保护

保持

暂停 串行 输入

8-铅 soic

1

2

3

4

8

7

6

5

cs

所以

WP

地

VCC

保持

sck

si