1/35

初步的 数据

九月 2002

这个 是 初步的 信息 在 一个 新 产品 now 在 开发 或者 undergoing evaluation. 详细信息 是 主题 至 改变 没有 注意.

M50LPW012

2 mbit (256kb x8, 激励 块)

3v 供应 低 管脚 计数 flash 记忆

■

供应 电压

–V

CC

= 3v 至 3.6v 为 程序, 擦掉 和

读 行动

–V

PP

= 12v 为 快 程序 和 快 擦掉

■

低 管脚 计数 (lpc)

– 标准 接口 为 embedded 运作

和 pc chipsets 那 是 没有 automap-

ping 记忆 特性

■

地址/地址 多路复用 (一个/一个

mux)

– 接口 为 程序编制 设备 com-

patibility

■

低 管脚 计数 (lpc) 硬件

接口 模式

– 5 信号 交流 接口 支承的

读 和 写 行动

– 硬件 写 保护 管脚 为 块 pro-

tection

– 寄存器 为基础 读 和 写 保护

– 5 额外的 一般 目的 输入 为 plat-

表格 设计 flexibility

– 同步 和 33mhz pci 时钟

■

字节 程序编制 时间

– 单独的 字节 模式 10µs 典型

– quadruple 字节 模式 2.5

µ

s 典型

■

7 记忆 blocks

– 1 激励 块

– 4 主要的 blocks 和 2 参数 blocks

■

程序/擦掉 控制

– embedded 字节 程序 和 块/碎片

擦掉 algorithms

– 状态 寄存器 位

■

程序 和 擦掉 suSPEND

■

为 使用 在 pc bios 产品

■

电子的 signature

– 生产者 代号: 20h

– 设备 代号: 3bh

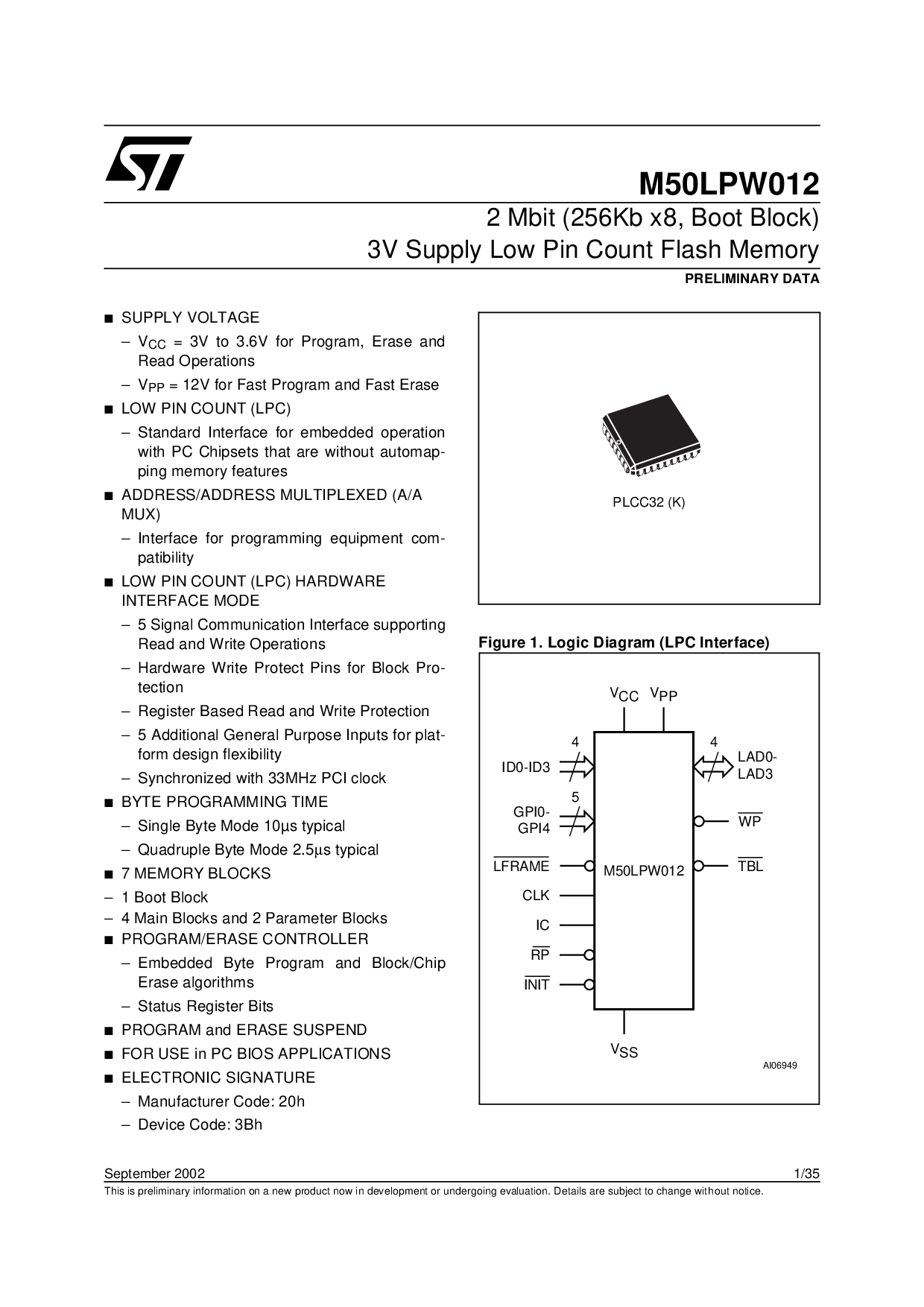

图示 1. 逻辑 图解 (lpc 接口)

AI06949

4

LFRAME

lad0-

LAD3

V

CC

M50LPW012

CLK

V

SS

4

IC

RP

TBL

5

INIT

WP

id0-id3

gpi0-

GPI4

V

PP

plcc32 (k)