ae0.1e

富士通 半导体

数据 工作表

高级 信息.

记忆

CMOS

4

×

512 k

×

32 有点

同步 动态 ram

mb81f643242c-60/-70/-10

cmos 4-银行

×

524,288-字

×

32 有点

同步 动态 随机 访问权限 记忆

■

描述

这 富士通 mb81f643242c 是 一个 cmos 同步 动态 随机 访问权限 记忆 (sdram) 包含

67,108,864 记忆 细胞 无障碍 入点 一个 32-有点 格式. 这 mb81f643242c 特点 一个 完全 同步

操作 引用 至 一个 正 边缘 时钟 由此 全部 运营 是 已同步 在 一个 时钟 输入 哪个

启用 高 业绩 和 简单 用户 接口 coexistence. 这 mb81f643242c sdram 是 设计 至

减少 这 复杂性 的 使用 一个 标准 动态 ram (dram) 哪个 需要 许多 控制 信号 计时

约束条件, 和 将 改善 数据 带宽 的 记忆 作为 很多 作为 5 次 更多 比 一个 常规 dram.

这 mb81f643242c 是 理想情况下 适合 用于 workstations, 个人 计算机, 激光 打印机, 高 分辨率 图形

适配器/accelerators 和 其他 应用程序 在哪里 一个 极其 大型 记忆 和 带宽 是 必填项 和

在哪里 一个 简单 接口 是 需要.

■

产品 线 &放大器; 特点

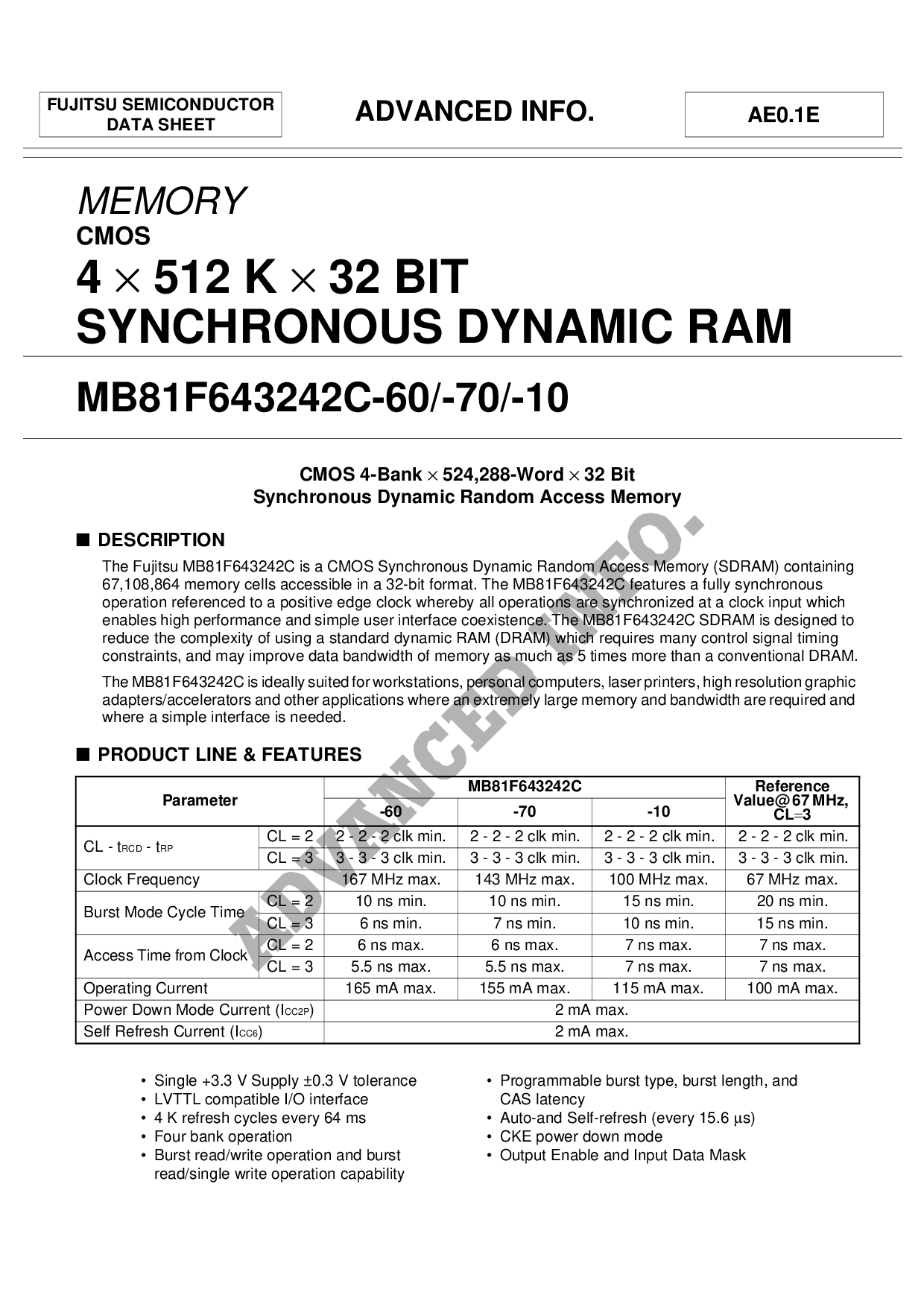

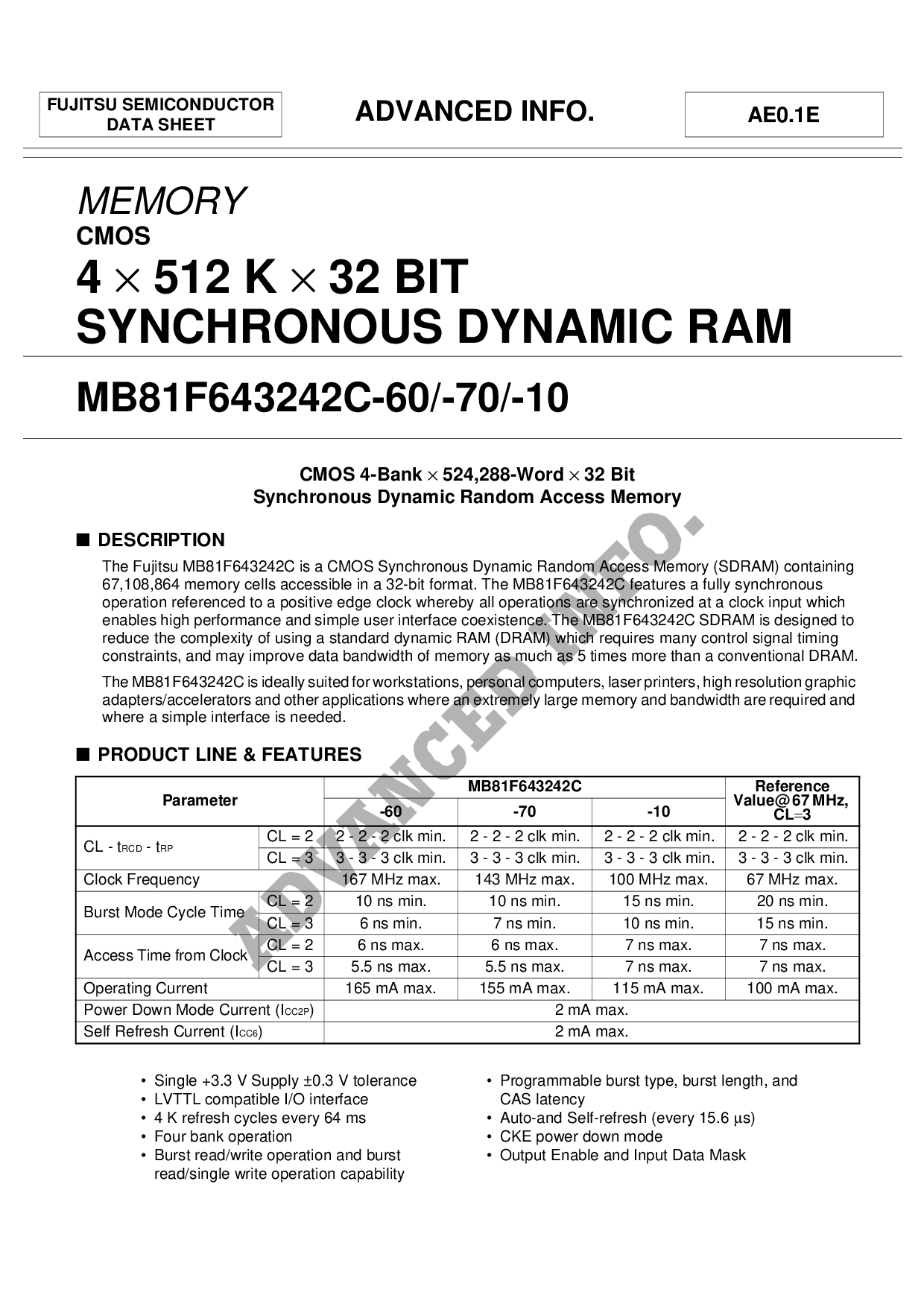

参数

MB81F643242C 参考

value@ 67 mhz,

cl

=

3

-60 -70 -10

cl - t

刚果民盟

- t

rp

cl = 2 2 - 2 - 2 clk 最小值 2 - 2 - 2 clk 最小值 2 - 2 - 2 clk 最小值 2 - 2 - 2 clk 最小值

cl = 3 3 - 3 - 3 clk 最小值 3 - 3 - 3 clk 最小值 3 - 3 - 3 clk 最小值 3 - 3 - 3 clk 最小值

时钟 频率 167 mhz 最大值 143 mhz 最大值 100 mhz 最大值 67 mhz 最大值

突发 模式 循环 时间

cl = 2 10 ns 最小值 10 ns 最小值 15 ns 最小值 20 ns 最小值

cl = 3 6 ns 最小值 7 ns 最小值 10 ns 最小值 15 ns 最小值

访问权限 时间 从 时钟

cl = 2 6 ns 最大值 6 ns 最大值 7 ns 最大值 7 ns 最大值

cl = 3 5.5 ns 最大值 5.5 ns 最大值 7 ns 最大值 7 ns 最大值

操作 电流 165 ma 最大值 155 ma 最大值 115 ma 最大值 100 ma 最大值

电源 向下 模式 电流 (我

CC2P

) 2 ma 最大值

自我 刷新 电流 (我

CC6

) 2 ma 最大值

• 单独 +3.3 v 供应 ±0.3 v 公差

• lvttl 兼容 我/o 接口

• 4 k 刷新 循环次数 每 64 ms

• 四 银行 操作

• 突发 阅读/写 操作 和 突发

阅读/单独 写 操作 能力

• 可编程 突发 类型, 突发 长度, 和

cas 延迟

• 自动-和 自刷新 (每 15.6

µ

s)

• cke 电源 向下 模式

• 输出 启用 和 输入 数据 面具