5-1

事实 数据

双 JK 负的

EdgeĆTriggered FlipĆFlop

这 mc74ac112/74act112 组成 的 二 高-速 完全地独立

转变 clocked jk flip-flops. 这 clocking 运作 是 独立 的 上升 和 下降

时间 的 这 时钟 波形. 这 jk 设计 准许 运作 作 一个 d flip-flop (谈及 至

mc74ac74/74act74 数据 薄板) 用 连接 这 j 和 k 输入 一起.

异步的 输入:

低 输入 至 s

D

(设置) sets q 至 高 水平的

低 输入 至 c

D

(clear) sets q 至 低 水平的

clear 和 设置 是 独立 的 时钟

同时发生的 低 在 c

D

和 s

D

制造 两个都 q 和 q

高

•

输出 源/下沉 24 毫安

• ′

act112 有 ttl 兼容 输入

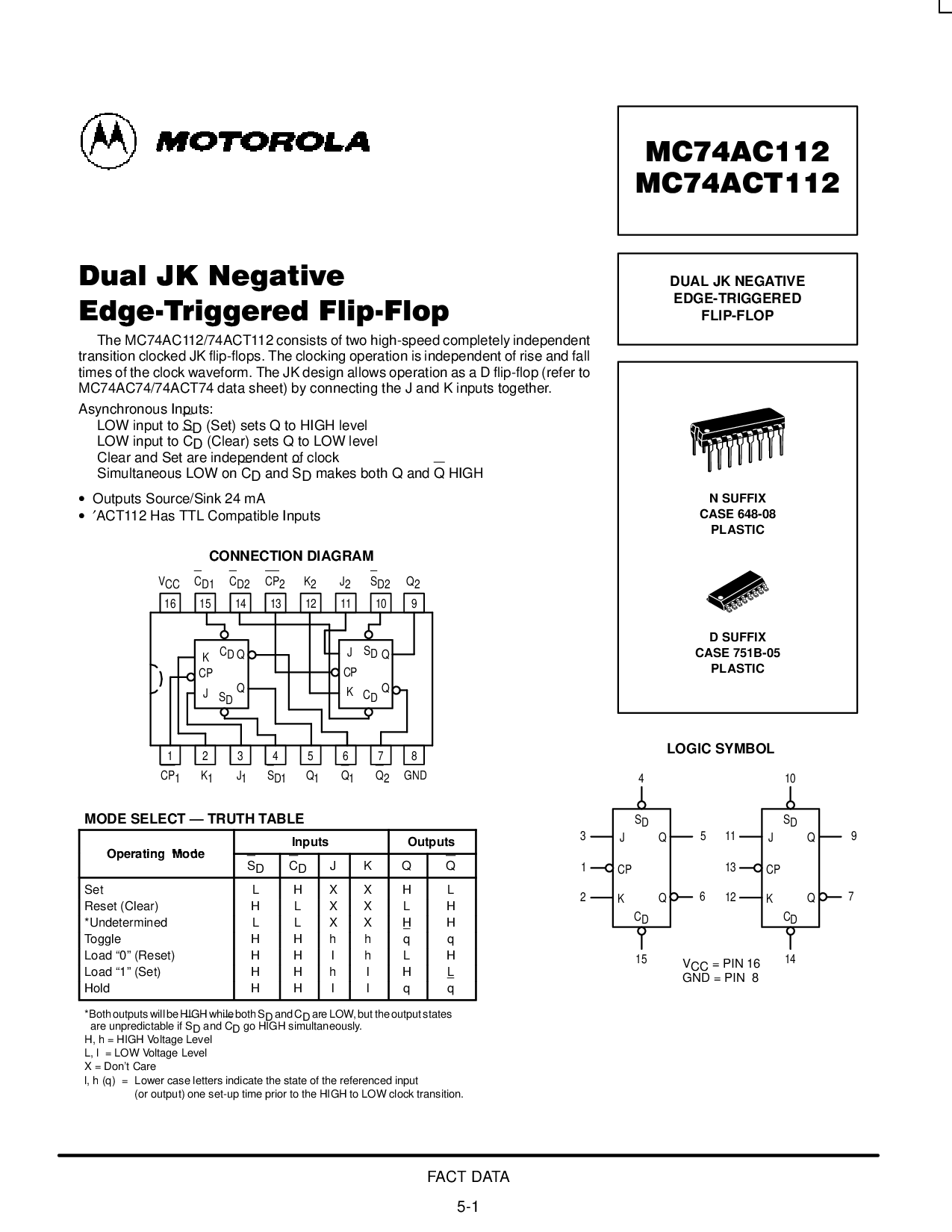

CP

V

CC

CP

1

K

1

J

1

S

D1

Q

1

Q

1

C

D1

C

D2

CP

2

K

2

J

2

S

D2

C

D

J

Q

Q

2

S

D

连接 图解

Q

2

地

1 2 3 4 5 6 7 8

910111213141516

K

Q

CP

S

D

K

Q

C

D

J

Q

模式 选择 — 真实 表格

运行 模式

输入 输出

运行 模式

S

D

C

D

J K Q Q

设置 L H X X H L

重置 (clear) H L X X L H

*Undetermined L L X X H H

Toggle H H h h q q

加载 “0” (重置) H H l h L H

加载 “1” (设置) H H h l H L

支撑 H H l l q q

h, h = 高 电压 水平的

l, l = 低 电压 水平的

x = don’t 小心

l, h (q) = 更小的 情况 letters 表明 这 状态 的 这 关联 输入

(或者 输出) 一个 设置-向上 时间 较早的 至 这 高 至 低 时钟 转变.

*Both输出 将 是 高 当 两个都 s

D

和 c

D

是 低, 但是 这 输出 states

是 unpredictable 如果 s

D

和 c

D

go 高 同时发生地.

MC74AC112

MC74ACT112

双 jk 负的

边缘-triggered

flip-flop

n 后缀

情况 648-08

塑料

d 后缀

情况 751b-05

塑料

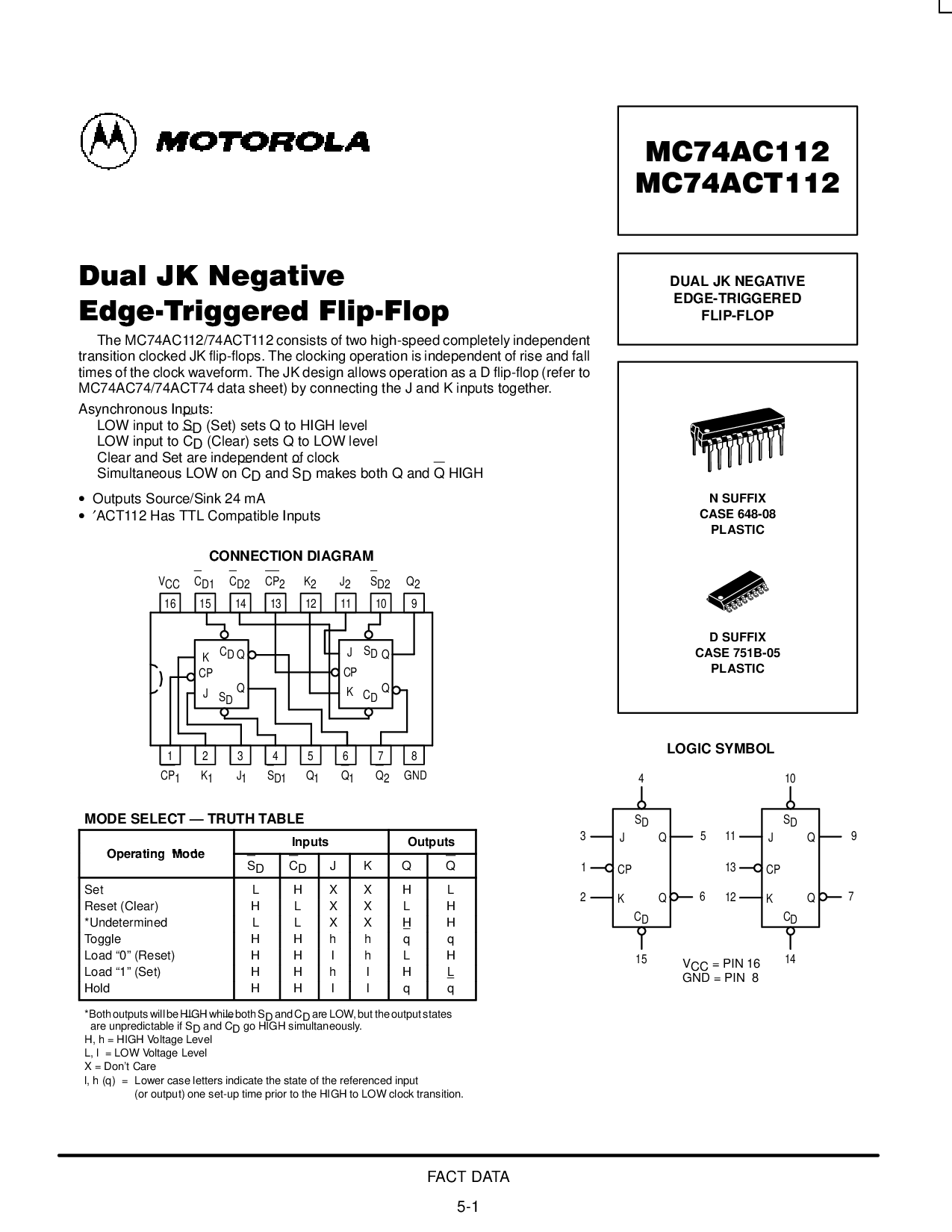

逻辑 标识

S

D

QJ

CP

Q

C

D

V

CC

= 管脚 16

地 = 管脚 8

K

3

1

2

15

4

5

6

S

D

QJ

CP

Q

C

D

K

11

13

12

14

10

9

7