半导体 组件 industries, llc, 2004

march, 2004 − rev. 2

1

发行 顺序 号码:

nlsf3t125/d

NLSF3T125

四方形 总线 缓存区

和 3−state 控制 输入

这 nlsf3t125 是 一个 高 速 cmos 四方形 总线 缓存区 fabricated

和 硅 门 cmos 技术. 它 achieves 高 速 运作

类似的 至 相等的 双极 肖特基 ttl 当 维持 cmos

低 电源 消耗.

这 nlsf3t125 需要 这 3−state 控制 输入 (oe

) 至 是 设置

高 至 放置 这 输出 在 这 高 阻抗 状态.

这 t125 输入 是 兼容 和 ttl 水平. 这个 设备 能 是

使用 作 一个 水平的 转换器 为 接合 3.3 v 至 5.0 v, 因为 它 有

全部 5.0 v cmos 水平的 输出 swings.

这 nlsf3t125 输入 结构 提供 保护 当 电压

在 0 v 和 5.5 v 是 应用, regardless 的 这 供应 电压.

这 输出 结构 也 提供 保护 当 v

CC

= 0 v. 这些

输入 和 输出 结构 帮助 阻止 设备 destruction 造成 用

供应 电压 − 输入/输出 电压 mismatch, 电池 backup, hot

嵌入, 等

这 内部的 电路 是 composed 的 三 stages, 包含 一个 缓存区

输出 这个 提供 高 噪音 免除 和 稳固的 输出. 这

输入 tolerate 电压 向上 至 7.0 v, 准许 这 接口 的 5.0 v

系统 至 3.0 v 系统.

•

高 速: t

PD

= 3.8 ns (典型值) 在 v

CC

= 5.0 v

•

低 电源 消耗: i

CC

= 4.0

一个 (最大值) 在 t

一个

= 25

°

C

•

ttl−compatible 输入: v

IL

= 0.8 v; v

IH

= 2.0 v

•

电源 向下 保护 提供 在 输入

•

保持平衡 传播 延迟

•

设计 为 2.0 v 至 5.5 v 运行 范围

•

低 噪音: v

OLP

= 0.8 v (最大值)

•

管脚 和 函数 兼容 和 其它 标准 逻辑 families

•

latchup 效能 超过 300 毫安

•

静电释放 效能: 人 身体 模型; > 2000 v,

机器 模型; > 200 v

•

碎片 complexity: 72 fets 或者 18 相等的 门

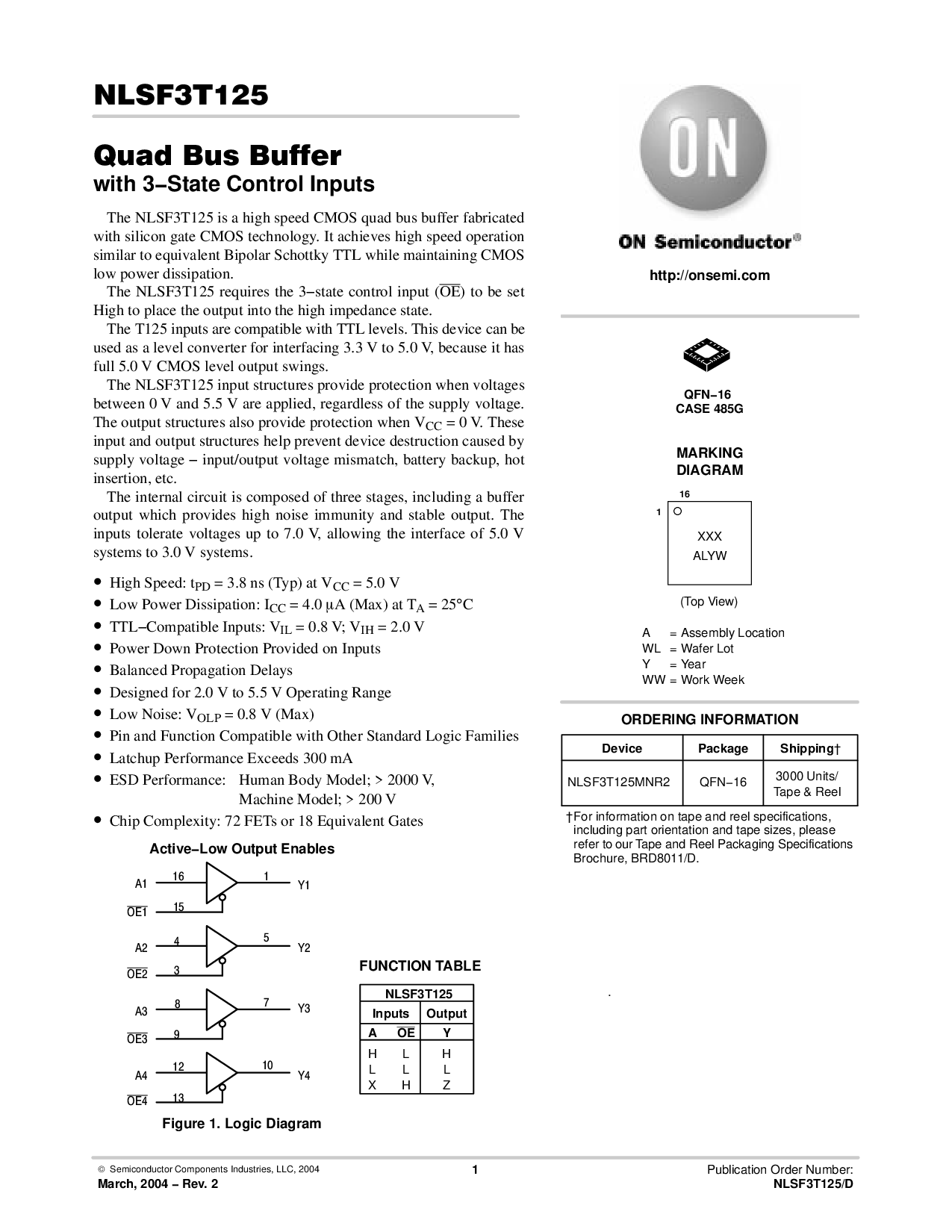

图示 1. 逻辑 图解

active−low 输出 使能

Y1

Y2

Y4

1

5

7

10

13

12

8

9

4

3

15

16

A1

OE1

A2

OE2

A3

OE3

A4

OE4

Y3

函数 表格

NLSF3T125

输入 输出

AOE

Y

HL H

LL L

XH Z

设备 包装 Shipping

†

订货 信息

NLSF3T125MNR2 QFN−16

3000 单位/

录音带 &放大; 卷轴

http://onsemi.com

16

XXX

ALYW

1

标记

图解

一个 = 组装 location

WL = 薄脆饼 lot

Y = 年

WW = 工作 week

QFN−16

情况 485g

.

(顶 视图)

†for 信息 在 录音带 和 卷轴 规格,

包含 部分 方向 和 录音带 sizes, 请

谈及 至我们的 tape 和 卷轴 包装 规格

brochure, brd8011/d.