®

altera 公司 1

Cyclone

fpga 家庭

march 2003, ver. 1.1 数据 工作表

ds-cyclone-1.1

导言

初步

信息

这 cyclone

tm

字段 可编程 闸门 阵列 家庭 是 基于 开启 一个 1.5-v,

0.13-

µ

m, 全部-图层 铜 sram 流程, 与 密度 向上 至 20,060 逻辑

元素 (莱斯) 和 向上 至 288 kbits 的 ram. 与 特点 喜欢 相位-

已锁定 循环 (plls) 用于 时钟 和 一个 专用 双 数据 费率 (ddr)

接口 至 满足 ddr sdram 和 快 循环 ram (fcram) 记忆

要求, cyclone 设备 是 一个 成本效益 解决方案 用于 数据-路径

应用程序. cyclone 设备 支持 各种 我/o 标准, 包括

lvds 在 数据 费率 向上 至 311 兆位 按 第二 (mbps) 和 66-mhz,

32-有点 外围设备 组件 互连 (pci), 用于 接口 与 和

支撑 assp 和 asic 设备. altera 也 优惠 新建 低成本 串行

配置 设备 至 配置 cyclone 设备.

特点...

■

2,910 至 20,060 莱斯, 请参见表 1

■

向上 至 294,912 ram 比特 (36,864 字节数)

■

支架 配置 通过 低成本 串行 配置 设备

■

支持 用于 lvttl, lvcmos, sstl-2, 和 sstl-3 i/o 标准

■

支持 用于 66-mhz, 32-有点 pci 标准

■

低 速度 (311 mbps) lvds 我/o 支持

■

向上 至 两个 plls 按 设备 提供 时钟 乘法 和 相位

换档

■

向上 至 八 全球 时钟 线条 与 六个 时钟 资源 可用 按

逻辑 阵列 块 (实验室) 行

■

支持 用于 外部 记忆, 包括 ddr sdram (133 mhz),

fcram, 和 单独 数据 费率 (sdr) sdram

■

支持 用于 多个 知识分子 财产 (ip) 岩心, 包括

Altera

MegaCore

功能 和 altera megafunctions 合作伙伴

程序 (ampp

sm

) megafunctions

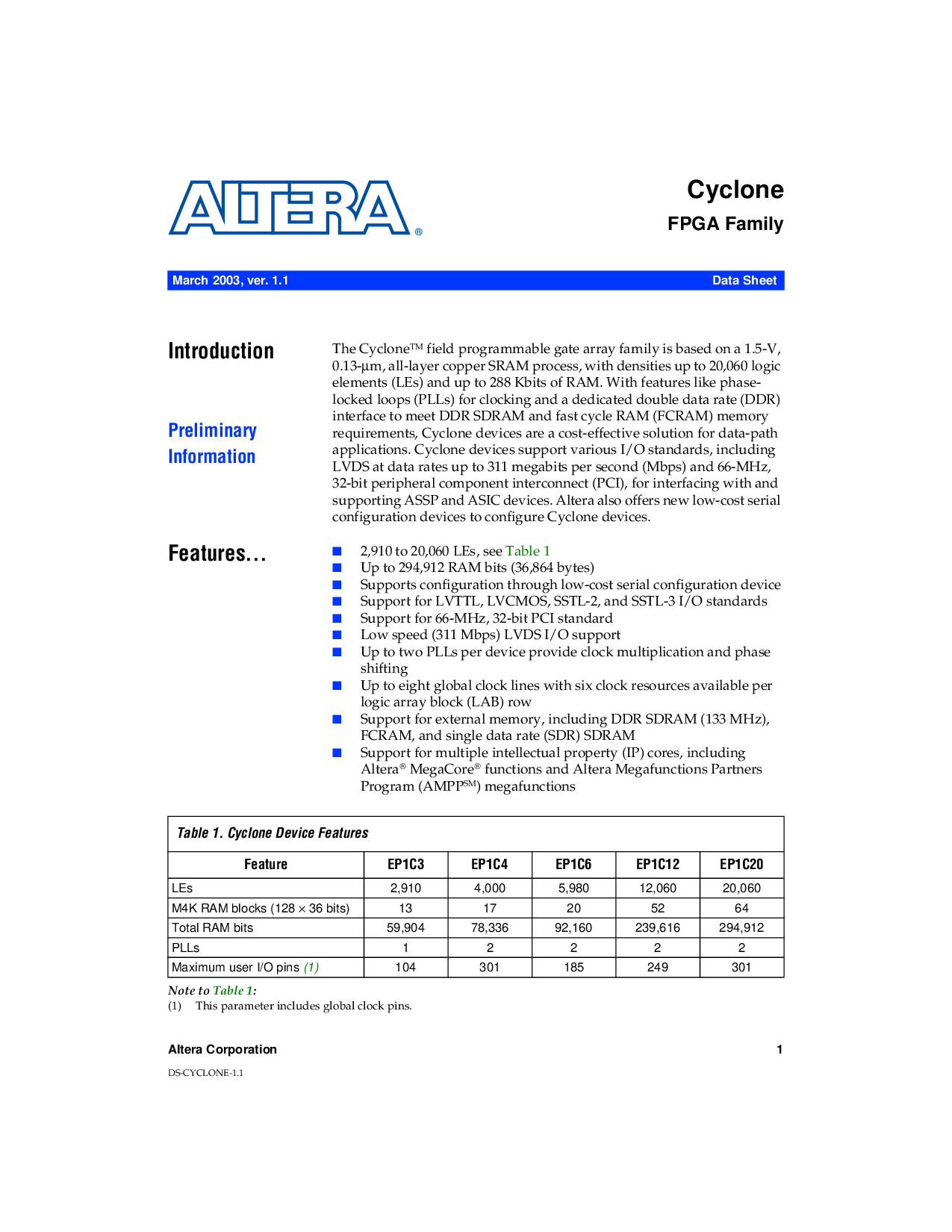

备注 至表 1:

(1) 这个 参数 包括 全球 时钟 针脚.

表 1. cyclone 设备 特点

功能 EP1C3 EP1C4 EP1C6 EP1C12 EP1C20

莱斯 2,910 4,000 5,980 12,060 20,060

m4k ram 块 (128

×

36bits)1317205264

合计 ram 比特 59,904 78,336 92,160 239,616 294,912

plls 12222

最大值 用户 我/o 针脚

(1)

104 301 185 249 301