QL2009

3.3v 和 5.0v pasic

2 fpga

结合 速, 密度, 低 费用 和 flexibility

3-35

ultimate verilog/vhdl 硅 解决方案

-abundant, 高-速 interconnect 排除 手工的 routing

-有伸缩性的 逻辑 cell 提供 高 效率

和

效能

-设计 tools 生产 快, 效率高的 verilog/vhdl 综合

速, 密度, 低 费用 和 flexibility 在 一个 设备

-16-位 计数器 speeds exceeding 200 mhz

-9,000 usable asic 门, 16,000 usable pld 门, 225 i/os

-3-layer metal vialink

处理 为 小 消逝 sizes

-100% routable 和 管脚-输出 maintainable

先进的 逻辑 cell 和 i/o 能力

-complex 功能 (向上 至 16 输入) 在 一个 单独的 逻辑 cell

-高 综合 门 utilization 从 逻辑 cell fragments

-全部 ieee 标准 jtag boundary scan 能力

-individually-控制 输入/反馈 寄存器 和 oes 在 所有 i/o 管脚

其它 重要的 家族 特性

-3.3v 和 5.0v 运作 和 低 备用物品 电源

-i/o 管脚-兼容性 在 不同的 设备 在 这 一样 包装

-pci 一致的 (在 5.0v), 全部 速 33 mhz implementations

-高 设计 安全 提供 用 安全 fuses

… 9,000

usable asic 门,

225 i/o 管脚

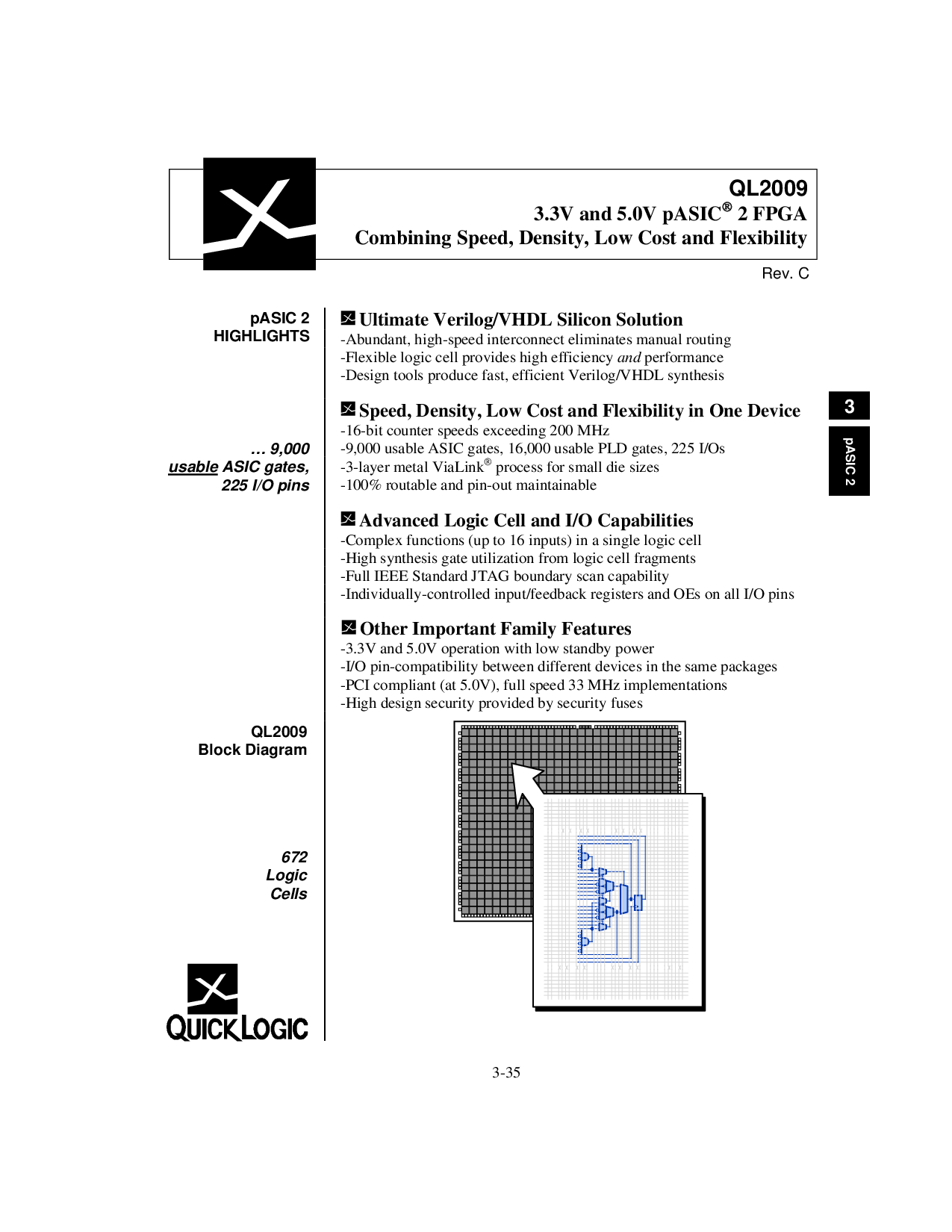

672

逻辑

Cells

pasic 2

3

QL2009

块 图解

rev. c

pasic 2

最好的部分