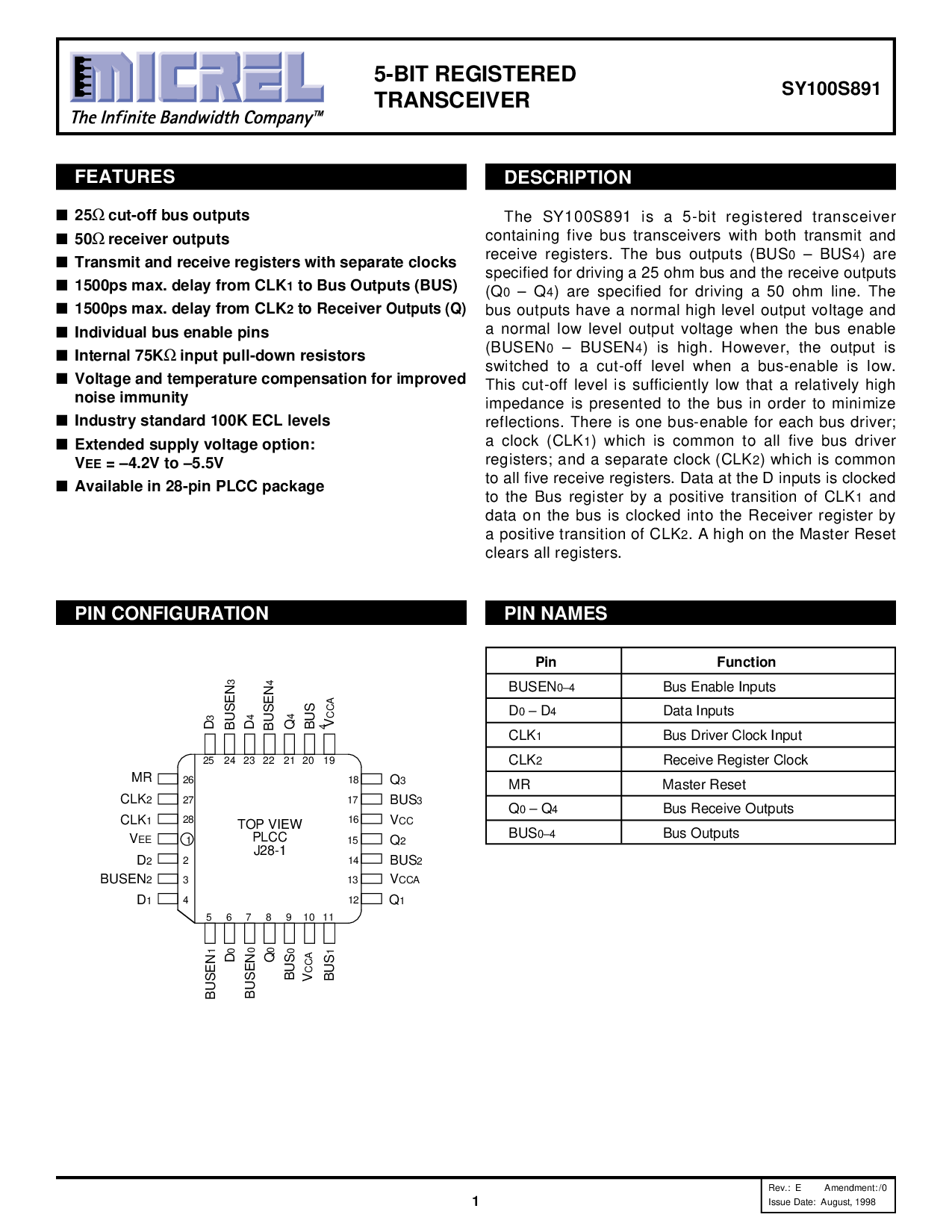

管脚 函数

BUSEN

0–4

总线 使能 输入

D

0

– d

4

数据 输入

CLK

1

总线 驱动器 时钟 输入

CLK

2

receive 寄存器 时钟

MR 主控 重置

Q

0

– q

4

总线 receive 输出

总线

0–4

总线 输出

描述

特性

■

25

Ω

截-止 总线 输出

■

50

Ω

接受者 输出

■

transmit 和 receive 寄存器 和 独立的 clocks

■

1500ps 最大值 延迟 从 clk

1

至 总线 输出 (总线)

■

1500ps 最大值 延迟 从 clk

2

至 接受者

输出 (q)

■

单独的 总线 使能 管脚

■

内部的 75k

Ω

输入 拉-向下 电阻器

■

电压 和 温度 补偿 为 改进

噪音 免除

■

工业 标准 100k ecl 水平

■

扩展 供应 电压 选项:

V

EE

= –4.2v 至 –5.5v

■

有 在 28-管脚 plcc 包装

这 sy100s891 是 一个 5-位 注册 transceiver

containing five 总线 transceivers 和 两个都 transmit 和

receive 寄存器. 这 总线 输出 (总线

0

– 总线

4

) 是

指定 为 驱动 一个 25 ohm 总线 和 这 receive 输出

(q

0

– q

4

) 是 指定 为 驱动 一个 50 ohm 线条. 这

总线 输出 有 一个 正常的 高 水平的 输出 电压 和

一个 正常的 低 水平的 输出 电压 当 这 总线 使能

(busen

0

– busen

4

) 是 高. 不管怎样, 这 输出 是

切换 至 一个 截-止 水平的 当 一个 总线-使能 是 低.

这个 截-止 水平的 是 sufficiently 低 那 一个 相当地 高

阻抗 是 提交 至 这 总线 在 顺序 至 降低

reflections. 那里 是 一个 总线-使能 为 各自 总线 驱动器;

一个 时钟 (clk

1

) 这个 是 一般 至 所有 five 总线 驱动器

寄存器; 和 一个 独立的 时钟 (clk

2

) 这个 是 一般

至 所有 five receive 寄存器. 数据 在 这 d 输入 是 clocked

至 这 总线 寄存器 用 一个 积极的 转变 的 clk

1

和

数据 在 这 总线 是 clocked 在 这 接受者 寄存器 用

一个 积极的 转变 的 clk

2

. 一个 高 在 这 主控 重置

clears 所有 寄存器.

5-位 注册

TRANSCEIVER

管脚 配置 管脚 names

SY100S891

rev.: e amendment: /0

公布 日期: 8月, 1998

顶 视图

PLCC

j28-1

26

27

28

1

2

3

4

18

17

16

15

14

13

12

Q

3

V

CC

Q

2

V

CCA

总线

3

总线

2

Q

1

25 24 23 22 21 20 19

567891011

V

EE

MR

CLK

1

BUSEN

2

D

1

CLK

2

D

2

Q

0

总线

0

总线

1

D

0

BUSEN

1

BUSEN

0

V

CCA

D

3

D

4

BUSEN

4

总线

4

BUSEN

3

Q

4

V

CCA

1