12 输出 缓存区 为 2 ddr 和 3 sram dimms

W256

Cypress 半导体 公司

• 3901 北 第一 街道 • San Jose

,

ca 95134 • 408-943-2600

文档 #: 38-07256 rev. *c 修订 8月 30, 2004

特性

• 一个 输入 至 12 output 缓存区/驱动器

• 支持 向上 至 2 ddr dimms 或者 3 sdram dimms

• 一个 额外的 输出 为 反馈

• smbus 接口 为 单独的 输出 控制

• 低 skew 输出 (< 100 ps)

• 支持 266 mhz 和 333 mhz ddr sdram

• 专心致志的 管脚 为 电源 管理 支持

• 空间-节省 28-管脚 ssop 包装

函数的 描述

这 w256 是 一个 3.3v/2.5v 缓存区 设计 至 distribute

高-速 clocks 在 pc applications. 这 部分 有 12 输出.

designers 能 配置 这些 输出 至 支持 3 unbuffered

标准 sdram dimms 和 2ddr dimms. 这 w256 能

是 使用 在 conjunction 和 这 w250-02 或者 类似的 时钟

synthesizer 为 这 通过 pro 266 chipset.

这 w256 也 包含 一个 smbus 接口 这个 能 使能

或者 使不能运转 各自 输出 时钟. 在 电源-向上, 所有 输出 clocks

是 使能 (内部的 拉-向上).

便条:

1. 内部的 100k 拉-向上 电阻器 呈现 在 输入 marked 和*. 设计 应当 不 rely solely 在 内部的 拉-向上 电阻 to 设置 i/o 管脚 高.

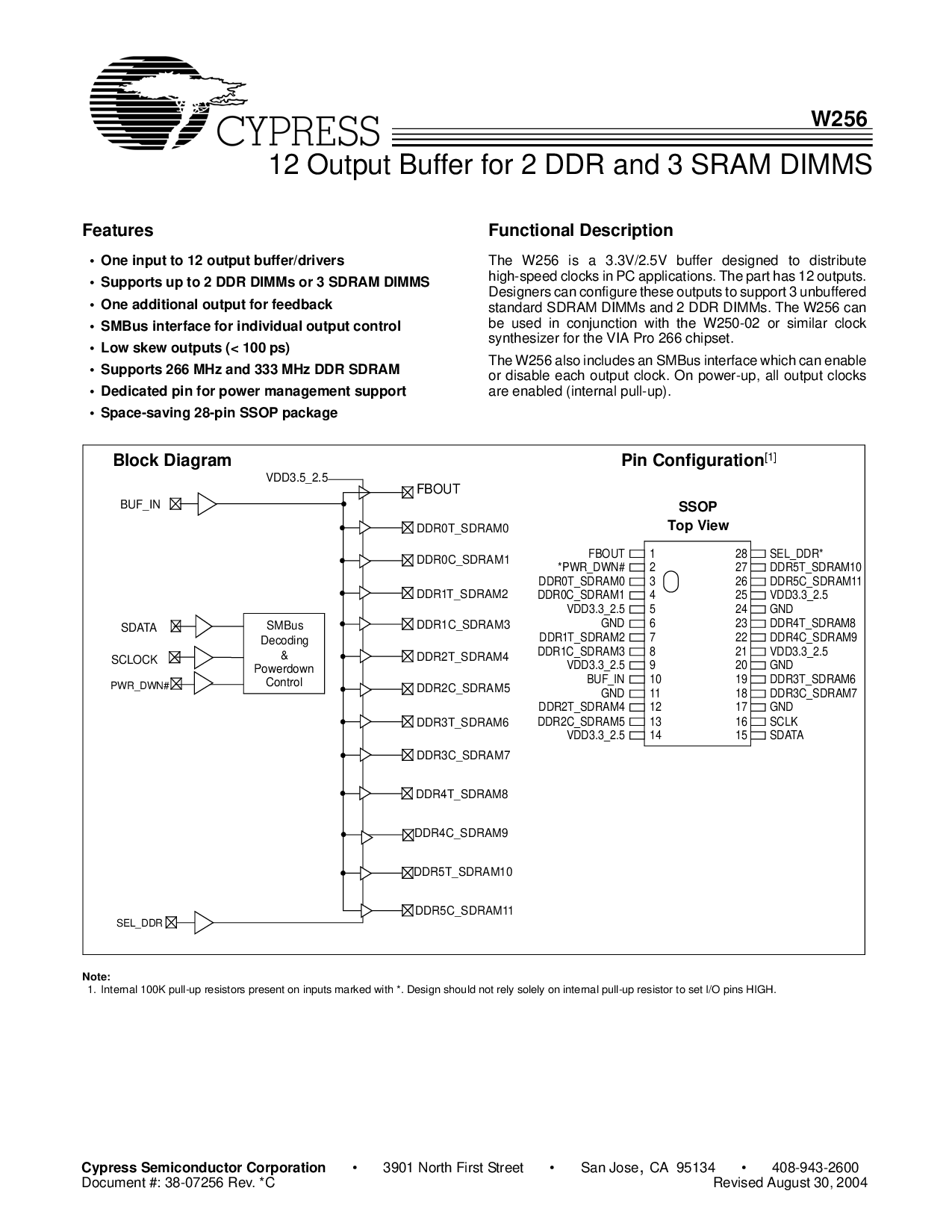

块 图解

SMBus

buf_在

SDATA

SCLOCK

ddr0t_sdram0

ddr0c_sdram1

ddr1t_sdram2

ddr1c_sdram3

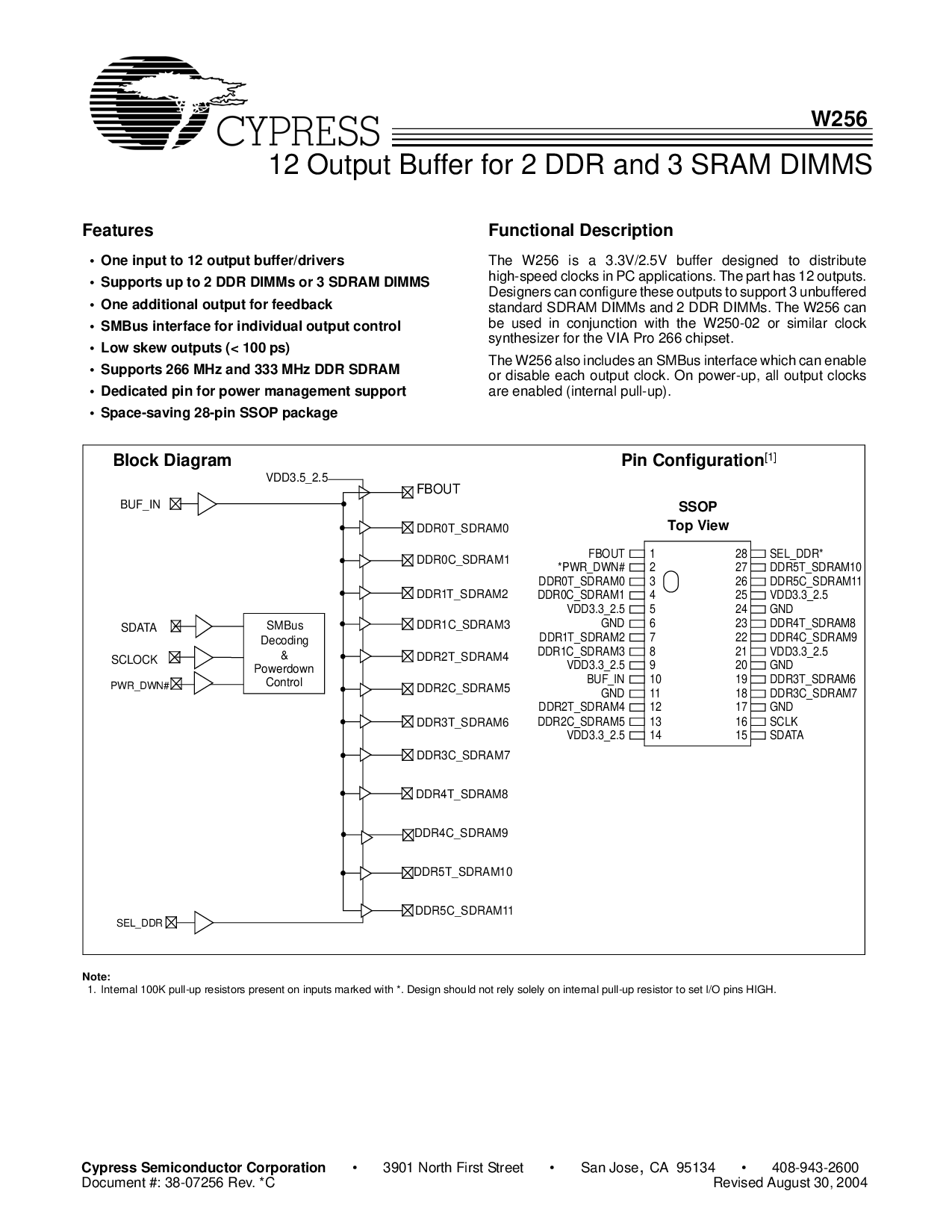

SSOP

顶 视图

管脚 配置

[1]

解码

ddr2t_sdram4

ddr2c_sdram5

ddr3t_sdram6

ddr3c_sdram7

ddr4t_sdram8

pwr_dwn#

ddr4c_sdram9

ddr5t_sdram10

ddr5c_sdram11

FBOUT

sel_ddr

FBOUT

*pwr_dwn#

ddr0t_sdram0

ddr0c_sdram1

vdd3.3_2.5

地

ddr1t_sdram2

ddr1c_sdram3

vdd3.3_2.5

buf_在

地

ddr2t_sdram4

ddr2c_sdram5

vdd3.3_2.5

sel_ddr*

ddr5t_sdram10

ddr5c_sdram11

vdd3.3_2.5

地

ddr4t_sdram8

ddr4c_sdram9

vdd3.3_2.5

地

ddr3t_sdram6

ddr3c_sdram7

地

SCLK

SDATA

28

27

26

25

24

23

22

21

20

19

18

17

16

15

1

2

3

4

5

6

7

8

9

10

11

12

13

14

&放大;

Powerdown

控制

vdd3.5_2.5