ds056 (v1.5) 8月 21, 2003

www.xilinx.com

1

初步的 产品 规格

1-800-255-7778

© 2003 xilinx, 公司 所有 权利 保留. 所有 xilinx 商标, 注册 商标, patents, 和 免责声明 是 作 列表 一个t

http://www.xilinx.com/legal.htm

.

所有 其它 商标 和 注册 商标 是 这 所有物 的 它们的 各自的 所有权人. 所有 规格 是 主题 至 change 没有 注意.

特性

• 5 ns 管脚-至-管脚 逻辑 延迟

• 系统 频率 向上 至 178 mhz

• 144 macrocells 和 3,200 usable 门

• 有 在 小 footprint 包装

- 100-管脚 tqfp (81 用户 i/o 管脚)

- 144-管脚 tqfp (117 用户 i/o 管脚)

- 144-csp (117 用户 i/o 管脚)

• 优化 为 高-效能 3.3v 系统

- 低 电源 运作

- 5v tolerant i/o 管脚 接受 5v, 3.3v, 和 2.5v

信号

- 3.3v 或者 2.5v 输出 能力

- 先进的 0.35 micron 特性 大小 cmos

快 flash™ 技术

• 先进的 系统 特性

- 在-系统 可编程序的

- 更好的 管脚-locking 和 routability 和

快 connect™ ii 转变 矩阵变换

- extra 宽 54-输入 函数 blocks

- 向上 至 90 产品-条款 每 macrocell 和

单独的 产品-期 allocation

- local 时钟 倒置 和 三 global 和 一个

产品-期 clocks

- 单独的 输出 使能 每 输出 管脚 和 local

倒置

- 输入 hysteresis 在 所有 用户 和 boundary-scan 管脚

输入

- 总线-支撑 电路系统 在 所有 用户 管脚 输入

- 全部 ieee 标准 1149.1 boundary-scan (jtag)

• 快 concurrent 程序编制

• 回转 比率 控制 在 单独的 输出

• 增强 数据 安全 特性

• 极好的 质量 和 可靠性

- 忍耐力 exceeding 10,000 程序/擦掉

循环

- 20 年 数据 保持

- 静电释放 保护 exceeding 2,000v

• 管脚-兼容 和 5v-核心 xc95144 设备 在 这

100-管脚 tqfp 包装

描述

这 xc95144xl 是 一个 3.3v cpld targeted 为 高-perfor-

mance, 低-电压 产品 在 leading-边缘 communi-

cations 和 computing 系统. 它 是 包括 的 第八

54v18 函数 blocks, 供应 3,200 usable 门 和

传播 延迟 的 5 ns. 看图示 2为 architecture

overview.

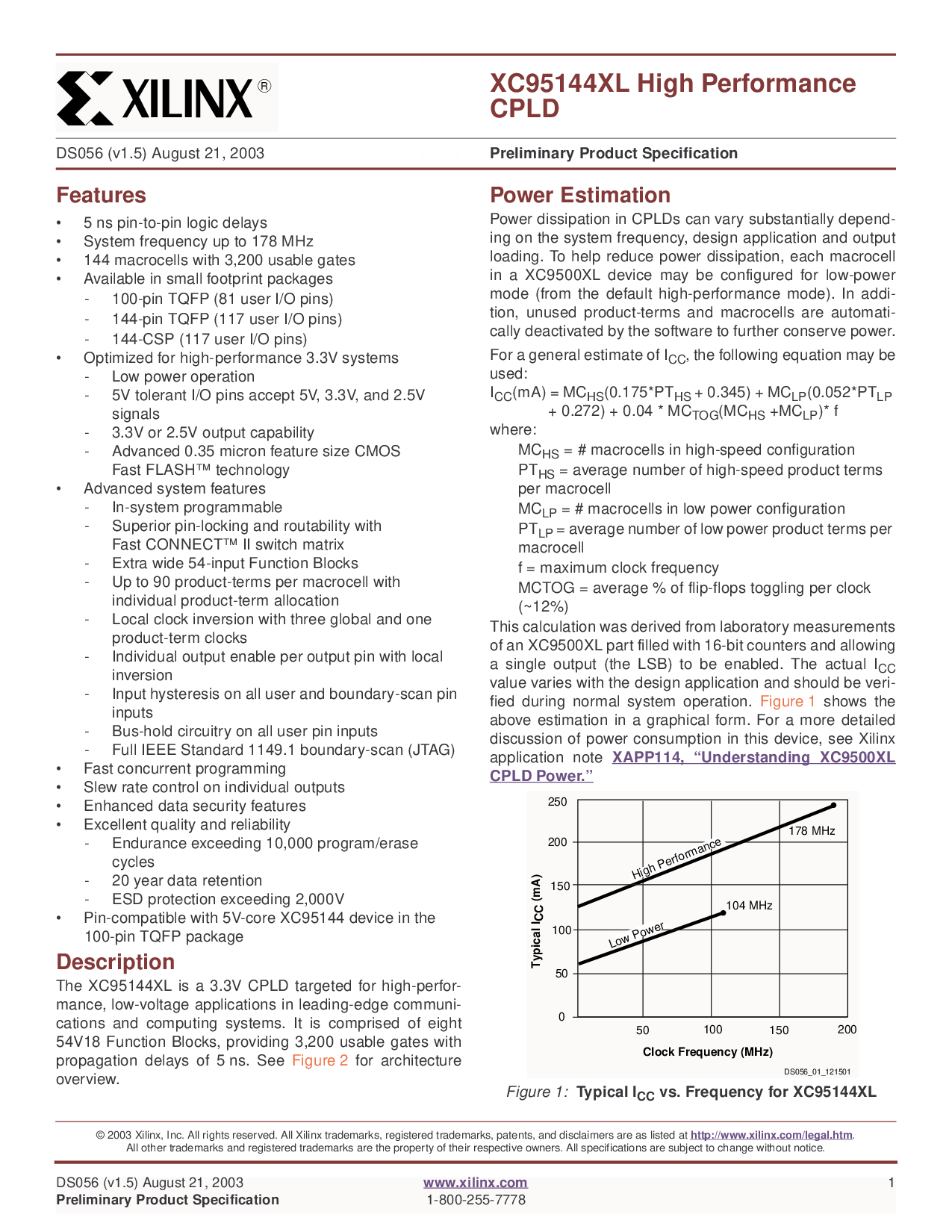

电源 estimation

电源 消耗 在 cplds 能 相异 substantially 取决于-

ing 在 这 系统 频率, 设计 应用 和 输出

加载. 至 帮助 减少 电源 消耗, 各自 macrocell

在 一个 xc9500xl 设备 将 是 配置 为 低-电源

模式 (从 这 default 高-效能 模式). 在 addi-

tion, unused 产品-条款 和 macrocells 是 自动地-

cally deactivated 用 这 软件 至 更远 conserve 电源.

为 一个 一般 估计 的 i

CC

, 这 下列的 等式 将 是

使用:

I

CC

(毫安) = mc

HS

(0.175*pt

HS

+ 0.345) + mc

LP

(0.052*pt

LP

+ 0.272) + 0.04 * mc

TOG

(mc

HS

+MC

LP

)* f

在哪里:

MC

HS

= # macrocells 在 高-速 配置

PT

HS

= 平均 号码 的 高-速 产品 条款

每 macrocell

MC

LP

= # macrocells 在 低 电源 配置

PT

LP

= 平均 号码 的 低 电源 产品 条款 每

macrocell

f = 最大 时钟 频率

mctog = 平均 % 的 flip-flops toggling 每 时钟

(~12%)

这个 计算 是 获得 从 laboratory 度量

的 一个 xc9500xl 部分 filled 和 16-位 counters 和 准许

一个 单独的 输出 (这 lsb) 至 是 使能. 这 真实的 i

CC

值 varies 和 这 设计 应用 和 应当 是 veri-

fied 在 正常的 系统 运作.图示 1显示 这

在之上 estimation 在 一个 graphical 表格. 为 一个 更多 详细地

discussion 的 电源 消耗量 在 这个 设备, 看 xilinx

应用 便条

xapp114, “understanding xc9500xl

cpld 电源.”

0

xc95144xl 高 效能

CPLD

ds056 (v1.5) 8月 21, 2003

05

初步的 产品 规格

R

图示 1:

典型 i

CC

vs. 频率 为 xc95144xl

时钟 频率 (mhz)

典型 i

CC

(毫安)

100 200

ds056_01_121501

200

250

50

50 150

150

100

0

104 mhz

高 效能

178 mhz

低

P

ower