sn54165, sn54ls165a, sn74165, sn74ls165a

并行的-加载 8-位 变换 寄存器

sdls062d – october 1976 – 修订 二月 2002

1

邮递 办公室 盒 655303

•

达拉斯市, 德州 75265

D

complementary 输出

D

直接 overriding 加载 (数据) 输入

D

gated 时钟 输入

D

并行的-至-串行 数据 转换

类型

典型 最大

时钟 频率

典型

电源 消耗

’165 26 mhz 210 mw

’LS165A 35 mhz 90 mw

描述

这 ’165 和 ’ls165a 是 8-位 串行 变换

寄存器 那 变换 这 数据 在 这 方向 的 q

一个

对着 q

H

当 clocked. 并行的-在 进入 至

各自 平台 是 制造 有 用 第八 单独的,

直接 数据 输入 那 是 使能 用 一个 低 水平的

在 这 变换/加载 (sh/ld

) 输入. 这些 寄存器

也 特性 gated 时钟 (clk) 输入 和

complementary 输出 从 这 eighth 位. 所有

输入 是 二极管-clamped 至 降低

传递-线条 影响, 因此 simplifying

系统 设计.

clocking 是 accomplished 通过 一个 二-输入

积极的-也不 门, permitting 一个 输入 至 是

使用 作 一个 时钟-inhibit 函数. 支持 也 的

这 时钟 输入 高 inhibits clocking, 和 支持

也 时钟 输入 低 和 sh/ld

高 使能 这

其它 时钟 输入. 时钟 inhibit (clk inh) 应当

是 changed 至 这 高 水平的 仅有的 当 clk 是

高. 并行的 加载 是 inhibited 作 长 作 sh/ld

是 高. 数据 在 这 并行的 输入 是 承载

直接地 在 这 寄存器 当 sh/ld

是 低,

independently 的 这 水平 的 clk, clk inh, 或者

串行 (ser) 输入.

这 sn54165 和 sn74165 设备

是 废弃的 和 是 非 变长 有提供的

.

版权

2002, 德州 器械 组成公司的

请 是 知道 那 一个 重要的 注意 涉及 有效性, 标准 保用单, 和 使用 在 核心的 产品 的

德州 器械 半导体 产品 和 免责声明 附之 呈现 在 这 终止 的 这个 数据 薄板.

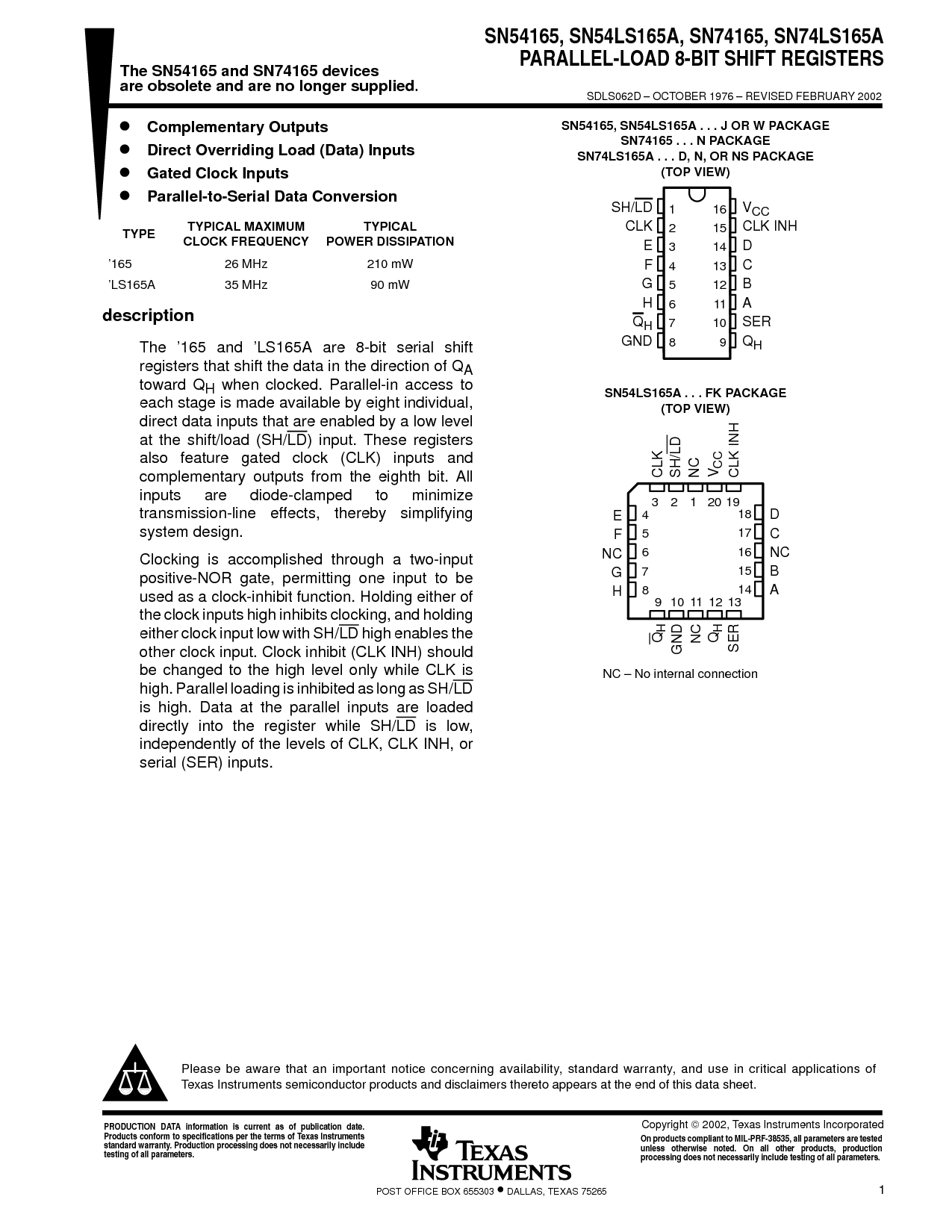

sn54165, sn54ls165a ...j 或者 w pACKAGE

SN74165 ...n pACKAGE

SN74LS165A . . . d, n, 或者 ns 包装

(顶 视图)

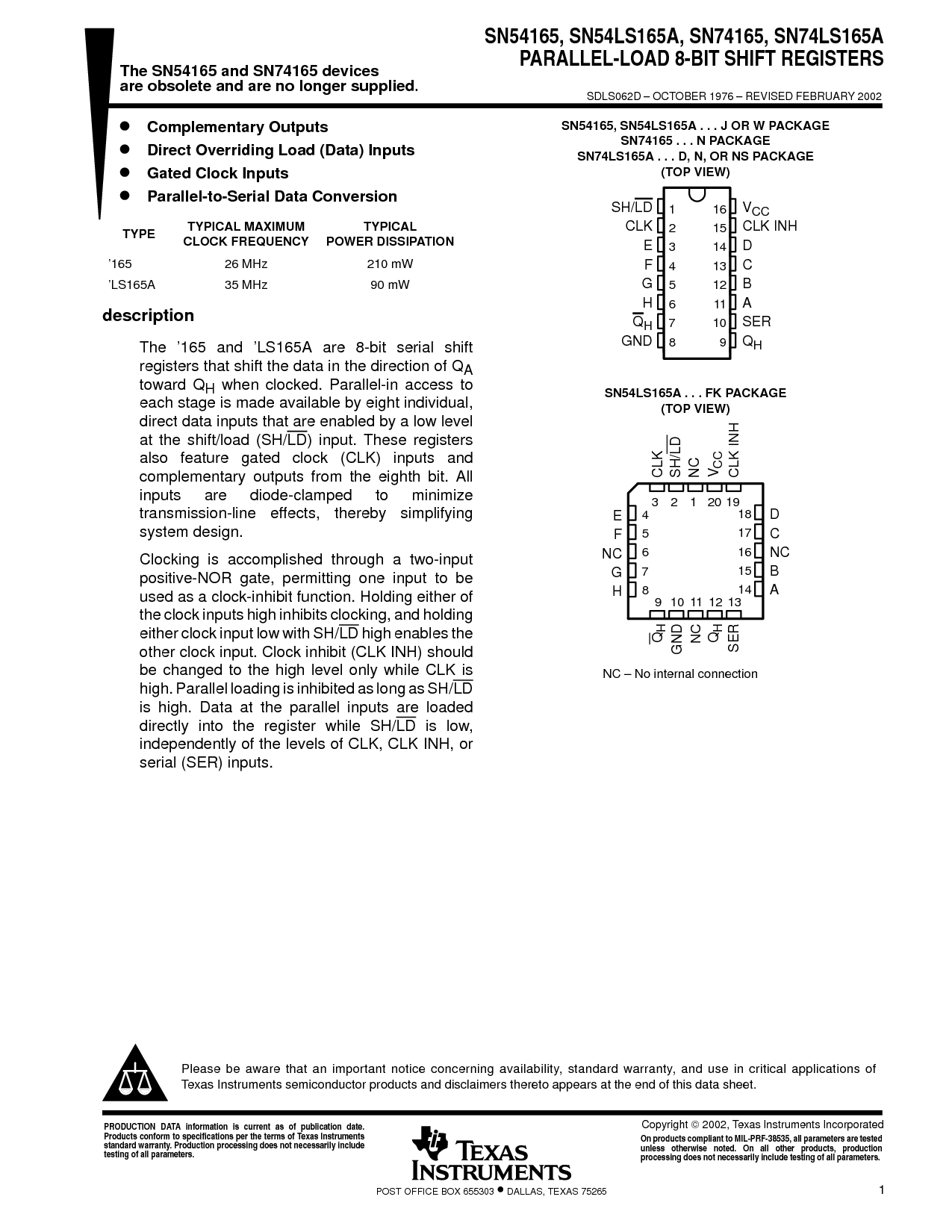

3212019

910111213

4

5

6

7

8

18

17

16

15

14

D

C

NC

B

一个

E

F

NC

G

H

SN54LS165A . . . fk 包装

(顶 视图)

CLK

sh/ld

NC

SER

clk inh

H

地

NC

V

CC

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

sh/ld

CLK

E

F

G

H

Q

H

地

V

CC

clk inh

D

C

B

一个

SER

Q

H

Q

H

Q

nc – 非 内部的 连接

生产 数据 信息 是 电流 作 的 发行 日期.

产品 遵从 至 规格 每 这 条款 的 德州 器械

标准 保用单. 生产 处理 做 不 必然地 包含

测试 的 所有 参数.

在 产品 一致的 至 mil-prf-38535, 所有 参数 是 测试

除非 否则 指出. 在 所有 其它 产品, 生产

处理 做 不 必然地 包含 测试 的 所有 参数.