3.3v 32k/64k x 16/18 双-端口 静态的 内存

cy7c027v/028v

cy7c037v/038v

铅

含铅的-自由

Cypress 半导体 公司

• 3901 北 第一 街道 • San Jose

,

ca 95134 • 408-943-2600

文档 #: 38-06078 rev. *a 修订 九月 20, 2004

特性

• 真实 双-ported 记忆 cells 这个 准许

同时发生的 进入 的 这 一样 记忆 location

• 32k x 16 organization (cy7c027v)

• 64k x 16 organization (cy7c028v)

• 32k x 18 organization (cy7c037v)

• 64k x 18 organization (cy7c038v)

• 0.35-micron cmos for 最佳的 速/电源

• 高-速 进入: 15/20/25 ns

• 低 运行 电源

—

起作用的: i

CC

= 115 毫安 (典型)

— 备用物品: i

SB3

= 10

µ

一个 (典型)

• 全部地 异步的 运作

• 自动 电源-向下

• expandable 数据 总线 至 32/36 位 或者 更多 使用 mas-

ter/从动装置 碎片 选择 当 使用 更多 比 一个 设备

• 在-碎片 arbitration 逻辑

• semaphores 包含 至 准许 软件 handshaking

在 端口

•INT

标记 为 端口-至-端口 交流

• 独立的 upper-字节 和 更小的-字节 控制

• 双 碎片 使能

• 管脚 选择 为 主控 或者 从动装置

• 商业的 和 工业的 温度 范围

• 100-管脚 含铅的(铅)-自由 tqfp 和 100-管脚 tqfp

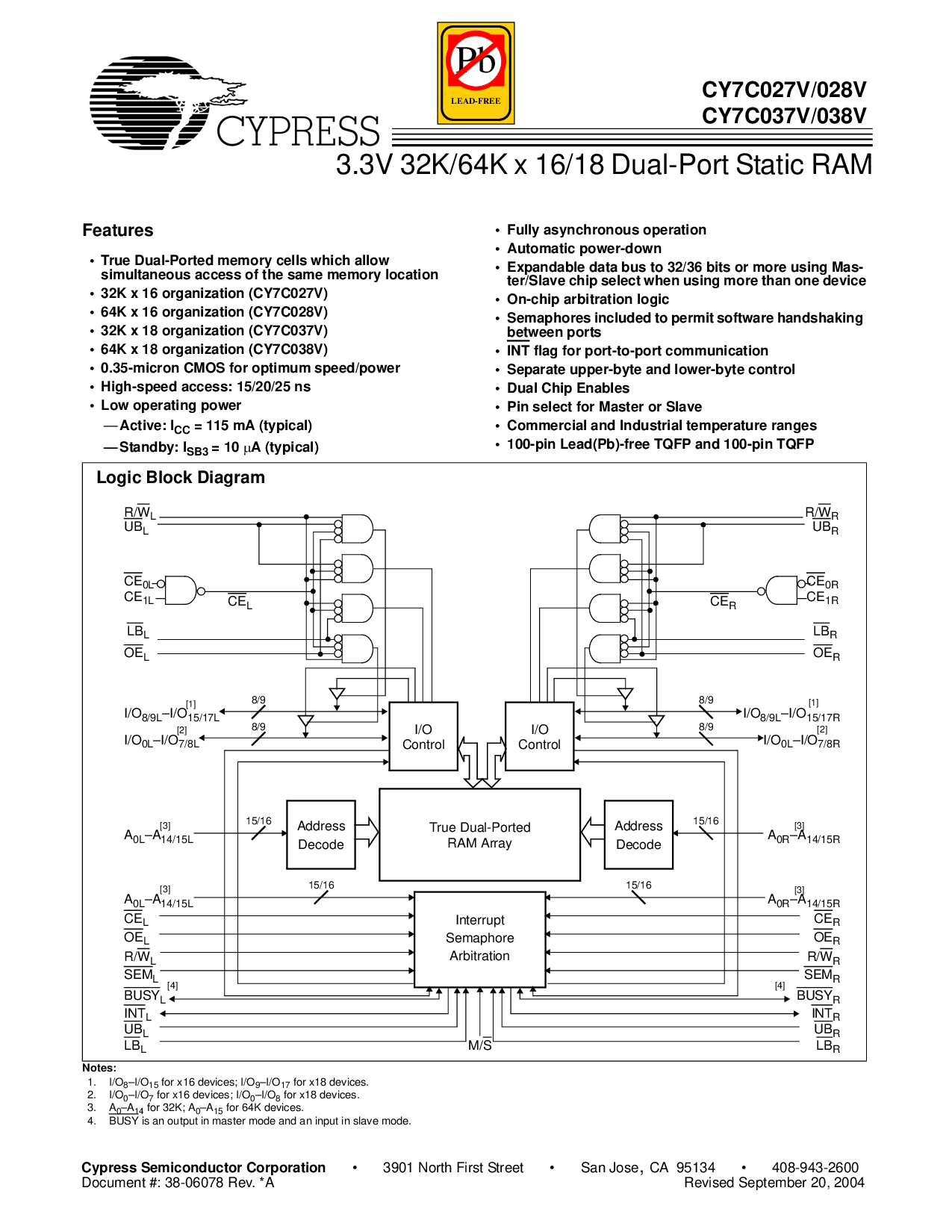

注释:

1. i/o

8

–i/o

15

为 x16 设备; i/o

9

–i/o

17

为 x18 设备.

2. i/o

0

–i/o

7

为 x16 设备; i/o

0

–i/o

8

为 x18 设备.

3. 一个

0

–A

14

为 32k; 一个

0

–A

15

为 64k 设备.

4. BUSY

是 一个 输出 在 主控 模式 和 一个 输入 在 从动装置 模式.

r/w

L

CE

0L

CE

1L

OE

L

i/o

8/9l

–i/o

15/17l

i/o

控制

地址

Decode

一个

0L

–A

14/15l

CE

L

OE

L

r/w

L

BUSY

L

i/o

控制

CE

L

中断

Semaphore

Arbitration

SEM

L

INT

L

m/s

UB

L

LB

L

i/o

0L

–i/o

7/8l

r/w

R

CE

0R

CE

1R

OE

R

i/o

8/9l

–i/o

15/17r

CE

R

UB

R

LB

R

i/o

0L

–i/o

7/8r

UB

L

LB

L

逻辑 块 图解

一个

0L

–A

14/15l

真实 双-ported

内存 排列

一个

0R

–A

14/15r

CE

R

OE

R

r/w

R

BUSY

R

SEM

R

INT

R

UB

R

LB

R

地址

Decode

一个

0R

–A

14/15r

[1]

[1]

[2]

[2]

[3]

[3]

[4]

[4]

[3] [3]

15/16

8/9

8/9

15/16

8/9

8/9

15/16 15/16