TLF8588

DP8420A21A22A microCMOS 可编程序的 256k1M4M 动态 内存 ControllerDrivers

July 1992

DP8420A21A22A microCMOS 可编程序的

256k1M4M 动态 内存 ControllerDrivers

一般 描述

这 DP8420A21A22A 动态 内存 控制者 提供 一个

低 cost 单独的 碎片 接口 在 动态 内存 和

所有 8- 16- 和 32-位 systems 这 DP8420A21A22A gen-

erate 所有 这 必需的 进入 控制 信号 定时 为

DRAMs 一个 在-碎片 refresh 要求 时钟 是 使用 至 自动-

matically refresh 这 DRAM array Refreshes 和 accesses

是 arbitrated 在 chip 如果 necessary 一个 WAIT

或者 DTACK 输出-

放 inserts wait states 在 系统 进入 cycles 包含

burst 模式 accesses RAS

低 时间 在 refreshes 和

RAS

precharge 时间 之后 refreshes 和 后面的 至 后面的 交流-

cesses 是 有保证的 通过 这 嵌入 的 wait states

独立的 在-碎片 precharge counters 为 各自 RAS

输出

能 是 使用 为 记忆 interleaving 至 避免 delayed 后面的

至 后面的 accesses 因为 的 precharge 一个 额外的 fea-

ture 的 这 DP8422A 是 二 进入 端口 至 使简化 双

accessing Arbitration among 这些 端口 和 refresh 是

完毕 在 chip

特性

Y

在 碎片 高 精确 延迟 线条 至 保证 核心的

DRAM 进入 定时 参数

Y

microCMOS 处理 为 低 电源

Y

高 电容 驱动器 为 RAS CASWE和 DRAM

地址 在 碎片

Y

在 碎片 支持 为 nibble 页 和 静态的 column

DRAMs

Y

字节 使能 信号 在 碎片 准许 字节 writing 在 一个 文字

大小 向上 至 32 位 和 非 外部 逻辑

Y

选择 的 控制 speeds 20 MHz 和 25 MHz

Y

在 板 端口 APort B (dp8422a 仅有的)refresh arbitra-

tion 逻辑

Y

直接 接口 至 所有 主要的 微处理器 (applica-

tion 注释 有)

Y

4 RAS 和 4 CAS 驱动器 (这 RAS 和 CAS configura-

tion 是 可编程序的)

的 管脚

的 地址

Largest 直接 驱动 进入

控制

(plcc) 输出

DRAM 记忆 端口

可能 Capacity 有

DP8420A 68 9 256 kbit 4 Mbytes 单独的 进入 端口

DP8421A 68 10 1 Mbit 16 Mbytes 单独的 进入 端口

DP8422A 84 11 4 Mbit 64 Mbytes 双 进入 端口 (一个 和 b)

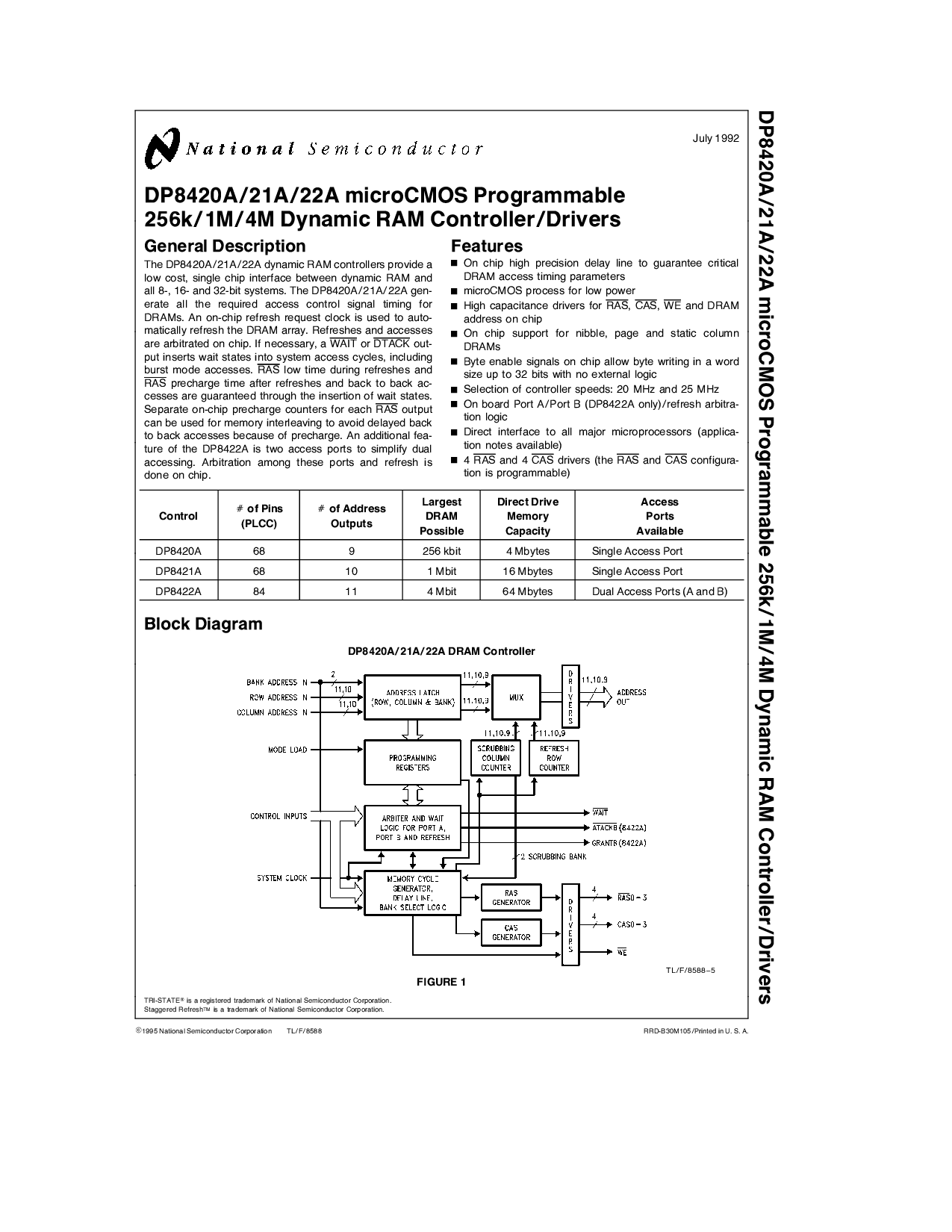

块 图解

DP8420A21A22A DRAM 控制

TLF8588–5

图示 1

触发-状态

是 一个 注册 商标 的 国家的 半导体 Corporation

Staggered Refresh

TM

是 一个 商标 的 国家的 半导体 Corporation

C

1995 国家的 半导体 公司 rrd-b30m105printed 在 U S A