7-886

提醒: 这些 设备 是 敏感的 至 静电的 释放; follow 恰当的 ic 处理 程序.

1-888-intersil 或者 321-724-7143 | 版权 © intersil 公司 1999

CD4046BMS

cmos 微小功率 阶段 锁 循环

描述

cd4046bms cmos 微小功率 阶段-锁 循环 (pll)

组成 的 一个 低 电源 直线的 电压-控制 振荡器 (vco)

和 二 不同的 阶段 comparators having 一个 一般 信号-

输入 amplifier 和 一个 一般 比较器 输入. 一个 5.2v 齐纳

二极管 是 提供 为 供应 规章制度 如果 需要.

这 cd4046bms 是 有提供的 在 这些 16-含铅的 外形 包装:

vco 部分

这 vco 需要 一个 外部 电容 c1 和 一个 或者 二

外部 电阻器 (r1 或者 r1 和 r2). 电阻 r1 和 电容

c1 决定 这 频率 范围 的 这 vco 和 电阻 r2

使能 这 vco 至 有 一个 频率 补偿 如果 必需的. 这 高

输入 阻抗 (10

12

Ω

) 的 这 vco simplifies 这 设计 的 低

通过 filters 用 permitting 这 设计者 一个 宽 选择 的 电阻-

至-电容 ratios. 在 顺序 不 至 加载 这 低-通过 filter, 一个

源-追随着 输出 的 这 vco 输入 电压 是 提供 在 ter-

minal 10 (demodulated 输出). 如果 这个 终端 是 使用, 一个

加载 电阻 (rs) 的 10k

Ω

或者 更多 应当 是 连接 从

这个 终端 至 vss. 如果 unused 这个 终端 应当 是 left 打开.

这 vco 能 是 连接 也 直接地 或者 通过 频率

dividers 至 这 比较器 输入 的 这 阶段 comparators. 一个 全部

cmos 逻辑 摆动 是 有 在 这 输出 的 这 vco 和

准许 直接 连接 至 cmos 频率 dividers 此类 作 这

intersil cd4024, cd4018, cd4020, cd4029, 和 cd4050. 一个

或者 更多 cd4018 (preset 表格 分隔-用-n 计数器) 或者 cd4029

(presettable 向上/向下 计数器) 或者 cd4029 (presettable divide-

用-n 计数器) 或者 cd4029 (presettable 向上/向下 counter), 或者

cd4059a (可编程序的 分隔-用 “n” 计数器), 一起 和

这 cd4046bms (阶段-锁 循环) 能 是 使用 至 build 一个

微小功率 低-频率 synthesizer. 一个 逻辑 0 在 这 inhibit

输入 “enables” 这 vco 和 这 源 追随着, 当 一个 逻辑 1

“turns off” 两个都 至 降低 保卫-用 电源 消耗量.

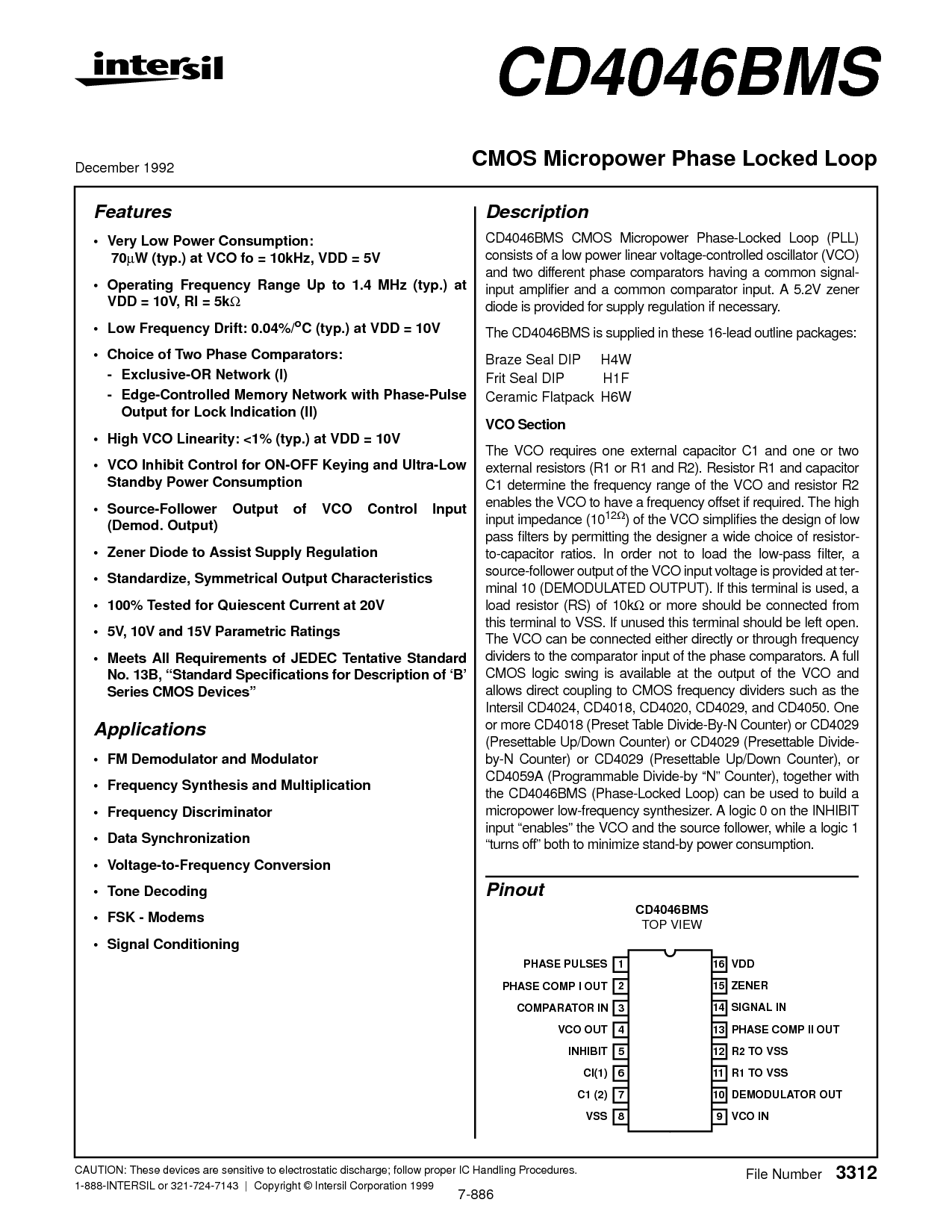

引脚

CD4046BMS

顶 视图

braze seal 插件 H4W

frit seal 插件 H1F

陶瓷的 flatpack H6W

14

15

16

9

13

12

11

10

1

2

3

4

5

7

6

8

阶段 脉冲

阶段 竞赛 i 输出

比较器 在

vco 输出

INHIBIT

ci(1)

VSS

c1 (2)

VDD

信号 在

阶段 竞赛 ii 输出

r2 至 vss

r1 至 vss

demodulator 输出

vco 在

齐纳

特性

• 非常 低 电源 消耗量:

70

µ

w (典型值.) 在 vco fo = 10khz, vdd = 5v

• 运行 频率 范围 向上 至 1.4 mhz (典型值.) 在

vdd = 10v, ri = 5k

Ω

• 低 频率 逐渐变化: 0.04%/

o

c (典型值.) 在 vdd = 10v

• 选择 的 二 阶段 comparators:

- 独有的-或者 网络 (i)

- 边缘-控制 记忆 网络 和 阶段-脉冲波

输出 为 锁 indication (ii)

• 高 vco 线性: <1% (典型值.) 在 vdd = 10v

• vco inhibit 控制 为 在-止 keying 和 过激-低

备用物品 电源 消耗量

• 源-追随着 输出 的 vco 控制 输入

(demod. 输出)

• 齐纳 二极管 至 assist 供应 规章制度

• standardize, 对称的 输出 特性

• 100% 测试 为 安静的 电流 在 20v

• 5v, 10v 和 15v 参数 比率

• 满足 所有 (所需的)东西 的 电子元件工业联合会 tentative 标准

非. 13b, “standard specifications 为 描述 的 ‘b’

序列 cmos devices”

产品

• fm demodulator 和 modulator

• 频率 综合 和 multiplication

• 频率 discriminator

• 数据 同步

• 电压-至-频率 转换

• 声调 解码

• fsk - modems

• 信号 conditioning

12月 1992

文件 号码

3312