12月 4, 1998 (version

3.0

)

1

特点

•7.5 ns pin-to-pin逻辑 延误 开启 全部 针脚

•f

cnt

to 125 mhz

•72 宏单元 与 1,600可用 gate?s

•向上 至72 美国e?右 我/o pins

•5 v 在系统内 程序m能 (isp)

-Endurance?的 10,000 程序/擦除 cycle?s

-程序/擦除over 已满 商业 电压 和

温度 范围

•增强型 管脚-锁定 体系结构

•灵活 36v18 功能B锁

-90 产品 条款 驱动器 任何 或 全部 的 18 宏单元

内 功能 块

-Glob一个l 一个d产品 期限 时钟, 输出 启用, 设置

和 rese?t 信号

•分机e?nsive ieee std1149.1 boundary-sc一个n (jtag)

支持

•可编程 电源 红色u运动 模式 入点 每个

宏单元

•回转 费率 控制on individu铝 出点puts

•用户 程序一个mmable?接地p入点 能力

•分机e?nded 图案 秒urity 特点 用于设计 保护

•高驱动 24m一个oUtutut也

•3.3 v 或 5 v 我/ocapab能力

•高级cmos 5v fastflashte?技术

•支架 平行 专业版g夯实 的 更多 比 一个

xc9500 同时

•一个可用 入点 44-管脚 plcc, 84-管脚 plcc,100-管脚 pqfp

和 100-管脚 tqfp 软件包

描述

这 xc9572 是一个 高-性能ormance?CPLD提供

advance?d 系统内m编程 和test盖一个bilities 用于

概述 purpose 逻辑 integ定量.我t是 包括d的 四

36v18 功能 块, 提供 1,600 可用 盖茨 与

道具一个gation 延误的 7.5ns. see?Figure?2用于 the?建筑结构-

真实overview.

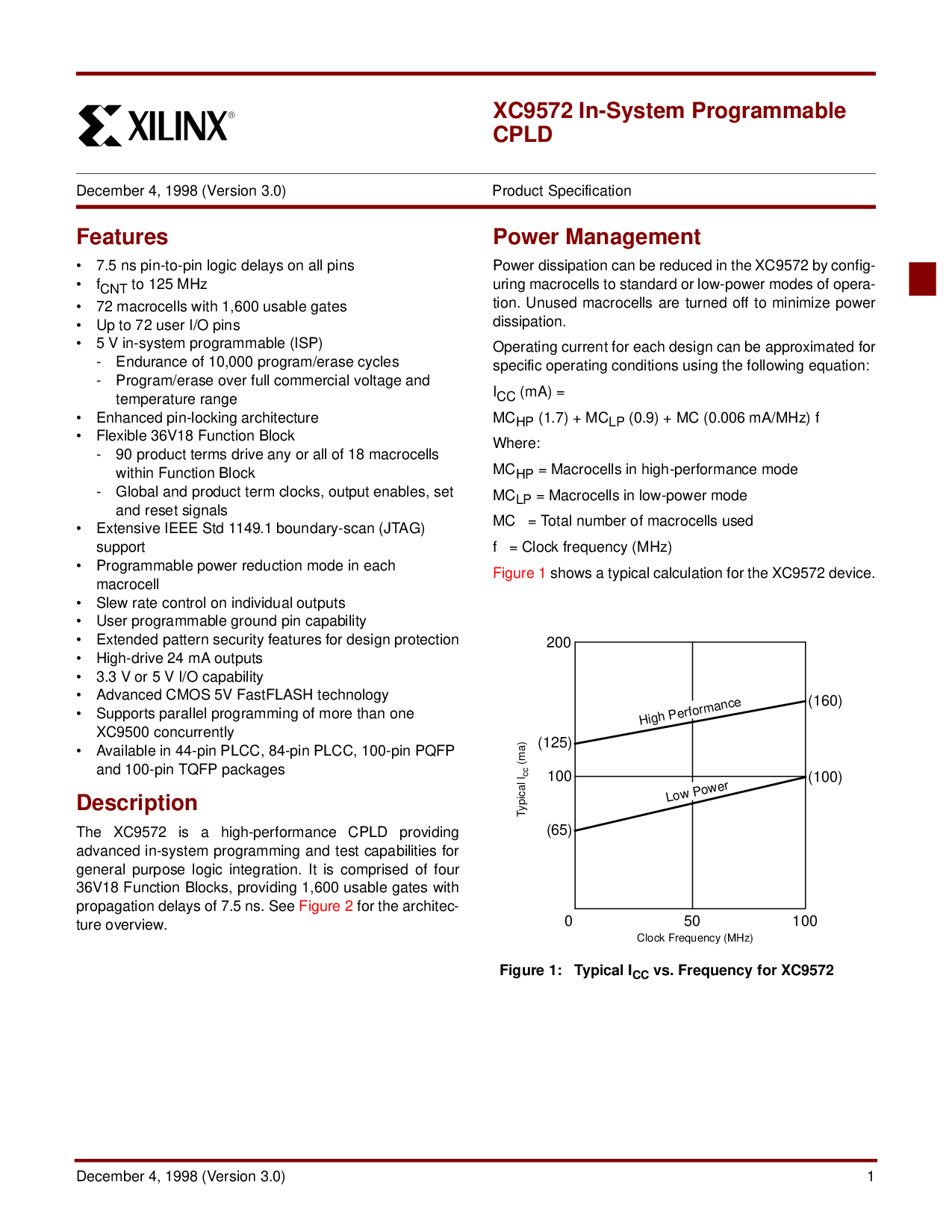

电源 管理

powe?右 耗散 可以 是 减少 入点 这 xc9572by 配置-

uringmacro细胞 至 standard 或低功耗modes 的 歌剧-

操作. 未使用 宏单元 是 转弯e?doff 至 minimize采购订单wer

耗散.

操作gcurrent 用于 每个 设计 可以 是 近似值d用于

具体 操作 条件ons 使用 这 following 方程:

我

抄送

(ma)=

mc

HP

(1.7) + mc

lp

(0.9) + mc (0.006 ma/mhz) f

在哪里:

mc

HP

= 宏单元 入点 high-按formance 模式

mc

lp

= 宏单元 入点 low-采购订单wer 模式

mc =t奥塔尔 号码of 宏单元已使用

f = 时钟 频率 (mhz)

Figure?1显示 一个typical 计算 用于 这 xc9572 设备.

1

xc9572 在系统内 可编程

CPLD

12月 4, 1998 (ve?rsion 3.0)

11*

产品sp环保

图 1:typical 我

抄送

vs. 频率 用于 xc9572

0

100

200

(65)

(125)

(160)

(100)

典型 我

抄送

(ma)

50100

clock 频率(mhz)

l

o

w

p

o

w

e?

右

h

我

g

h

p

e?

右

f

o

右

m

一个

n

c

e?