ds027 (v3.1) july 5, 2000

www.xilinx.com

1

产品 规格

1-800-255-7778

© 2000 xilinx, 公司 所有 权利 保留. 所有 xilinx 商标, 注册 商标, patents, 和 免责声明 是 作 列表 一个t

http://www.xilinx.com/legal.htm

.

所有 其它 商标 和 注册 商标 是 这 恰当的ty 的 它们的 各自的 所有权人. 所有 规格 是 主题 至 change 没有 注意.

特性

• 一个-时间 可编程序的 (otp) 读-仅有的 记忆

设计 至 store 配置 bitstreams 的 xilinx

fpga 设备

• 简单的 接口 至 这 fpga; 需要 仅有的 一个 用户

i/o 管脚

• cascadable 为 storing 变长 或者 多样的 bitstreams

• 可编程序的 重置 极性 (起作用的 高 或者 起作用的

低) 为 兼容性 和 不同的 fpga 解决方案

• xc17128e/el, xc17256e/el, xc1701 和 xc1700l

序列 支持 快 配置

• 低-电源 cmos floating 门 处理

• xc1700e 序列 是 有 在 5v 和 3.3v 版本

• xc1700l 序列 是 有 在 3.3v 仅有的

• 有 在 紧凑的 塑料 包装: 8-管脚 soic,

8-管脚 voic, 8-管脚 pdip, 20-pin soic, 20-pin plcc,

44-管脚 plcc 或者 44-管脚 vqfp.

• 程序编制 支持 用 leading programmer

manufacturers.

• 设计 支持 使用 这 xilinx alliance 和

foundation 序列 软件 包装.

• 有保证的 20 年 生命 数据 保持

描述

这 xc1700 家族 的 配置 proms 提供 一个

容易-至-使用, 费用-有效的 方法 为 storing 大 xilinx

fpga 配置 bitstreams.

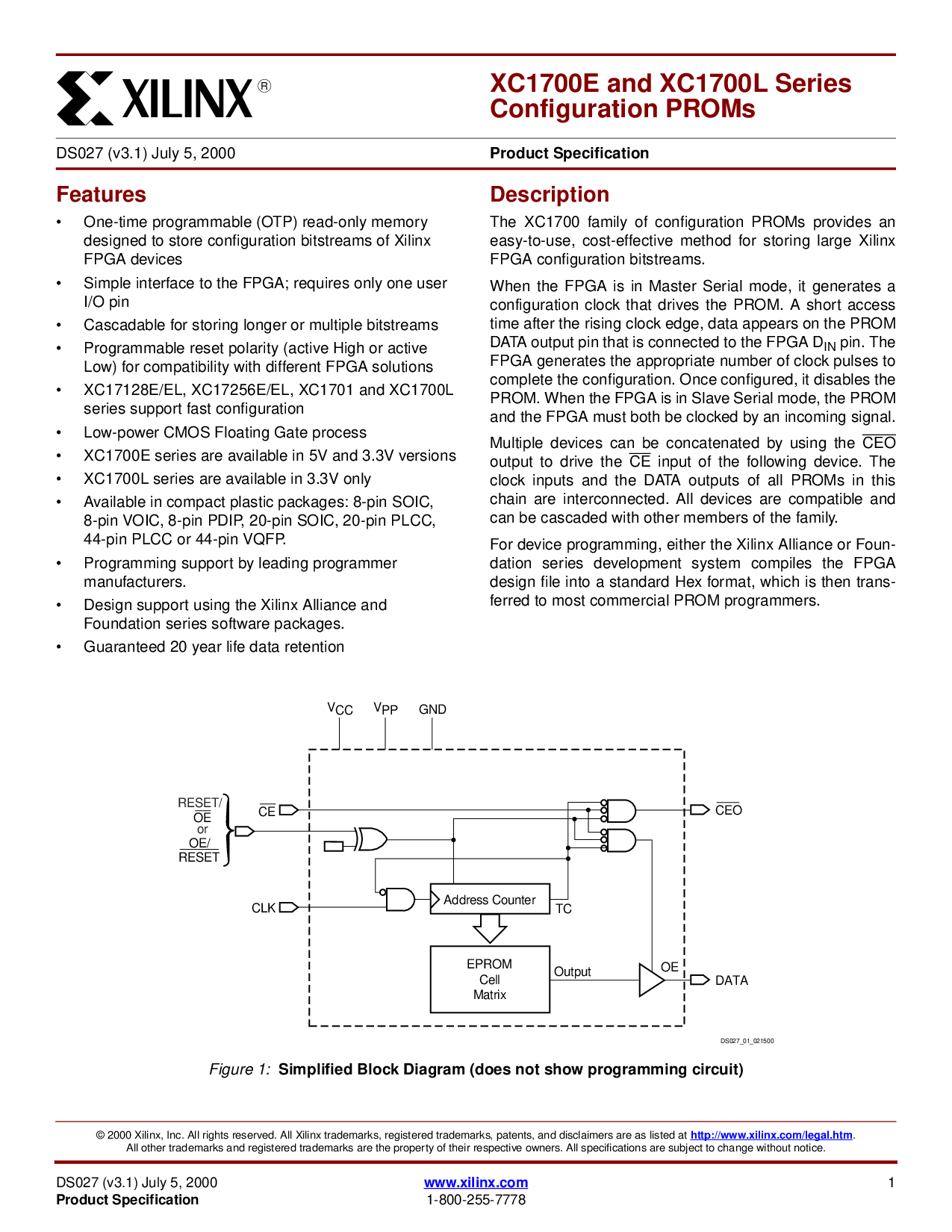

当 这 fpga 是 在 主控 串行 模式, 它 发生 一个

配置 时钟 那 驱动 这 prom. 一个 短的 进入

时间 之后 这 rising 时钟 边缘, 数据 呈现 在 这 prom

数据 输出 管脚 那 是 连接 至 这 fpga d

在

管脚. 这

fpga 发生 这 适合的 号码 的 时钟 脉冲 至

完全 这 配置. once 配置, 它 使不能运转 这

prom. 当 这 fpga 是 在 从动装置 串行 模式, 这 prom

和 这 fpga 必须 两个都 是 clocked 用 一个 新当选的 信号.

多样的 设备 能 是 concatenated 用 使用 这 ceo

输出 至 驱动 这 ce输入 的 这 下列的 设备. 这

时钟 输入 和 这 数据 输出 的 所有 proms 在 这个

chain 是 interconnected. 所有 设备 是 兼容 和

能 是 倾泻 和 其它 members 的 这 家族.

为 设备 程序编制, 也 这 xilinx alliance 或者 foun-

dation 序列 开发 系统 compiles 这 fpga

设计 文件 在 一个 标准 十六进制 format, 这个 是 然后 trans-

ferred 至 大多数 商业的 prom programmers.

0

xc1700e 和 xc1700l 序列

配置 proms

ds027 (v3.1) july 5, 2000

08

产品 规格

R

图示 1:

simplified 块 图解 (做 不 显示 程序编制 电路)

非易失存储器

Cell

矩阵变换

地址 计数器

CE

数据

OE

输出

CLK

V

CC

V

PP

地

ds027_01_021500

TC

OE

重置/

oe/

重置

或者

CEO