十一月 5, 1998 (版本 5.2) 7-83

7

特性

• 低-费用, 寄存器/获得 rich, sram 为基础

reprogrammable architecture

-0.5

µ

m 三-layer metal cmos 处理 技术

- 256 至 1936 逻辑 cells (3,000 至 23,000 “gates”)

- 价格 competitive 和 门 arrays

• 系统 水平的 特性

- 系统 效能 在之外 50 mhz

- 6 水平 的 interconnect hierarchy

- VersaRing

™

i/o 接口 为 管脚-locking

- 专心致志的 carry 逻辑 为 高-速 arithmetic

功能

- cascade chain 为 宽 输入 功能

- 建造-在 ieee 1149.1 jtag boundary scan 测试

电路系统 在 所有 i/o 管脚

- 内部的 3-状态 bussing 能力

- 四 专心致志的 低-skew 时钟 或者 信号 分发

nets

• 多功能的 i/o 和 包装

- 革新的 versaring

™

i/o 接口 提供 一个 高

逻辑 cell 至 i/o 比率, 和 向上 至 244 i/o 信号

- 可编程序的 输出 回转-比率 控制 maximizes

效能 和 减少 噪音

- 零 flip-flop 支撑 时间 为 输入 寄存器 使简化

系统 定时

- 独立 输出 使能 为 外部 bussing

- footprint 兼容性 在 一般 包装 在里面

这 xc5200 序列 和 和 这 xc4000 序列

- 在 150 设备/包装 结合体, 包含

先进的 bga, tq, 和 vq 包装 有

• 全部地 supported 用 xilinx 开发 系统

- 自动 放置 和 route 软件

- 宽 选择 的 pc 和 workstation platforms

- 在 100 3rd-群 alliance 接口

- supported 用 shrink-wrap foundation 软件

描述

这 xc5200 地方-可编程序的 门 排列 家族 是

engineered 至 deliver 低 费用. building 在 experiences

gained 和 三 previous successful sram fpga fami-

lies, 这 xc5200 家族 brings 一个 强健的 特性 设置 至 pro-

grammable 逻辑 设计. 这 versablock

™

逻辑 单元,

这 versaring i/o 接口, 和 一个 rich hierarchy 的 inter-

连接 resources 联合的 至 增强 设计 flexibility

和 减少 时间-至-market. 完全 支持 为 这

xc5200 家族 是 delivered 通过 这 familiar xilinx 软-

ware 环境. 这 xc5200 家族 是 全部地 supported 在

popular workstation 和 pc platforms. popular 设计

entry 方法 是 全部地 supported, 包含 abel, sche-

matic 俘获, vhdl, 和 verilog hdl 综合. 设计-

ers utilizing 逻辑 综合 能 使用 它们的 存在 tools 至

设计 和 这 xc5200 设备.

.

0

xc5200 序列

地方 可编程序的 门 arrays

十一月 5, 1998 (版本 5.2)

07*

产品 规格

R

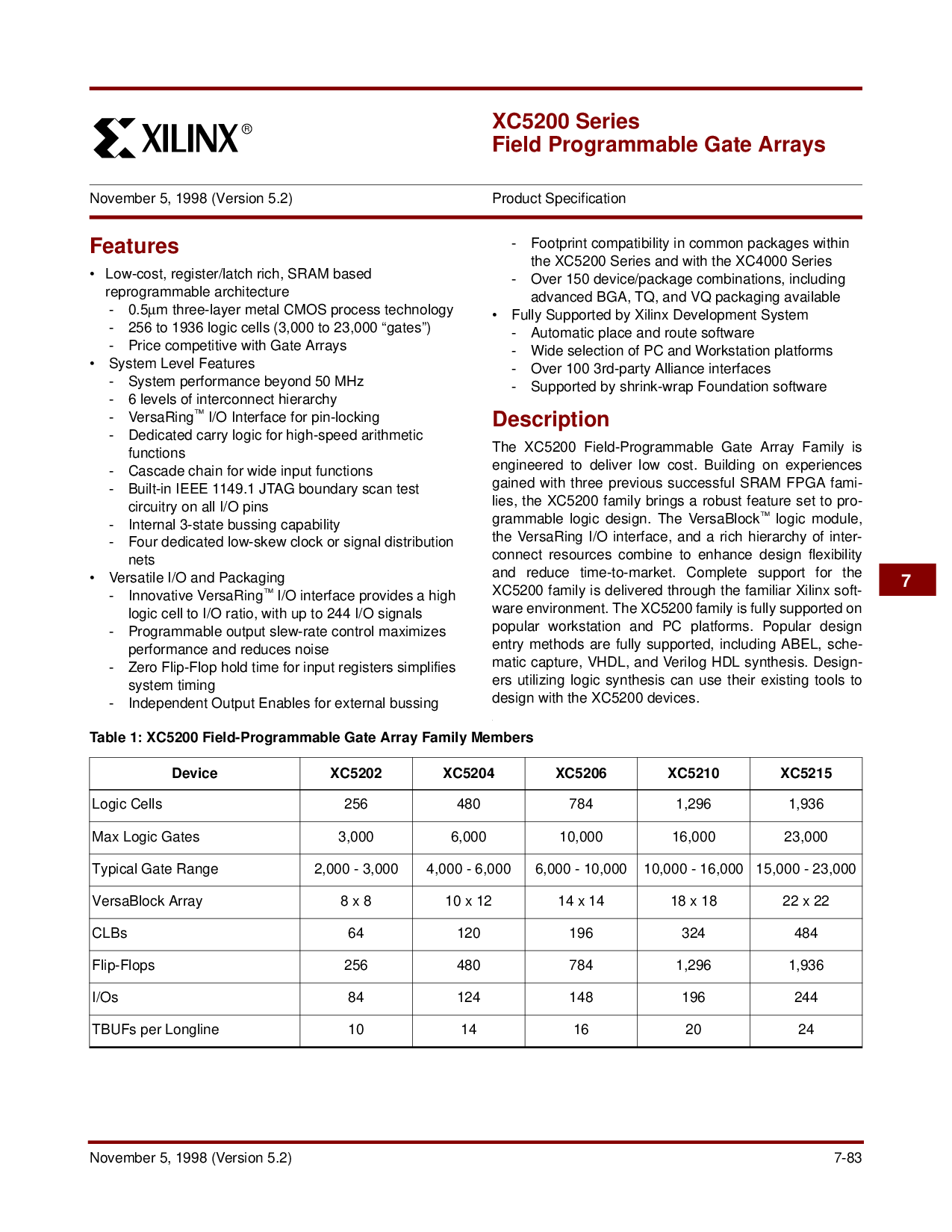

表格 1: xc5200 地方-可编程序的 门 排列 家族 members

设备 XC5202 XC5204 XC5206 XC5210 XC5215

逻辑 cells 256 480 784 1,296 1,936

最大值 逻辑 门 3,000 6,000 10,000 16,000 23,000

典型 门 范围 2,000 - 3,000 4,000 - 6,000 6,000 - 10,000 10,000 - 16,000 15,000 - 23,000

versablock 排列 8 x 8 10 x 12 14 x 14 18 x 18 22 x 22

CLBs 64 120 196 324 484

flip-flops 256 480 784 1,296 1,936

i/os 84 124 148 196 244

tbufs 每 longline 1014162024