5mhz spi 串行 e

2

prom 和 块 锁

TM

保护

128K

16k x 8 位

Ó

xicor, 公司 1998 专利权 pending 1 特性 主题 至 改变 没有 注意

7056–1.5 8/13/98 t2/c0/d1 ew

X25138

特性

•

5mhz 时钟 比率

•

低 电源 cmos

<1

m

一个 备用物品 电流

<5ma 起作用的 电流

•

2.5v 至 5.5v 电源 供应

•

spi 模式 (0,0 &放大; 1,1)

•

16k x 8 位

32 字节 页 模式

•

块 lock™ 保护

保护 1/4, 1/2 或者 所有 的 e

2

prom 排列

•

可编程序的 硬件 写 保护

在-电路 可编程序的 只读存储器 模式

•

建造-在 inadvertent 写 保护

电源-向上/向下 保护 电路系统

写 使能 获得

写 保护 管脚

•

自-安排时间 写循环

5ms 写 循环 时间 (典型)

•

高 可靠性

忍耐力: 100,000 循环

数据 保持: 100 年

静电释放 保护: 2000v 在 所有 管脚

•

包装

8-含铅的 xbga

8, 14-含铅的 soic

8-含铅的 pdip

8-含铅的 tssop

描述

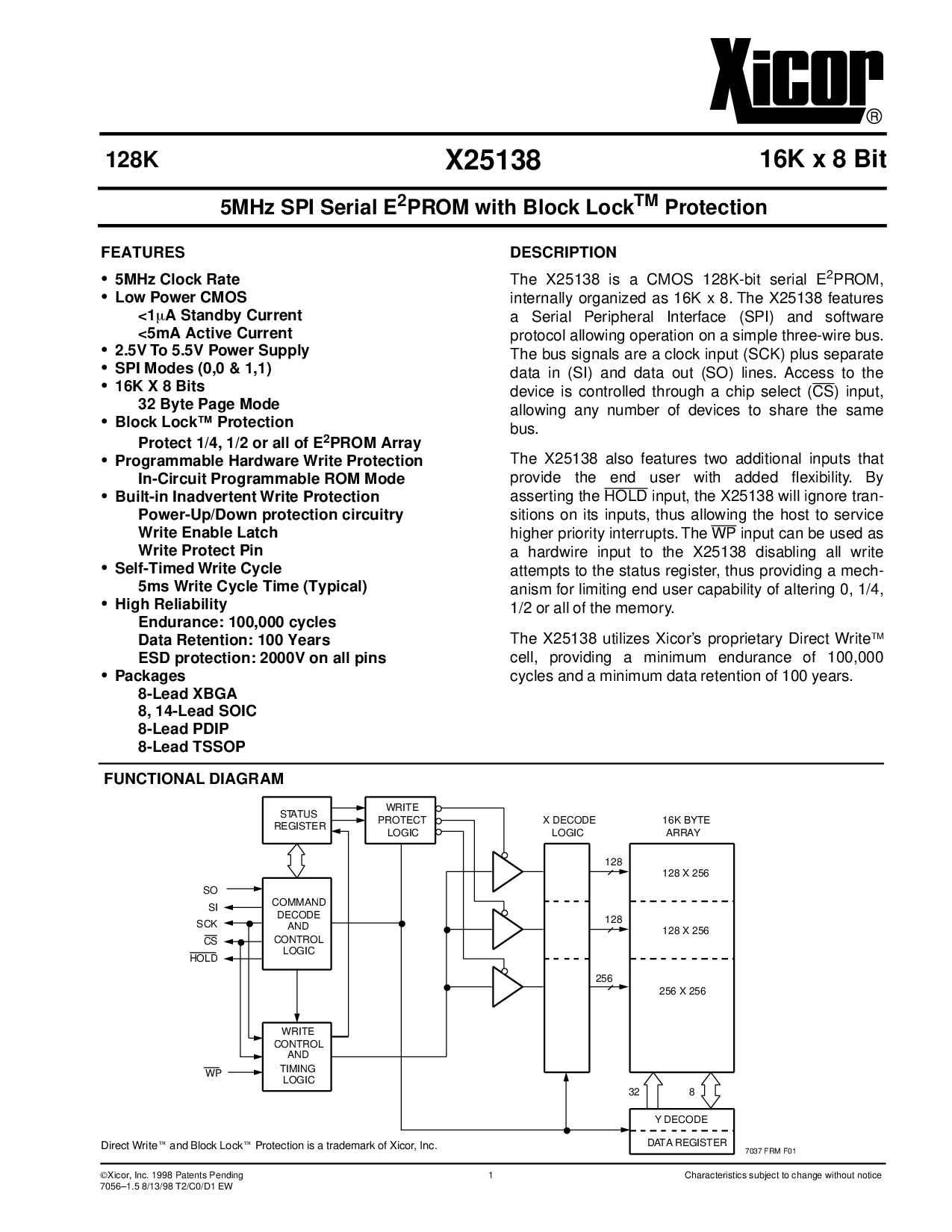

这 x25138 是 一个 cmos 128k-位 串行 e

2

prom,

内部 有组织的 作 16k x 8. 这 x25138 特性

一个 串行 附带的 接口 (spi) 和 软件

协议 准许 运作 在 一个 简单的 三-线 总线.

这 总线 信号 是 一个 时钟 输入 (sck) 加 独立的

数据 在 (si) 和 数据 输出 (所以) 线条. 进入 至 这

设备 是 控制 通过 一个 碎片 选择 (cs) 输入,

准许 任何 号码 的 设备 至 share 这 一样

总线.

这 x25138 也 特性 二 额外的 输入 那

提供 这 终止 用户 和 增加 flexibility. 用

asserting 这 支撑

输入, 这 x25138 将 ignore tran-

sitions 在 它的 输入, 因此 准许 这 host 至 维护

高等级的 priority 中断. 这 wp 输入 能 是 使用 作

一个 hardwire 输入 至 这 x25138 disabling 所有 写

attempts 至 这 状态 寄存器, 因此 供应 一个 mech-

anism 为 限制的 终止 用户 能力 的 altering 0, 1/4,

1/2 或者 所有 的 这 记忆.

这 x25138 运用 xicor’s 专卖的 直接 写

TM

cell, 供应 一个 最小 忍耐力 的 100,000

循环 和 一个 最小 数据 保持 的 100 年.

COMMAND

DECODE

和

控制

逻辑

写

控制

和

定时

逻辑

写

保护

逻辑

x decode

逻辑

16k 字节

排列

128 x 256

y decode

数据 寄存器

所以

SI

SCK

CS

支撑

WP

128

256

832

状态

寄存器

128

256 x 256

128 x 256

7037 frm f01

直接 写

Ô

和 块 锁

Ô

保护 是 一个 商标 的 xicor, 公司

函数的 图解