tlv2544, tlv2548

2.7 v 至 5.5 v, 12-有点, 200 ksps, 4/8 channel, 低 power,

串行 模数转换 转换器 与 自动 电源 向下

slas198a –february 1999– 修订 8月 1999

1

post 办公室 框 655303

•

达拉斯市, 德州 75265

d

最大值 吞吐量 200 ksps

d

内置 参考, 换算 时钟 和

8

×

先进先出

d

差速器/积分 非线性 错误:

±

1 lsb

d

信噪比 和 失真 比率:

69 db, f

我

= 12 khz

d

杂散 免费 动态 范围: 75 db,

f

我

= 12 khz

d

spi/dsp-兼容 串行 接口 与

sclk 向上 至 20 mhz

d

单独 宽 范围 供应 2.7 vdc 至

5.5 vdc

d

模拟 输入 范围 0 v 至 供应 电压

与 500 khz bw

d

硬件 受控 和 可编程

取样 期间

d

低 操作 电流 (1 ma 在 2.7 v,

1.2 ma 在 5.5 v 外部 参考,

1.6 ma 在 2.7 v,

2.1 ma 在 5.5 v, 内部 参考)

d

电源 向下: 软件/硬件

掉电 模式 (1

µ

一个 最大值, 分机 参考),

自动 掉电 模式 (1

µ

一个, 分机 参考)

d

可编程 自动-频道 扫掠

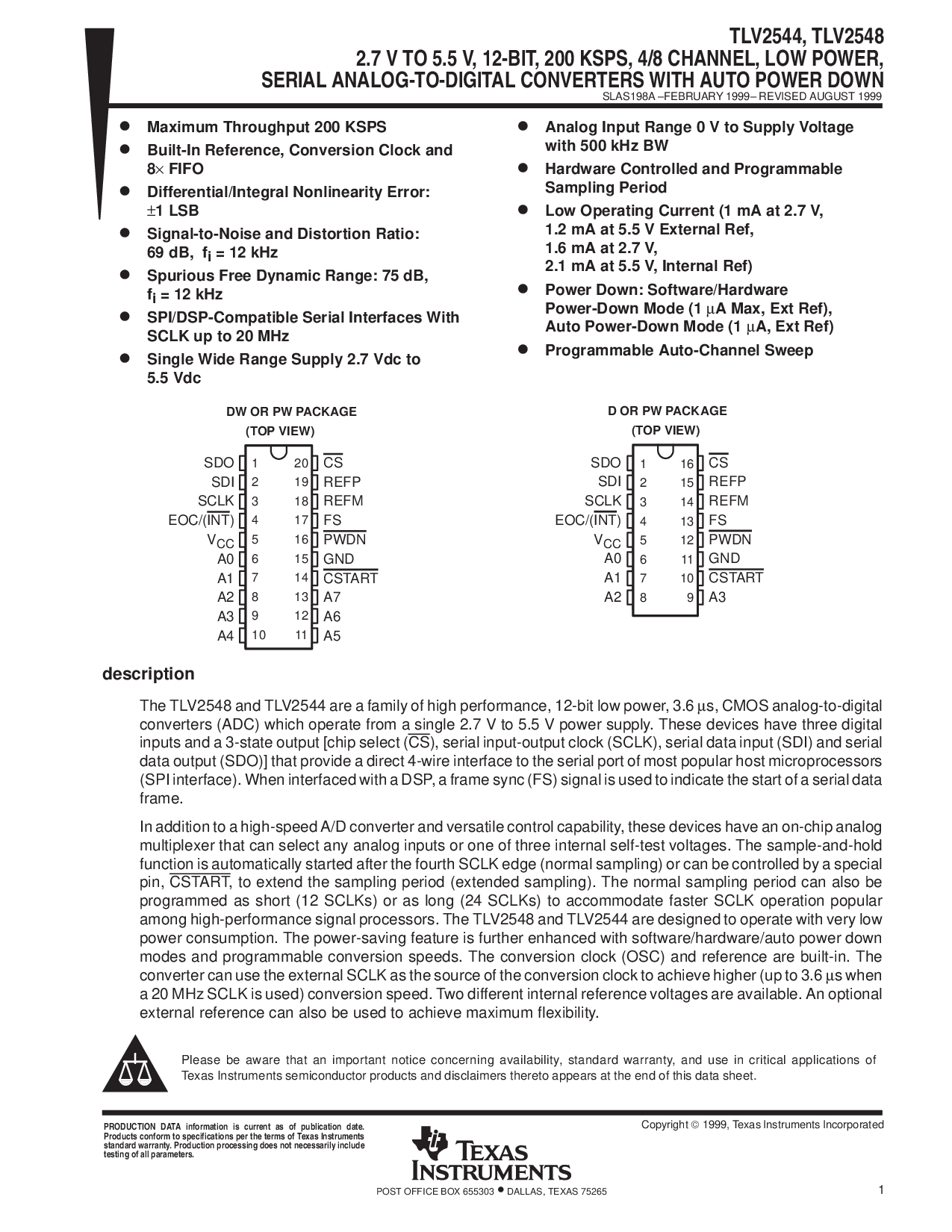

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

SDO

SDI

SCLK

eoc/(智力

)

v

抄送

A0

A1

A2

A3

A4

cs

REFP

REFM

fs

PWDN

地

CSTART

A7

A6

A5

dw 或 pw 包装

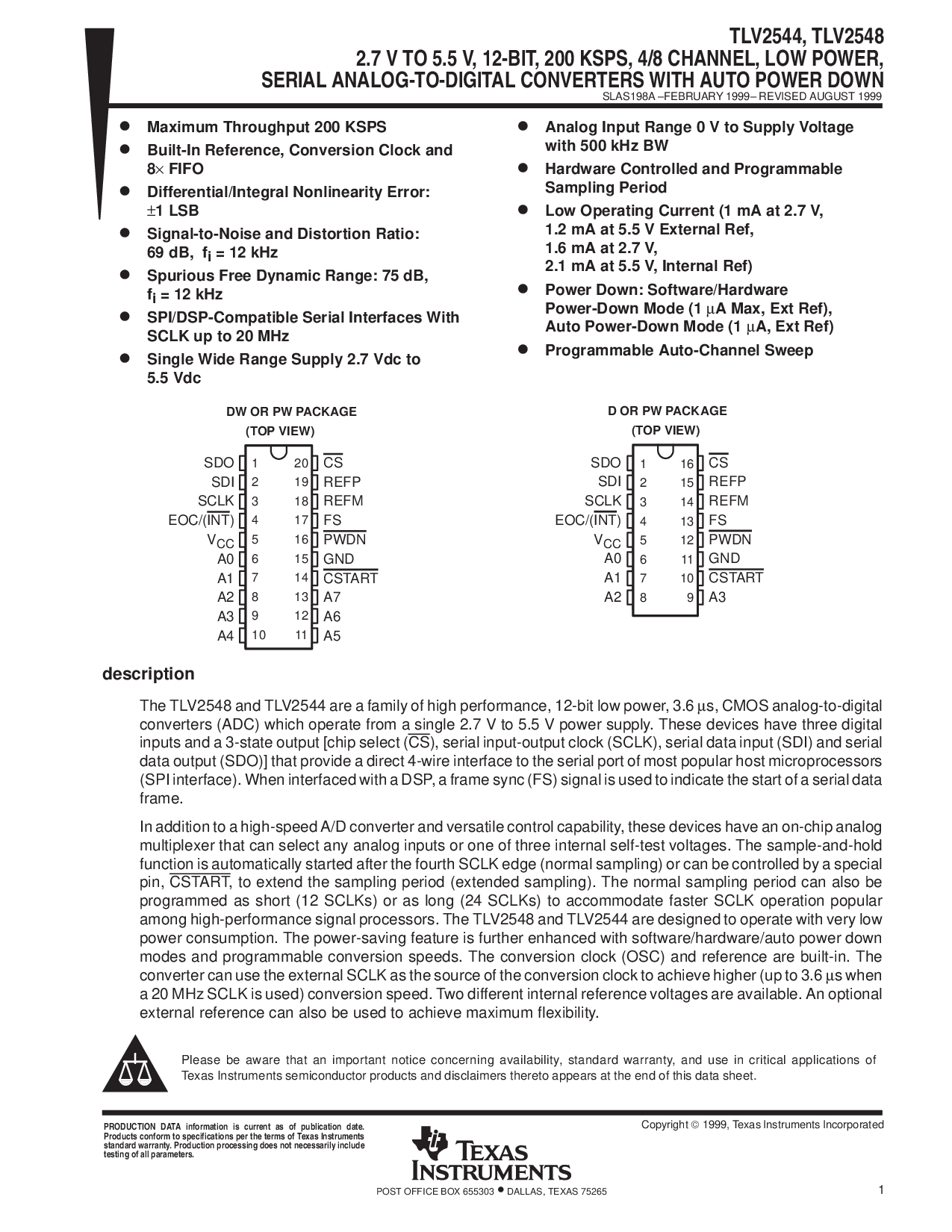

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

SDO

SDI

SCLK

eoc/(智力

)

v

抄送

A0

A1

A2

cs

REFP

REFM

fs

PWDN

地

CSTART

A3

d 或 pw 包装

(顶部 查看)

(顶部 查看)

描述

这 tlv2548 和 tlv2544 是 一个 家庭 的 高 业绩, 12-有点 低 电源, 3.6

µ

s, cmos 模数转换

转换器 (adc) 哪个 操作 从 一个 单独 2.7 v 至 5.5 v 电源 供应. 这些 设备 有 三个 数字

输入 和 一个 3-州 输出 [chip 选择 (cs), 串行 输入-输出 时钟 (sclk), 串行 数据 输入 (sdi) 和 串行

数据 输出 (sdo)] 那 提供 一个 直接 4-电线 接口 至 这 串行 港口 的 大多数 受欢迎 主机 微处理器

(spi 接口). 当 接口 与 一个 dsp, 一个 框架 同步 (fs) 信号 是 已使用 至 指示 这 开始 的 一个 串行 数据

框架.

入点 加法 至 一个 高速 一个/d 变频器 和 多才多艺 控制 能力, 这些 设备 有 一个 片上 模拟

多路复用器 那 可以 选择 任何 模拟 输入 或 一个 的 三个 内部 自我测试一下 电压. 这 采样和保持

功能 是 自动 已开始 之后 这 第四 sclk 边缘 (正常 取样) 或 可以 是 受控 由 一个 特殊

管脚, cstart

, 至 扩展 这 取样 期间 (扩展 取样). 这 正常 取样 期间 可以 也 是

编程 作为 短 (12 sclks) 或 作为 长 (24 sclks) 至 容纳 更快 sclk 操作 受欢迎

在 高性能 信号 处理器. 这 tlv2548 和 tlv2544 是 设计 至 操作 与 很 低

电源 消费. 这 省电 功能 是 进一步 增强型 与 软件/硬件/自动 电源 向下

模式 和 可编程 换算 速度. 这 换算 时钟 (osc) 和 参考 是 已建成-入点. 这

变频器 可以 使用 这 外部 sclk 作为 这 来源 的 这 换算 时钟 至 实现 较高 (向上 至 3.6

µ

s 当

一个 20 mhz sclk 是 已使用) 换算 速度. 两个 不同的 内部 参考 电压 是 可用. 一个 可选

外部 参考 可以 也 是 已使用 至 实现 最大值 灵活性.

版权

1999, 德州 仪器仪表 股份公司

生产 数据 信息 是 电流 作为 的 出版物 日期.

产品 符合 至 规格 按 这 条款 的 德州 仪器仪表

标准 保修. 生产 加工 是否 不 必然 包括

测试 的 全部 参数.

请 是 意识到 那 一个 重要 通知 关于 可用性, 标准 保修, 和 使用 入点 关键 应用程序 的

德州 仪器仪表 半导体 产品 和 免责声明 对此 出现 在 这 结束 的 这个 数据 工作表.