这 ics627-01 是 一个 低 费用, 低 jitter, 高

效能 时钟 synthesizer 这个 能 发生

发生率 必需的 为 hdtv 接受者 和 设置-

顶 boxes. 使用 ics’s 专利的 相似物/数字的

阶段-锁 循环 (pll) 技巧, 这 设备

使用 一个 inexpensive 基本的 27 mhz 结晶

输入 至 生产 低 jitter hdtv pixel clocks. 它

有 一个 独立的 输入 为 一个 1001/1000 或者

2(1001/1000) 转换 从 一个 13.5 mhz,

27 mhz 或者 54 mhz 在

放.

ics627-01

hdtv 设置-顶 时钟 源

mds 627-01 b

1

修订 051600

整体的 电路 系统, 公司 • 525 race 街道 • san jose •ca•95126•(408) 295-9800tel • www.icst.com

初步的 信息

描述

特性

• packaged 在 28 管脚 ssop (qsop)

• hdtv 发生率 的 74.25 和 74.175824 mhz

• 提供 可选择的 b 时钟 为 27.027 mhz 或者

其它 1001/1000

• 使用 一个 基本的 27 mhz 结晶 或者 时钟 输入

• 所有 发生率 是 发生 exactly (零 ppm

综合 错误)

• 全部 cmos 输出 swings 和 12 毫安 输出

驱动 能力 在 ttl 水平

• 先进的, 低 电源, sub-micron cmos 处理

• 3.3 v ±5% 运行 供应

REFOUT

(27 mhz)

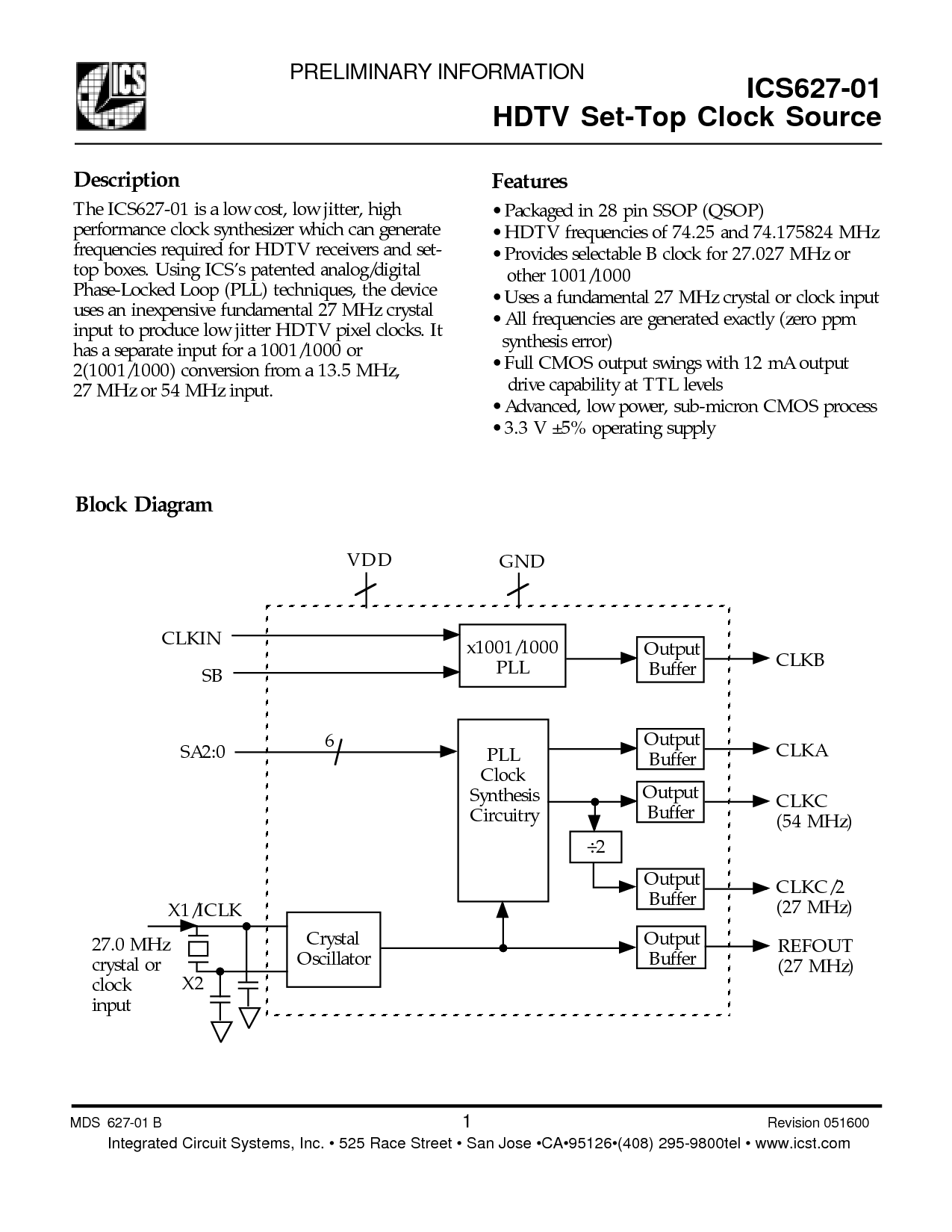

块 图解

结晶

振荡器

PLL

时钟

综合

电路系统

输出

缓存区

CLKC

(54 mhz)

27.0 mhz

结晶 或者

时钟

输入

x1/iclk

X2

clkc/2

(27 mhz)

÷2

CLKA

CLKB

SB

sa2:0

6

输出

缓存区

输出

缓存区

输出

缓存区

输出

缓存区

CLKIN

VDD

地

x1001/1000

PLL