© 2000 仙童 半导体 公司 DS500098 www.fairchildsemi.com

二月 1998

修订 july 2000

74vhc161284 ieee 1284 transceiver

74VHC161284

ieee 1284 transceiver

一般 描述

这 vhc161284 包含 第八 双向的 数据 缓存区

和 eleven 控制/状态 缓存区 至 执行 一个 全部

IEEE 1284 一致的 接口. 这 设备 支持 这

IEEE 1284 标准 和 是 将 至 是 使用 在

扩展 能力 端口 模式 (ecp). 这 引脚 准许

为 容易 连接 从 这 附带的 (一个-一侧) 至 这

host (缆索 一侧).

输出 在 这 缆索 一侧 能 是 配置 至 是 也

打开 流 或者 高 驱动 (

±

14 毫安). 这 拉-向上 和 拉-

向下 序列 末端 阻抗 的 这些 输出 在 这

缆索 一侧 是 优化 至 驱动 一个 外部 缆索. 在 addi-

tion, 所有 输入 (除了 hlh) 和 输出 在 这 缆索 一侧

包含 内部的 拉-向上 电阻器 连接 至 这 v

CC

sup-

ply 至 提供 恰当的 末端 和 拉-ups 为 打开

流 模式.

输出 在 这 附带的 一侧 是 标准 低-驱动

cmos 输出. 这 dir 输入 控制 数据 流动 在 这

一个

1

–A

8

/b

1

–B

8

transceiver 管脚.

特性

■

支持 ieee 1284 水平的 1 和 水平的 2 signaling

standards 为 双向的 并行的 communications

在 个人的 计算机 和 printing peripherals

■

替代 这 函数 的 二 (2) 74act1284 设备

■

所有 输入 有 hysteresis 至 提供 噪音 余裕

■

b 和 y 输出 阻抗 优化 至 驱动 外部

缆索

■

b 和 y 输出 在 高 阻抗 模式 在 电源

向下

■

输入 和 输出 在 缆索 一侧 有 内部的 拉-向上

电阻器

■

流动-通过 管脚 配置 准许 容易 接口

在 这 附带的 和 host

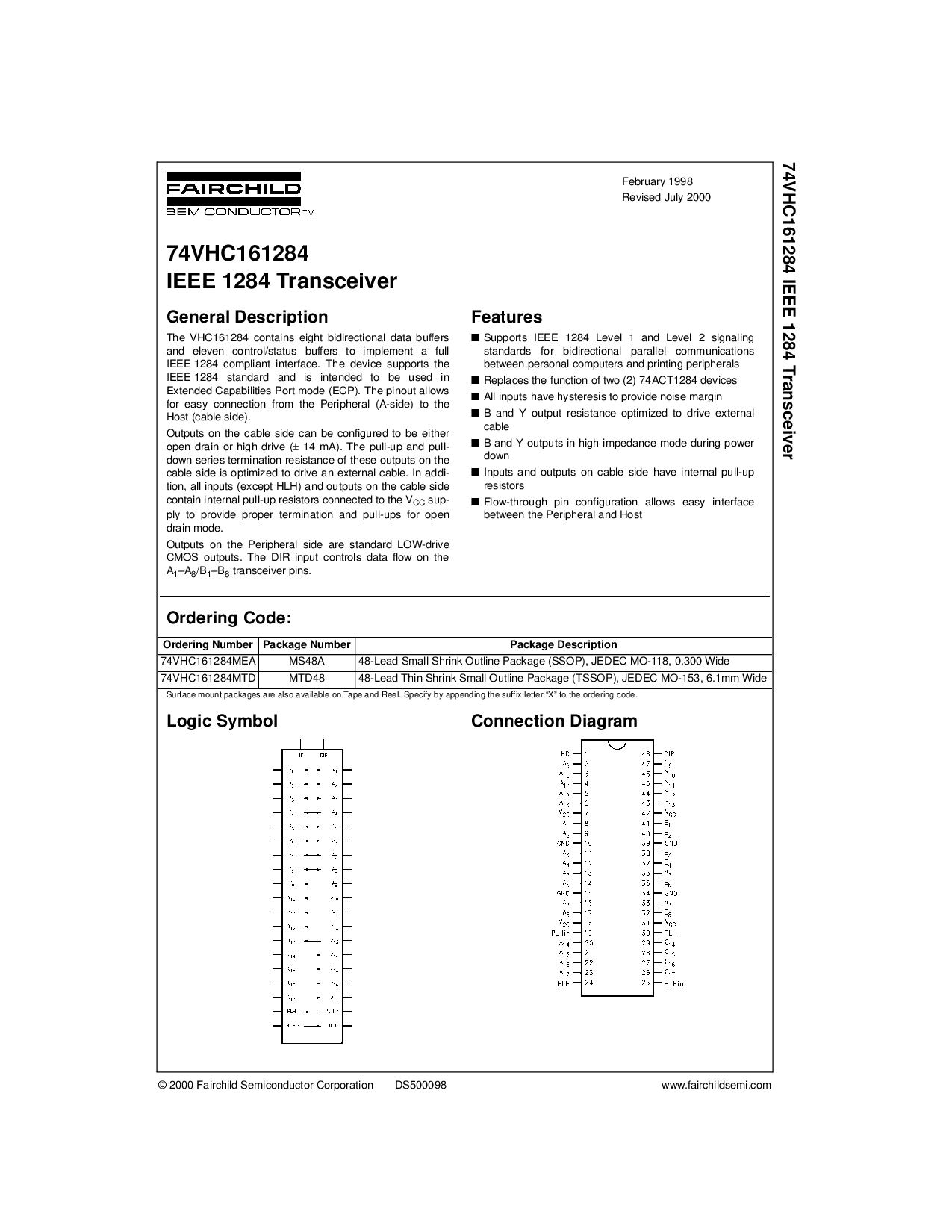

订货 代号:

表面 挂载 包装 是 也 有 在 录音带 和 卷轴. 具体说明 用 appending 这 后缀 letter

“

X

”

至 这 订货 代号.

逻辑 标识 连接 图解

订货 号码 包装 号码 包装 描述

74VHC161284MEA MS48A 48-含铅的 小 shrink 外形 包装 (ssop), 电子元件工业联合会 mo-118, 0.300 宽

74VHC161284MTD MTD48 48-含铅的 薄的 shrink 小 外形 包装 (tssop), 电子元件工业联合会 mo-153, 6.1mm 宽