7-80

提醒: 这些 设备 是 敏感的 至 静电的 释放; follow 恰当的 ic 处理 程序.

1-888-intersil 或者 321-724-7143 | 版权 © intersil 公司 1999

cd4014bms,

CD4021BMS

cmos 8-平台 静态的 变换 寄存器

描述

cd4014bms -同步的 并行的 或者 串行 输入/串行 输出

cd4021bms -异步的 并行的 输入 或者 同步的

串行 输入/串行 输出

cd4014bms 和 cd4021bms 序列 类型 是 8-平台 paral-

lel- 或者 串行-输入/串行 输出 寄存器 having 一般 时钟

和 并行的/串行 控制 输入, 一个 单独的 串行

数据 输入, 和 单独的 并行的 “jam” 输入 至 各自 寄存器

平台. 各自 寄存器 平台 是 一个 d-类型, 主控-从动装置 flip-flop. 在

增加 至 一个 输出 从 平台 8, “q” 输出 是 也 有

从 stages 6 和 7. 并行的 作 好 作 串行 entry 是 制造 在

这 寄存器 synchronously 和 这 积极的 时钟 线条 转变 在

这 cd4014bms. 在 这 cd4021bms 串行 entry 是 synchro-

nous 和 这 时钟 但是 并行的 entry 是 异步的. 在 两个都

类型, entry 是 控制 用 这 并行的/串行 控制

输入. 当 这 并行的/串行 控制 输入 是 低,

数据 是 serially shifted 在 这 8-平台 寄存器 synchronously

和 这 积极的 转变 的 这 时钟 线条. 当 这 并行的/

串行 控制 输入 是 高, 数据 是 jammed 在 这 8-

平台 寄存器 通过 这 并行的 输入 线条 和 同步的 和

这 积极的 转变 的 这 时钟 线条. 在 这 cd4021bms, 这

时钟 输入 的 这 内部的 平台 是 “forced” 当 asynchro-

nous 并行的 entry 是 制造. 寄存器 expansion 使用 多样的

包装 是 permitted.

这 cd4014bms 和 cd4021bms 是 有提供的 在 这些 16

含铅的 外形 包装:

braze seal 插件 H4T

frit seal 插件 H1F

陶瓷的 flatpack H6W

特性

• 高 电压 类型 (20v 比率)

• 中等 速 运作 12mhz (典型值.) 时钟 比率 在

vdd-vss = 10v

• 全部地 静态的 运作

• 8 主控-从动装置 flip-flops 加 输出 buffering 和

控制 gating

• 100% 测试 为 安静的 电流 在 20v

• 最大 输入 电流 的 1

µ

一个 在 18v 在 全部 包装-

age 温度 范围; 100na 在 18v 和 +25

o

C

• 噪音 余裕 (全部 包装 温度 范围)

• 1v 在 vdd = 5v

• 2v 在 vdd = 10v

• 2.5v 在 vdd = 15v

• standardized 对称的 输出 特性

• 5v, 10v 和 15v 参数 比率

• 满足 所有 (所需的)东西 的 电子元件工业联合会 tentative 标准

非. 13b, “standard specifications 为 描述 的

`b' 序列 cmos 设备

产品:

• 并行的 输入/串行 输出 数据 queueing

• 并行的 至 串行 数据 转换

• 一般 目的 寄存器

文件 号码

3294

12月 1992

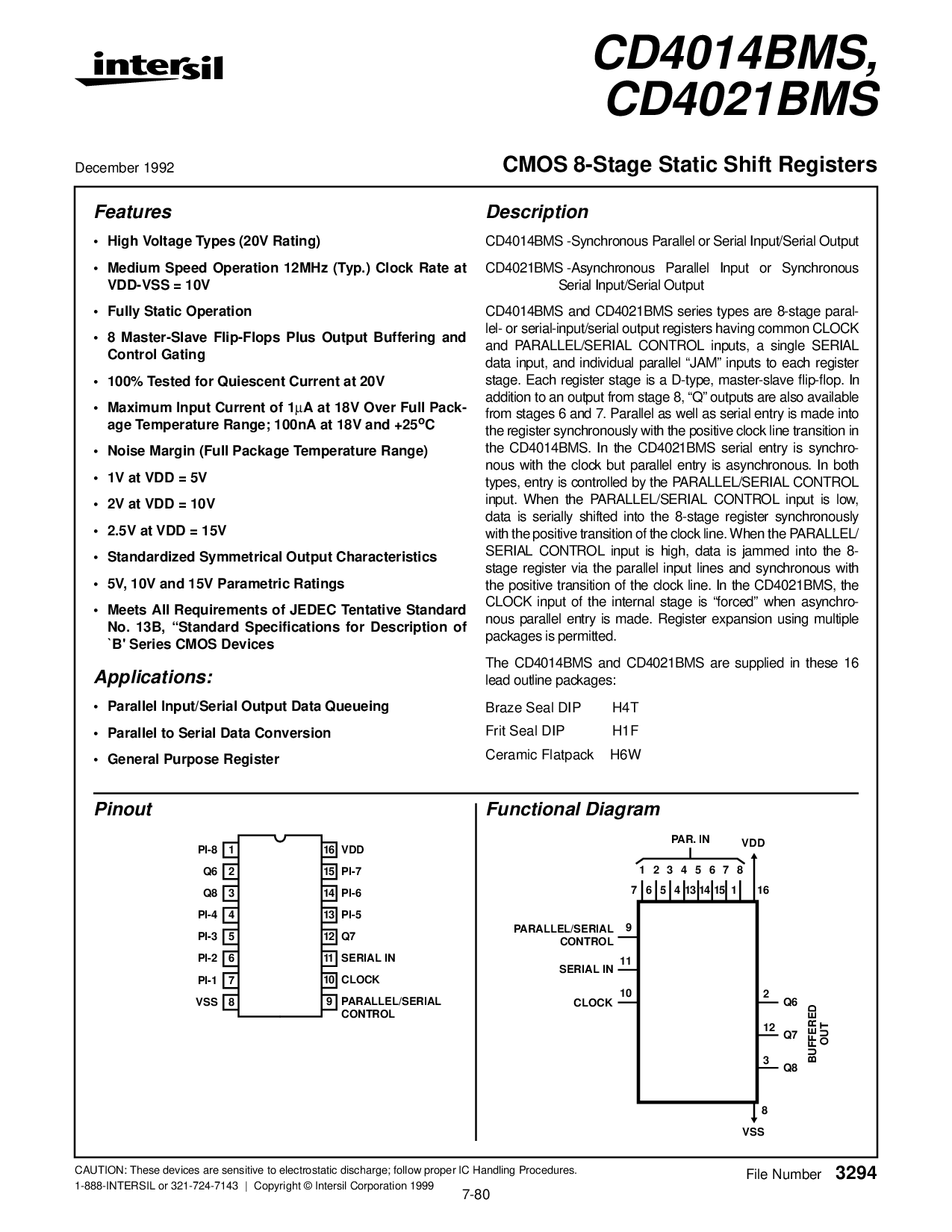

函数的 图解

14 1513 1456716

12345678

VDD

par. 在

VSS

12

3

2

11

10

9

Q6

Q7

Q8

并行的/串行

控制

串行 在

时钟

缓冲

输出

8

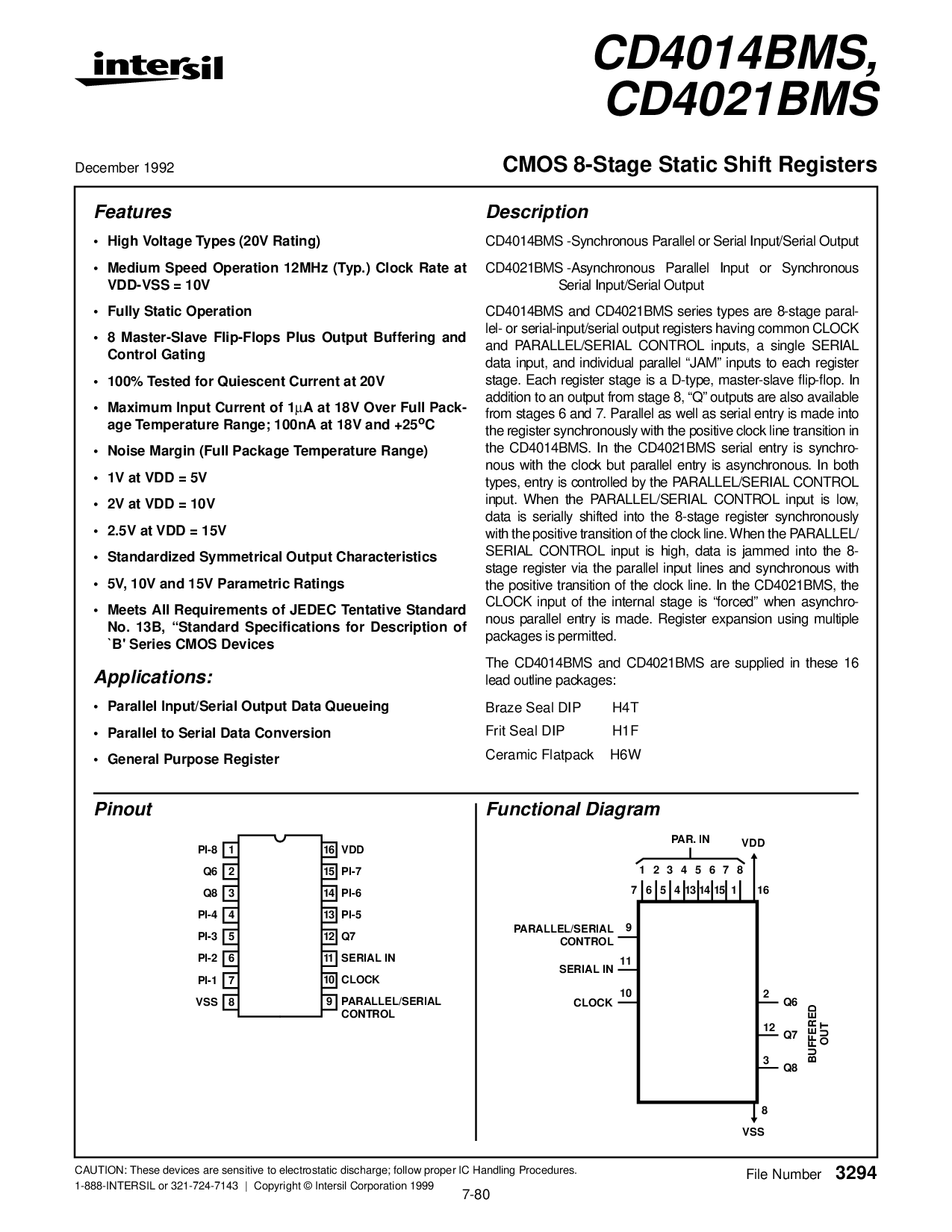

引脚

14

15

16

9

13

12

11

10

1

2

3

4

5

7

6

8

pi-8

Q6

Q8

pi-4

pi-3

pi-2

VSS

pi-1

VDD

pi-6

pi-5

Q7

串行 在

时钟

并行的/串行

pi-7

控制