7-780

提醒: 这些 设备 是 敏感的 至 静电的 释放; follow 恰当的 ic 处理 程序.

1-888-intersil 或者 321-724-7143 | 版权 © intersil 公司 1999

CD4027BMS

cmos 双 j-k

主控-从动装置 flip-flop

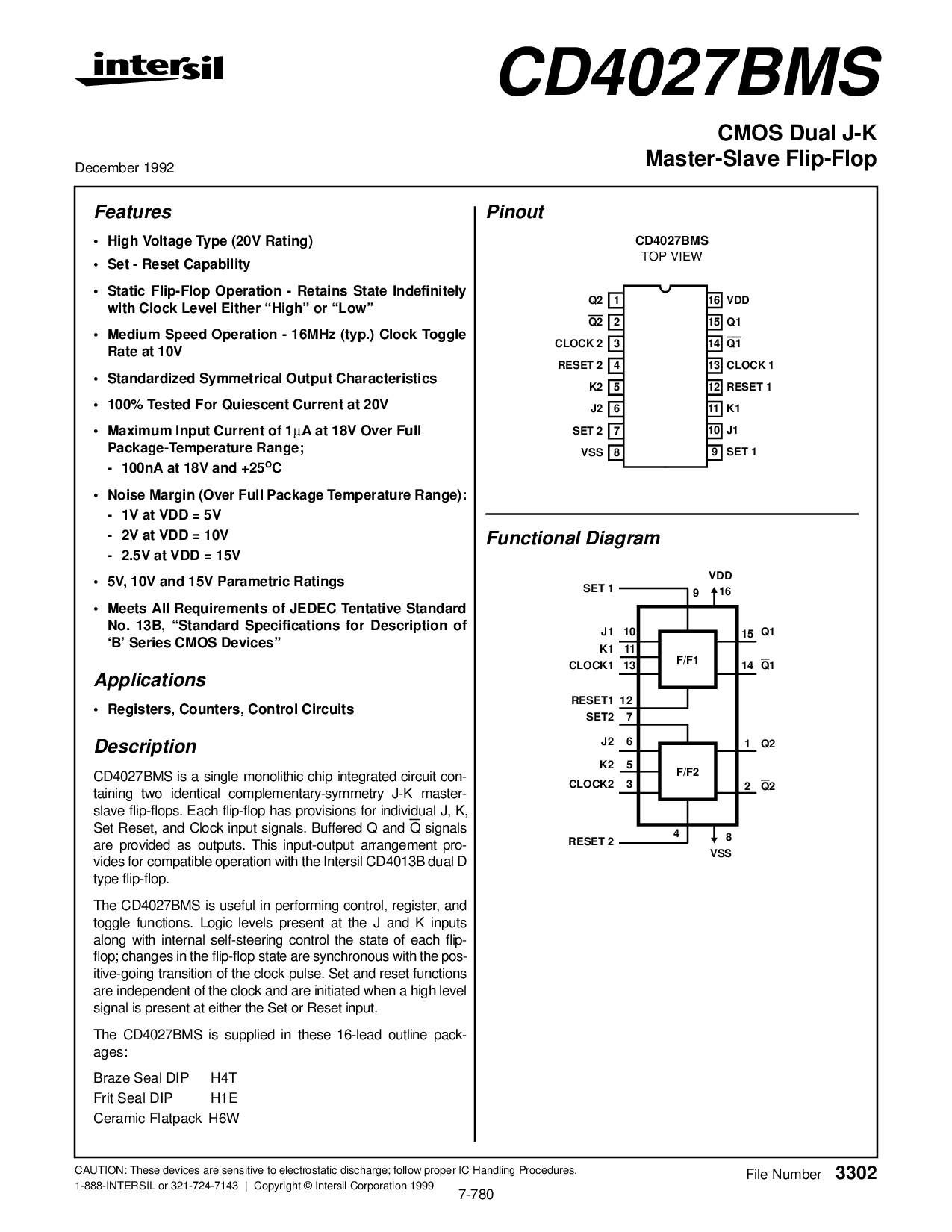

引脚

CD4027BMS

顶 视图

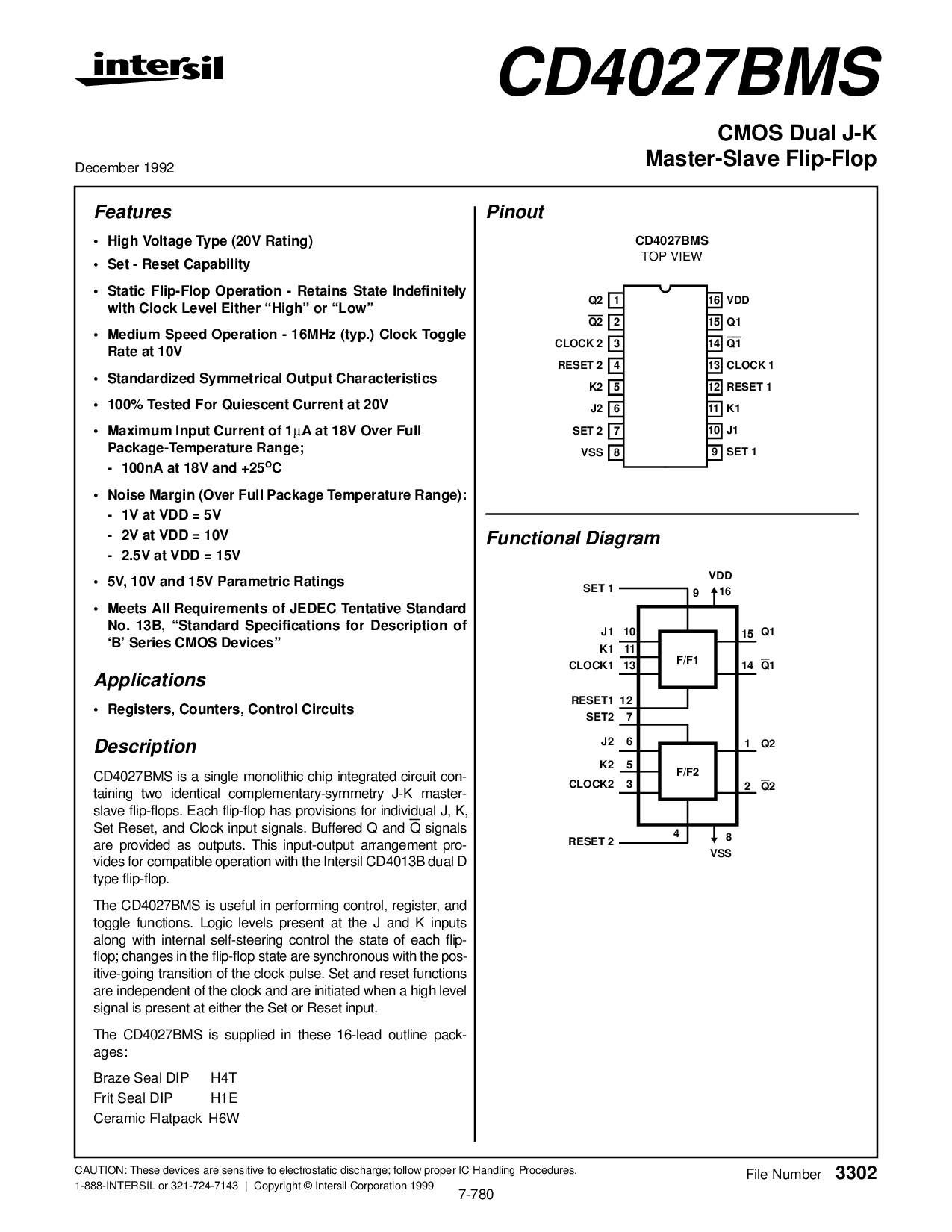

函数的 图解

14

15

16

9

13

12

11

10

1

2

3

4

5

7

6

8

Q2

Q2

时钟 2

重置 2

K2

J2

VSS

设置 2

VDD

Q1

时钟 1

重置 1

K1

J1

设置 1

Q1

VSS

VDD

16

8

重置 2

Q1

RESET1

SET2

Q2

5

Q2

10

11

13

12

7

1

K2

2

Q1

设置 1

9

4

15

14

6

3

J2

CLOCK2

J1

K1

CLOCK1

f/f1

f/f2

特性

• 高 电压 类型 (20v 比率)

• 设置 - 重置 能力

• 静态的 flip-flop 运作 - retains 状态 indefinitely

和 时钟 水平的 也 “high” 或者 “low”

• 中等 速 运作 - 16mhz (典型值.) 时钟 toggle

比率 在 10v

• standardized 对称的 输出 特性

• 100% 测试 为 安静的 电流 在 20v

• 最大 输入 电流 的 1

µ

一个 在 18v 在 全部

包装-温度 范围;

- 100na 在 18v 和 +25

o

C

• 噪音 余裕 (在 全部 包装 温度 范围):

- 1v 在 vdd = 5v

- 2v 在 vdd = 10v

- 2.5v 在 vdd = 15v

• 5v, 10v 和 15v 参数 比率

• 满足 所有 (所需的)东西 的 电子元件工业联合会 tentative 标准

非. 13b, “standard specifications 为 描述 的

‘b’ 序列 cmos devices”

产品

• 寄存器, counters, 控制 电路

描述

cd4027bms 是 一个 单独的 大而单一的 碎片 整体的 电路 con-

taining 二 完全同样的 complementary-对称 j-k 主控-

从动装置 flip-flops. 各自 flip-flop 有 provisions 为 单独的 j, k,

设置 重置, 和 时钟 输入 信号. 缓冲 q 和

q 信号

是 提供 作 输出. 这个 输入-输出 arrangement pro-

vides 为 兼容 运作 和 这 intersil cd4013b 双 d

类型 flip-flop.

这 cd4027bms 是 有用的 在 performing 控制, 寄存器, 和

toggle 功能. 逻辑 水平 呈现 在 这 j 和 k 输入

along 和 内部的 自-steering 控制 这 状态 的 各自 flip-

flop; 改变 在 这 flip-flop 状态 是 同步的 和 这 pos-

itive-going 转变 的 这 时钟 脉冲波. 设置 和 重置 功能

是 独立 的 这 时钟 和 是 initiated 当 一个 高 水平的

信号 是 呈现 在 也 这 设置 或者 重置 输入.

这 cd4027bms 是 有提供的 在 这些 16-含铅的 外形 包装-

ages:

braze seal 插件 H4T

frit seal 插件 H1E

陶瓷的 flatpack H6W

12月 1992

文件 号码

3302