ez-usb fx2lp™ usb 微控制器

cy7c68013a/cy7c68014a

cy7c68015a/cy7c68016a

Cypress 半导体 公司

• 3901 北 第一 街道 • San Jose

,

ca 95134 • 408-943-2600

文档 #: 38-08032 rev. *g 修订 二月 1, 2005

1.0 特性 (cy7c68013a/14a/15a/16a)

• usb 2.0–usb-如果 高 速 certified (tid # 40440111)

• 单独的-碎片 整体的 usb 2.0 transceiver, smart sie,

和 增强 8051 微处理器

• 合适, 表格 和 函数 兼容 和 这 fx2

— 管脚-兼容

— 物体-代号-兼容

— functionally-兼容 (fx2lp 是 一个 superset)

• 过激 低 电源: i

CC

非 更多 比 85 毫安 在 任何 模式

— 完美的 为 总线 和 电池 powered 产品

• 软件: 8051 代号 runs 从:

— 内部的 内存, 这个 是 下载 通过 usb

— 内部的 内存, 这个 是 承载 从 可擦可编程只读存储器

— 外部 记忆 设备 (128 管脚 包装)

• 16 kbytes 的 在-碎片 代号/数据 内存

• 四 可编程序的 大(量)/中断/isochro-

nous endpoints

— buffering 选项: 翻倍, triple, 和 四方形

• 额外的 可编程序的 (大(量)/中断) 64-字节

endpoint

• 8- 或者 16-位 外部 数据 接口

• smart 媒介 标准 ecc 一代

• gpif (一般 可编程序的 接口)

— 准许 直接 连接 至 大多数 并行的 接口

— 可编程序的 波形 descriptors 和 configu-

限定 寄存器 至 定义 波形

— 支持 多样的 准备好 (rdy) 输入 和 控制

(ctl) 输出

•

整体的, 工业-标准 增强 8051

— 48-mhz, 24-mhz, 或者 12-mhz cpu 运作

— 四 clocks 每 操作指南 循环

— 二 usarts

— 三 计数器/计时器

— expanded 中断 系统

— 二 数据 pointers

•

3.3v 运作 和 5v tolerant 输入

•

vectored usb 中断 和 gpif/先进先出 中断

•

独立的 数据 缓存区 为 这 设置-向上 和 数据 portions

的 一个 控制 转移

•

整体的 i

2

c 控制, runs 在 100 或者 400 khz

•

四 整体的 fifos

— 整体的 glue 逻辑 和 fifos 更小的 系统 费用

— 自动 转换 至 和 从 16-位 buses

— 主控 或者 从动装置 运作

— 使用 外部 时钟 或者 异步的 strobes

— 容易 接口 至 asic 和 dsp ics

1.1 特性 (cy7c68013a/14a 仅有的)

• cy7c68014a: 完美的 为 电池 powered 产品

— suspend 电流: 100

µ

一个 (典型值)

• cy7c68013a: 完美的 为 非-电池 powered applica-

tions

— suspend 电流: 300

µ

一个 (典型值)

• 有 在 四 含铅的-自由 包装 和 向上 至 40 gpios

— 128-管脚 tqfp (40 gpios), 100-管脚 tqfp (40 gpios),

56-管脚 qfn (24 gpios) 和 56-管脚 ssop (24 gpios)

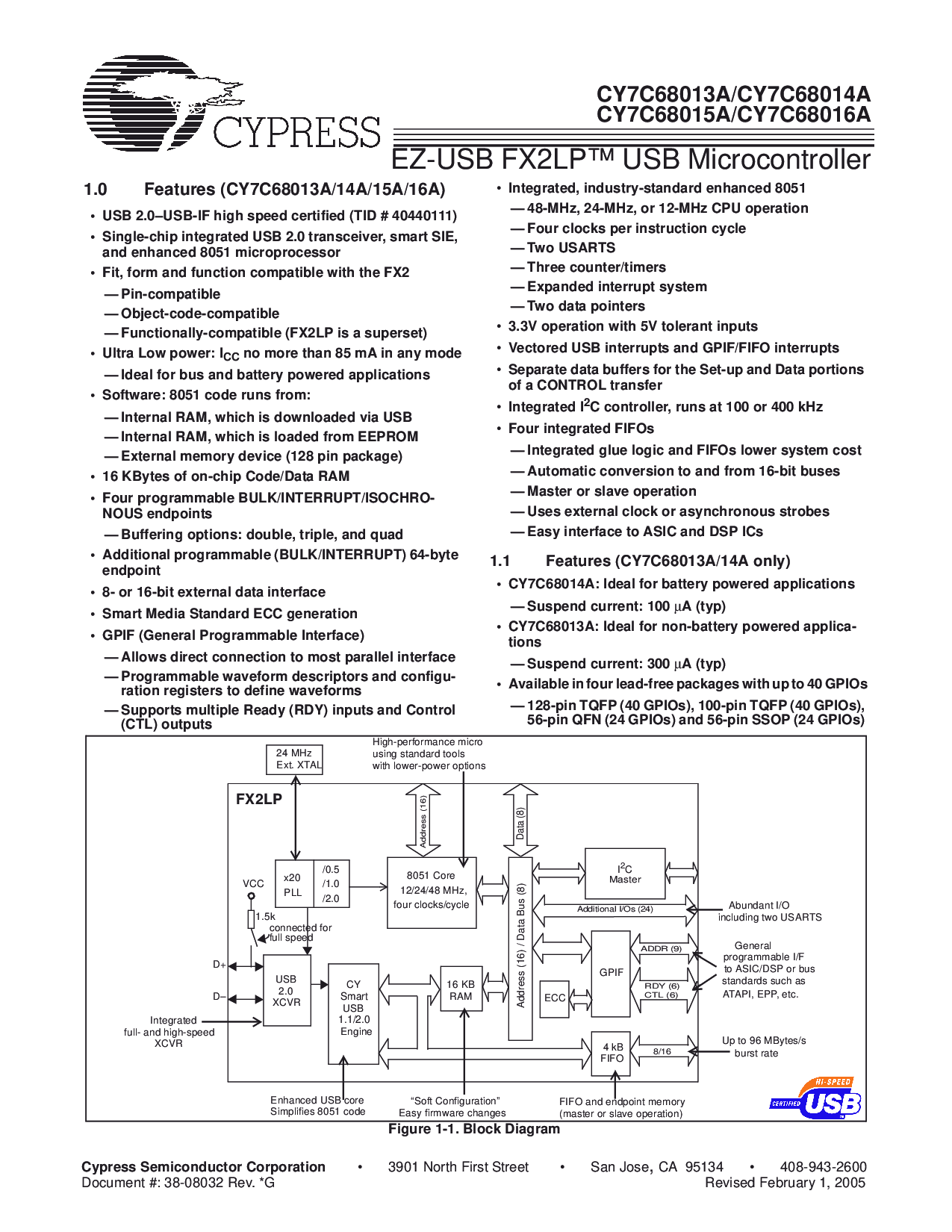

地址 (16)

x20

PLL

/0.5

/1.0

/2.0

8051 核心

12/24/48 mhz,

四 clocks/循环

I

2

C

VCC

1.5k

D+

D–

地址 (16) / 数据 总线 (8)

FX2LP

GPIF

CY

Smart

USB

1.1/2.0

Engine

USB

2.0

XCVR

16 kb

内存

4 kb

先进先出

整体的

全部- 和 高-速

XCVR

额外的 i/os (24)

地址 (9)

ctl (6)

rdy (6)

8/16

数据 (8)

24 mhz

ext. xtal

增强 usb 核心

使简化 8051 代号

“soft configuration”

容易 firmware 改变

先进先出 和 endpoint 记忆

(主控 或者 从动装置 运作)

向上 至 96 mbytes/s

burst 比率

一般

可编程序的 i/f

至 asic/dsp 或者 总线

standards 此类 作

atapi, epp, 等

abundant i/o

包含 二 usarts

高-效能 微观的

使用 标准 tools

和 更小的-电源 选项

主控

图示 1-1. 块 图解

连接 为

全部 速

ECC