ds90c363a/ds90cf363a

+3.3v 可编程序的 LVDS 传输者 18-位 Flat 嵌板

显示 (fpd) link-65 MHz

+3.3v LVDS 传输者 18-位 Flat 嵌板 显示 (fpd)

link-65 MHz

一般 描述

这 ds90c363a/ds90cf363a 传输者 converts 21 位

的 cmos/ttl 数据 在 三 LVDS (低 电压 差别的

signaling) 数据 streams. 一个 阶段-锁 transmit 时钟 是

transmitted 在 并行的 和 这 数据 streams 在 一个 fourth

LVDS link. 每 循环 的 这 transmit 时钟 21 位 的 输入

数据 是 抽样 和 transmitted. 在 一个 transmit 时钟 fre-

quency 的 65 mhz, 18 位 的 RGB 数据 和 3 位 的 LCD

定时 和 控制 数据 (fpline, fpframe, drdy) 是

transmitted 在 一个 比率 的 455 Mbps 每 LVDS 数据 频道.

使用 一个 65 MHz 时钟, 这 数据 throughput 是 170 mbytes/

秒. 这 DS90C363A 传输者 能 是 编写程序 为

Rising 边缘 strobe 或者 下落 边缘 strobe 通过 一个 dedi-

cated 管脚. 这 DS90CF363A 是 fixed 作 一个 下落 边缘

strobe 传输者. 一个 Rising 边缘 或者 下落 边缘 strobe

传输者 将 interoperate 和 一个 下落 边缘 strobe re-

ceiver (ds90cf364) 没有 任何 转变 逻辑.

这个 chipset 是 一个 完美的 意思 至 solve EMI 和 缆索 大小

问题 有关联的 和 宽, 高 速 TTL 接口.

特性

n

20 至 65 MHz 变换 时钟 支持

n

Rejects

>

±

3ns Jitter 从 VGA 碎片 和 较少 比

225ps 输出 Jitter

@

65MHz (tjcc)

n

Best–in–Class 设置 &放大; 支撑 时间 在 TxINPUTs

n

Tx 电源 消耗量

<

130 mW (典型值)

@

65MHz

Grayscale

n

>

50

%

较少 电源 消耗 比 BiCMOS

Alternatives

n

Tx 电源-向下 模式

<

200µW (最大值)

n

静电释放 比率

>

7 kV (hbm),

>

500V (eiaj)

n

支持 vga, svga, XGA 和 双 Pixel sxga.

n

Narrow 总线 减少 缆索 大小 和 费用

n

向上 至 1.3 Gbps throughput

n

向上 至 170 megabytes/秒 带宽

n

345 mV (典型值) 摆动 LVDS 设备 为 低 EMI

n

PLL 需要 非 外部 组件

n

兼容 和 tia/eia-644 LVDS 标准

n

低 profile 48-含铅的 TSSOP 包装

n

改进 替换 为:

SN75LVDS85 — DS90C363A

SN75LVDS84 — DS90CF363A

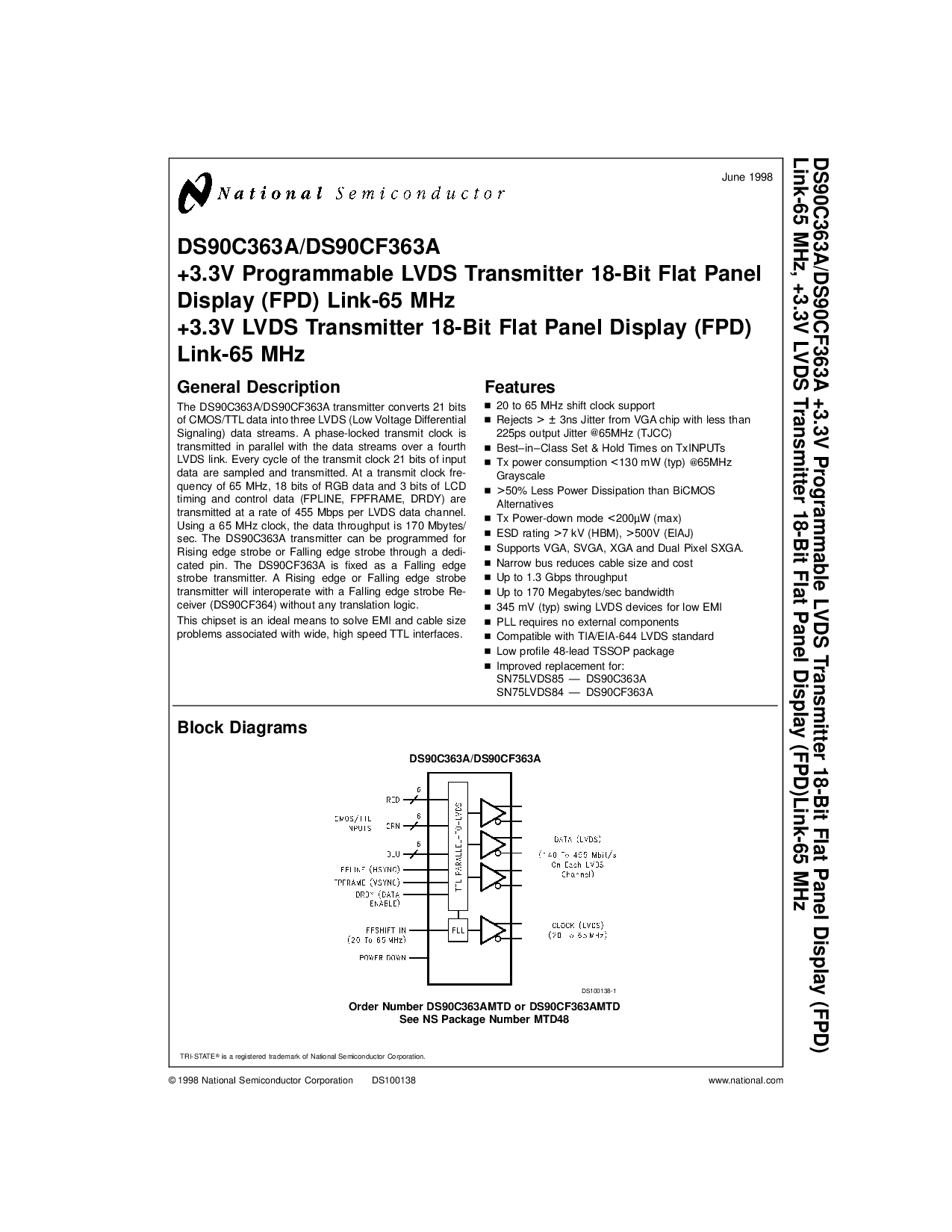

块 图解

触发-状态

®

是 一个 注册 商标 的 国家的 半导体 公司.

ds90c363a/ds90cf363a

ds100138-1

顺序 号码 DS90C363AMTD 或者 DS90CF363AMTD

看 NS 包装 号码 MTD48

六月 1998

ds90c363a/ds90cf363a +3.3v 可编程序的 LVDS 传输者 18-位 Flat 嵌板 显示 (fpd)

link-65 mhz, +3.3v LVDS 传输者 18-位 Flat 嵌板 显示 (fpd)link-65 MHz

© 1998 国家的 半导体 公司 DS100138 www.国家的.com