73M2910L

微控制器

april 2000

描述

这 73m2910l 高 效能 微观的-控制 是

为基础 在 这 工业 标准 8-位 8032

执行 在 一个 先进的 submicron cmos

处理. 这 处理器 有 这 attributes 的 这

8032, 包含 操作指南 循环 时间, uart, 计时器,

中断, 256 字节 的 在-碎片 内存 和

可编程序的 i/o. 这 architecture 有 被

优化 为 低 电源 可携带的 modem 或者

交流 产品 用 integrating 唯一的

特性 和 这 核心 cpu.

一个 关键 特性 是 一个 用户 friendly hdlc packetizer,

accessed 通过 这 特定的 函数 寄存器. 它

有 一个 串行 i/o, 硬件 支持 为 16 和 32-位

crc, 零 insert/delete 控制, 一个 专心致志的 中断

和 一个 clear 频道 模式 为 用-passing 这

packetizer.

其它 特性 包含 额外的 用户 可编程序的

i/o 和 可编程序的 bank 选择 和 碎片 选择

逻辑, 设计 至 eliminate 板 水平的 glue 逻辑. 它

也 包含 二 一般-目的 输入 端口 和

可编程序的 wakeup 能力.

为 设备 那 需要 非-多路复用 地址

和 数据 buses, 第八 latched 输出 为 这 低

字节 的 这 地址 是 有.

(持续)

特性

•

8032 兼容 操作指南 设置

•

44 mhz 运作 从 3.3 至 5.5v

•

hdlc 支持 逻辑 (packetizer, 16 和 32

crc, 零 id)

•

24 管脚 为 用户 可编程序的 i/o 端口

•

8 管脚 可编程序的 碎片 选择 逻辑 或者 i/o

为 记忆 编排 附带的 eliminating

glue 逻辑

•

3 外部 中断 来源 (可编程序的

极性)

•

16 专心致志的 latched 地址 管脚

•

多路复用 数据/地址 总线

•

操作指南 循环 时间 完全同样的 至 8032

•

缓冲 振荡器 (或者 osc/2) 输出 管脚

•

1.8432 mhz uart 时钟 有

•

bank 选择 电路系统 至 支持 向上 至 128k 的

外部 程序 记忆

•

也 有 在 100-含铅的 qfp 和 100-管脚

pga 包装

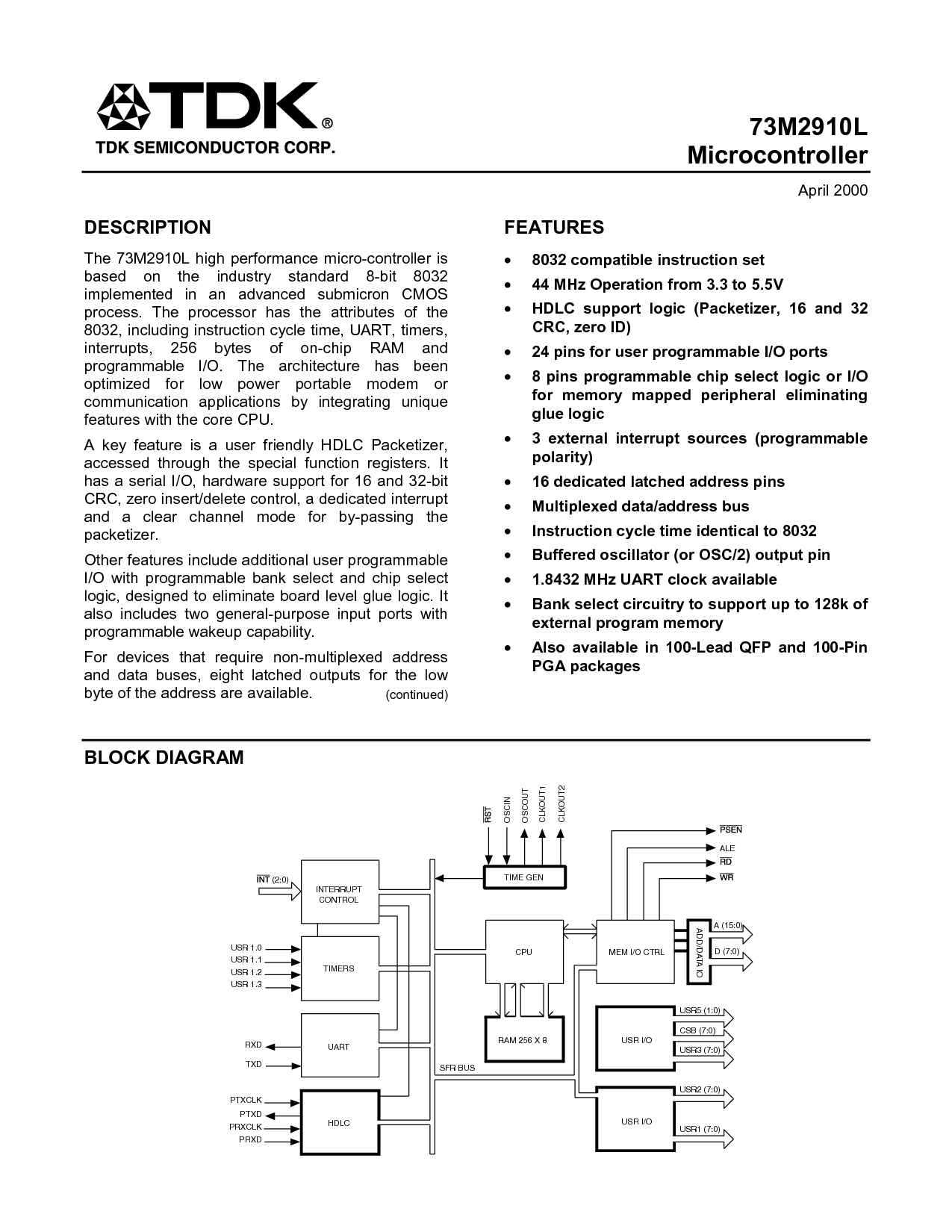

块 图解

(2:0)

usr 1.0

usr 1.1

usr 1.2

usr 1.3

RXD

TXD

PTXCLK

PTXD

PRXCLK

PRXD

OSCIN

OSCOUT

CLKOUT1

CLKOUT2

ALE

一个 (15:0)

d (7:0)

usr5 (1:0)

csb (7:0)

usr3 (7:0)

usr2 (7:0)

usr1 (7:0)

sfr 总线

时间 gen

CPU mem i/o ctrl

usr i/o

usr i/o

内存 256 x 8

HDLC

UART

计时器

中断

控制

增加/数据 io