© 2001 仙童 半导体 公司 DS012424 www.fairchildsemi.com

六月 1998

修订 二月 2001

74lcx112 低 电压 双 j-k 负的 边缘-triggered flip-flop 和 5v tolerant 输入

74LCX112

低 电压 双 j-k 负的 边缘-triggered flip-flop

和 5v tolerant 输入

一般 描述

这 lcx112 是 一个 双 j-k flip-flop. 各自 flip-flop 有 inde-

pendent j, k, preset, clear, 和 时钟 输入 和 q,

Q

输出. 这些 设备 是 边缘 敏感的 和 改变

状态 在 这 负的 going 转变 的 这 时钟 脉冲波.

clear 和 preset 是 独立 的 这 时钟 和 accom-

plished 用 一个 低 逻辑 水平的 在 这 相应的 输入.

lcx 设备 是 设计 为 低 电压 (3.3v 或者 2.5)

运作 和 这 增加 能力 的 接合 至 一个 5v

信号 环境.

这 74lcx112 是 fabricated 和 先进的 cmos technol-

ogy 至 达到 高 速 运作 当 维持

cmos 低 电源 消耗.

特性

■

5v tolerant 输入

■

2.3v–3.6v v

CC

规格 提供

■

7.5 ns t

PD

最大值 (v

CC

=

3.3v), 10

µ

一个 i

CC

最大值

■

电源 向下 高 阻抗 输入 和 输出

■

±

24 毫安 输出 驱动 (v

CC

=

3.0v)

■

实现 专利的 噪音/emi 减少 电路系统

■

获得-向上 效能 超过 500 毫安

■

静电释放 效能:

人 身体 模型

>

2000V

机器 模型

>

2000V

订货 代号:

设备 也 有 在 录音带 和 卷轴. 具体说明 用 appending 后缀 letter

“

X

”

至 这 订货 代号.

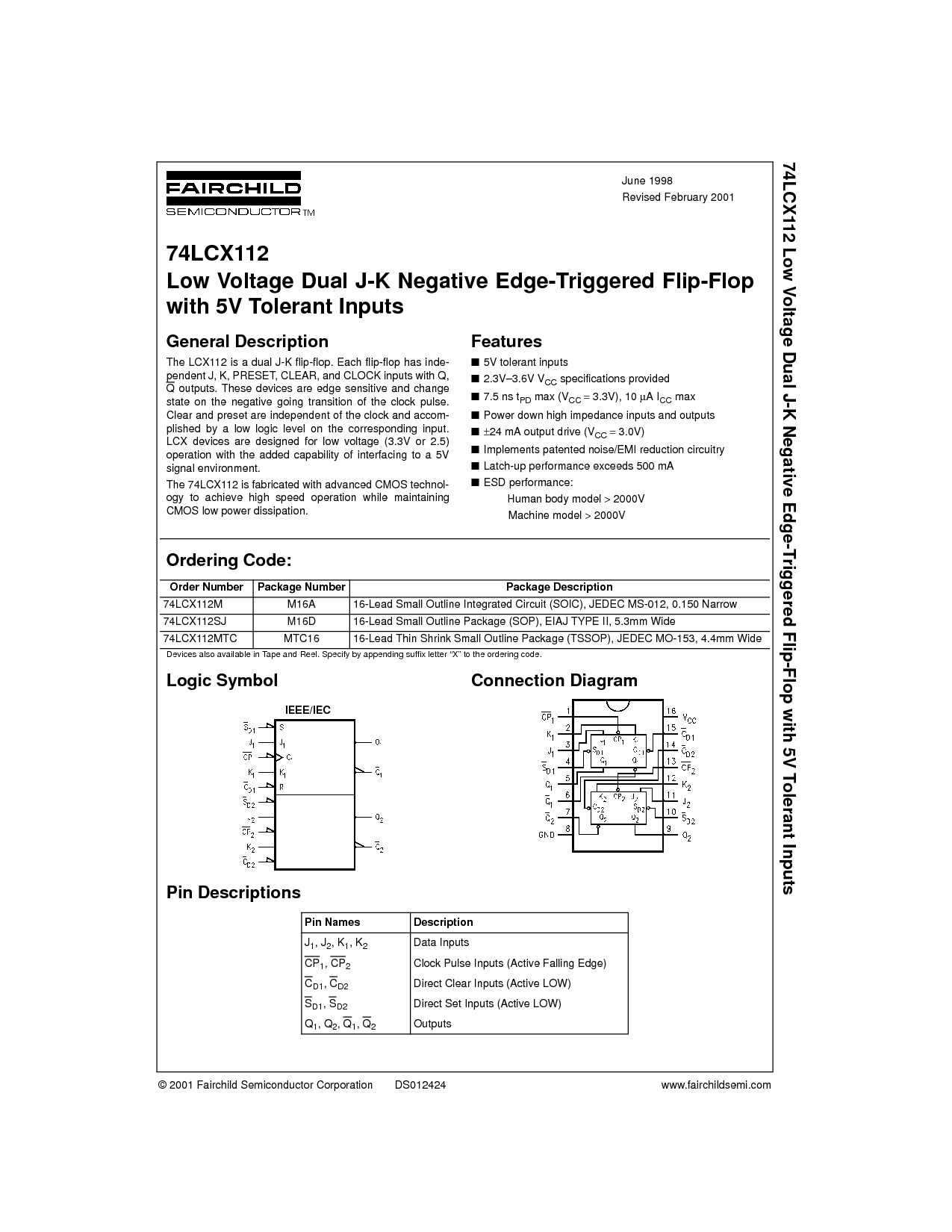

逻辑 标识

ieee/iec

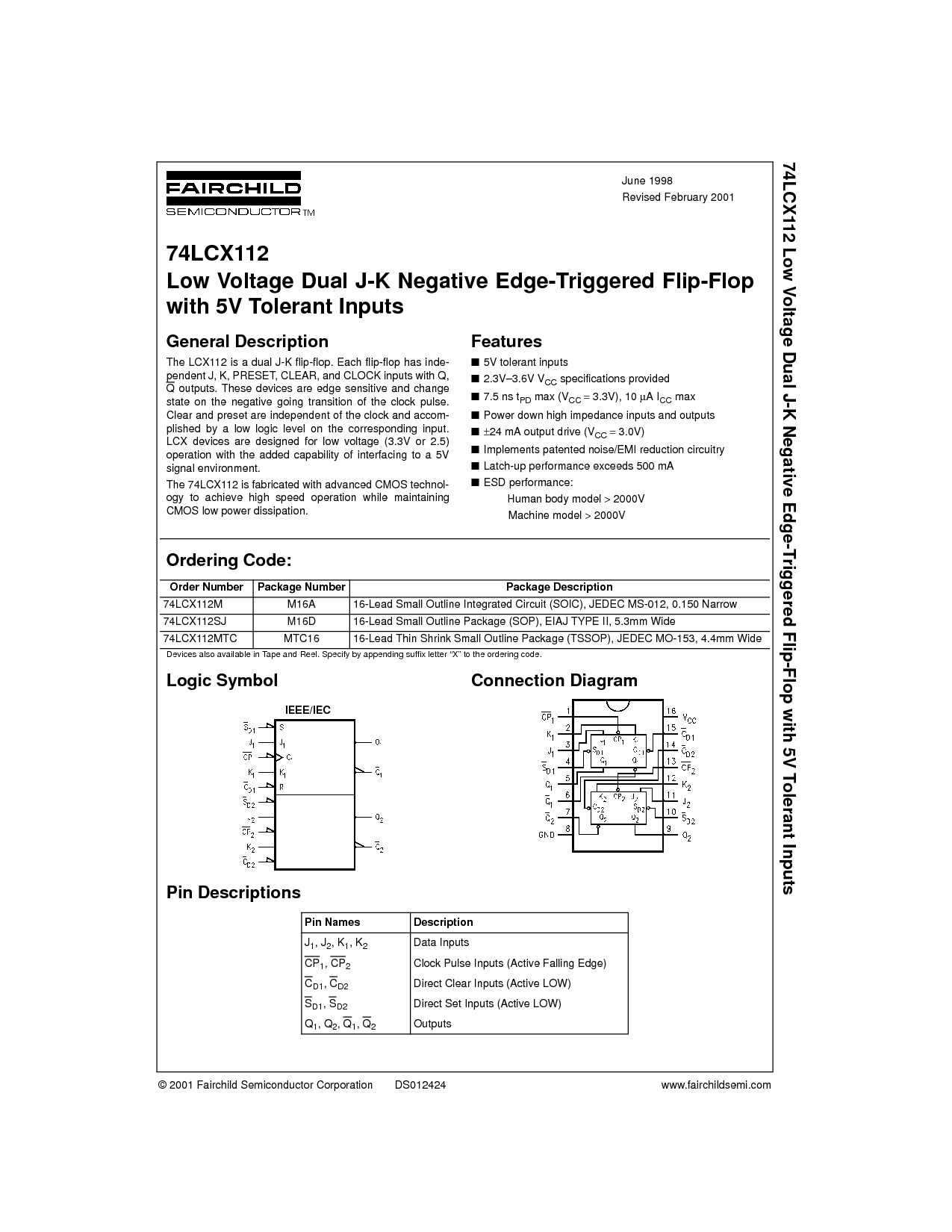

连接 图解

管脚 描述

顺序 号码 包装 号码 包装 描述

74LCX112M M16A 16-含铅的 小 外形 整体的 电路 (soic), 电子元件工业联合会 ms-012, 0.150 narrow

74LCX112SJ M16D 16-含铅的 小 外形 包装 (sop), eiaj 类型 ii, 5.3mm 宽

74LCX112MTC MTC16 16-含铅的 薄的 shrink 小 外形 包装 (tssop), 电子元件工业联合会 mo-153, 4.4mm 宽

管脚 names 描述

J

1

, j

2

, k

1

, k

2

数据 输入

CP

1

, cp

2

时钟 脉冲波 输入 (起作用的 下落 边缘)

C

D1

, c

D2

直接 clear 输入 (起作用的 低)

S

D1

, s

D2

直接 设置 输入 (起作用的 低)

Q

1

, q

2

, q

1

, q

2

输出