altera 公司 7

初步的 信息 cyclone fpga 家族 数据 薄板

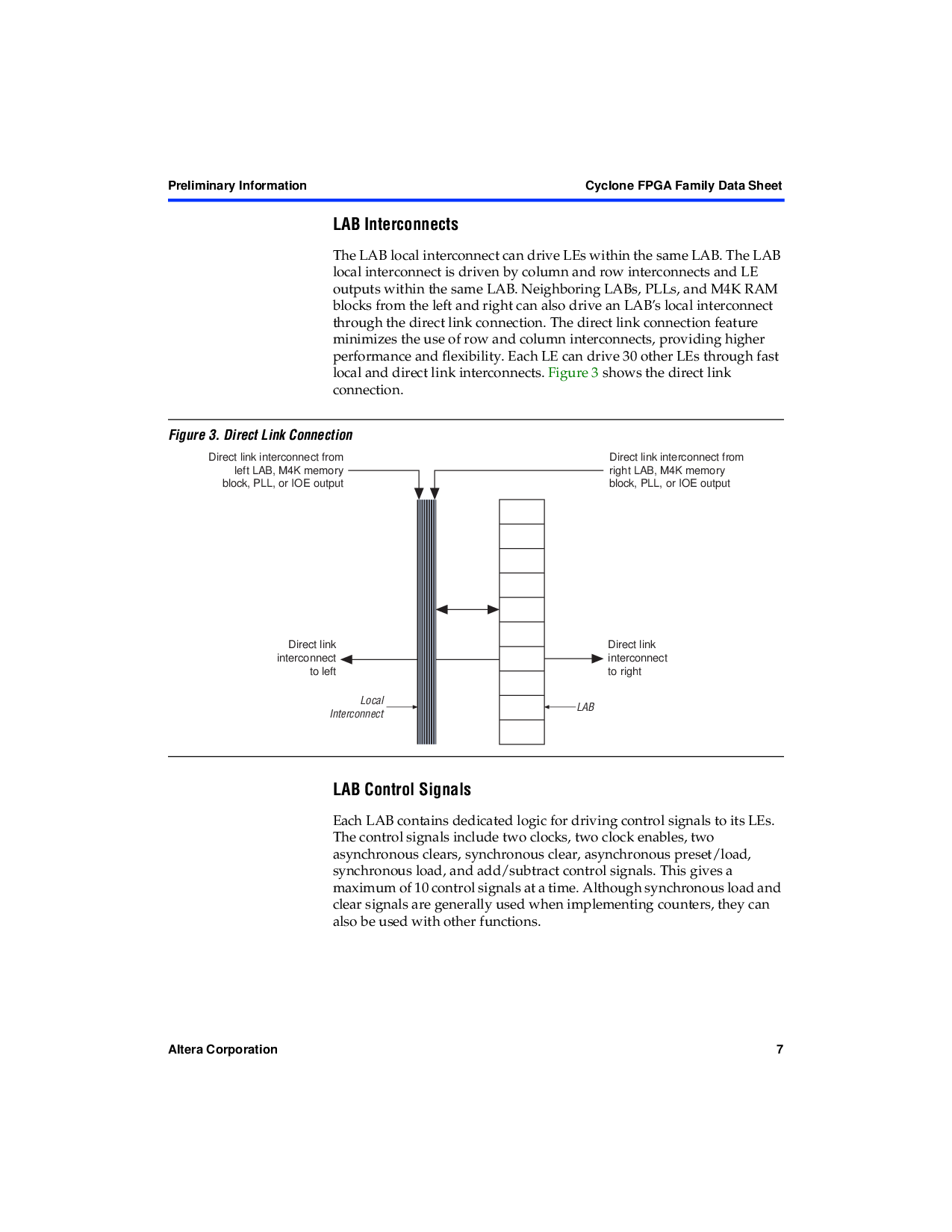

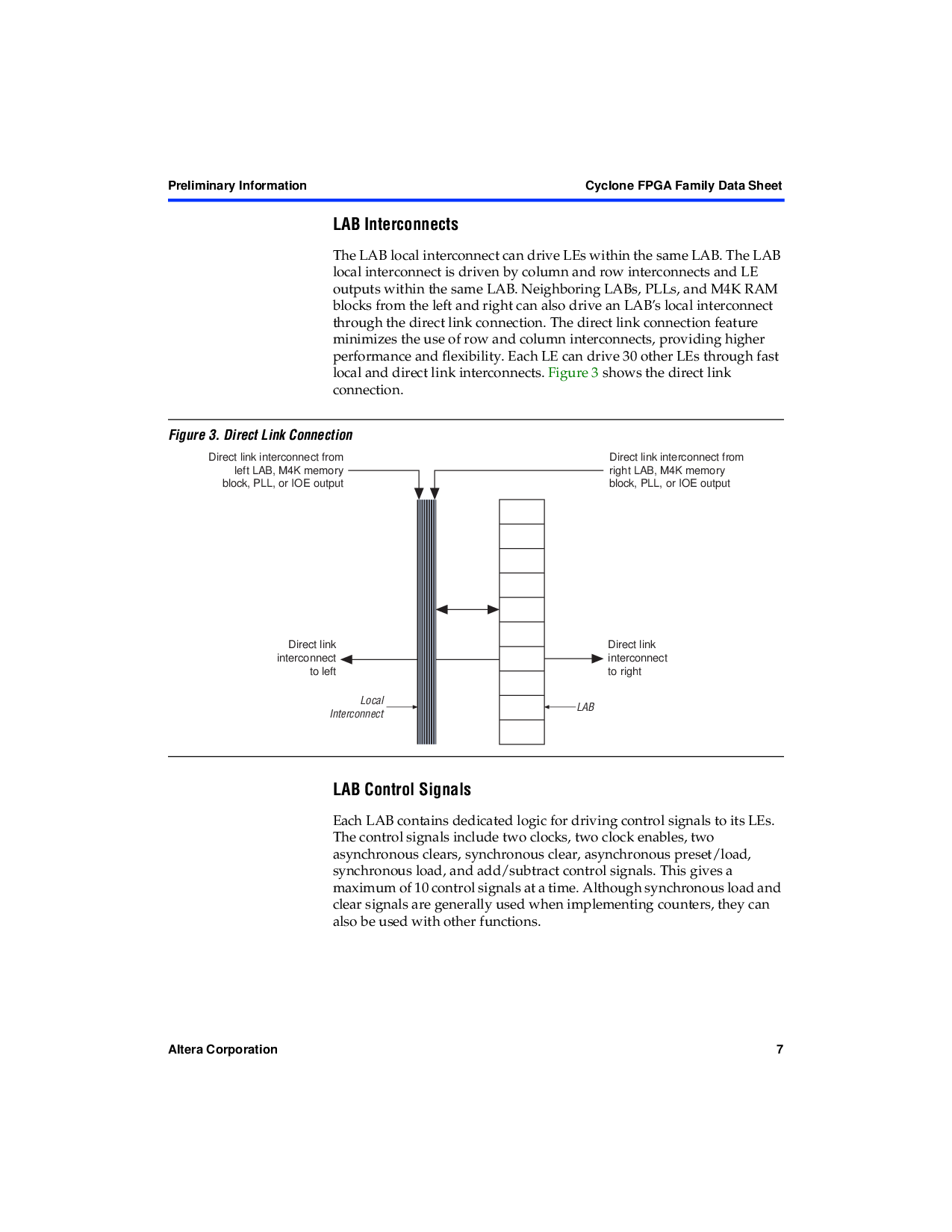

lab interconnects

这 lab local interconnect 能 驱动 les 在里面 这 一样 lab. 这 lab

local interconnect 是 驱动 用 column 和 行 interconnects 和 le

输出 在里面 这 一样 lab. neighboring labs, plls, 和 m4k 内存

blocks 从 这 left 和 正确的 能 也 驱动 一个 lab’s local interconnect

通过 这 直接 link 连接. 这 直接 link 连接 特性

降低 这 使用 的 行 和 column interconnects, 供应 高等级的

效能 和 flexibility. 各自 le 能 驱动 30 其它 les 通过 快

local 和 直接 link interconnects.图示 3显示 这 直接 link

连接.

图示 3. 直接 link 连接

lab 控制 信号

各自 lab 包含 专心致志的 逻辑 为 驱动 控制 信号 至 它的 les.

这 控制 信号 包含 二 clocks, 二 时钟 使能, 二

异步的 clears, 同步的 clear, 异步的 preset/加载,

同步的 加载, 和 增加/减去 控制 信号. 这个 给 一个

最大 的 10 控制 信号 在 一个 时间. 虽然 同步的 加载 和

clear 信号 是 一般地 使用 当 implementing counters, 它们 能

也 是 使用 和 其它 功能.

LAB

直接 link

interconnect

至 正确的

直接 link interconnect 从

正确的 lab, m4k 记忆

块, pll, 或者 ioe 输出

直接 link interconnect 从

left lab, m4k 记忆

块, pll, 或者 ioe 输出

Local

Interconnect

直接 link

interconnect

至 left